Cборник_ЛР

.pdf

на выход n-канального МДП транзистора с искажением (потерей амплитуды сигнала). Рассмотрим теперь ситуацию, когда Uвх = U0 ≈ 0 B. Так как = U1

транзистор открыт и проводит ток в инверсном включении, справа налево, по рис.6.1,a. Конденсатор Сн разряжается до значения Uвых = 0, то есть логиче-

ский ноль передается n-канальным МДП транзистором со входа на выход без искажений.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвых |

|

|||||||||||||||||||

Uвх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвых |

|

|

Uвх |

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сн |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сн |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

Uвх |

Uвых |

Uвх |

Uвых |

|

|

Сн |

|

|

|

|

|

|

|

|

|

в |

г |

|

|

|

|

|

|

|

|

|

|

д |

е |

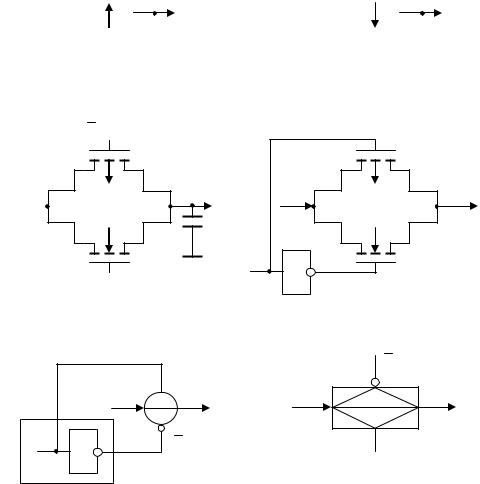

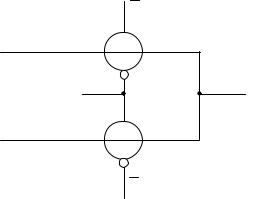

Рис.6.1. Схема и обозначения проходного ключа: а, б - составные части ПК; в - схема ПК; г - схема подключения тактовых импульсов;

д, е - обозначения ПК

113

На рис.6.1,б изображен р-канальный МДП транзистор в таком же включе-

нии, но управляемый инверсным сигналом . Рассуждая аналогично, имеем при = U1 ( = U0) закрытый транзистор независимо от входного сигнала.

Условие отпирания р-канального транзистора можно представить в виде

UЗИ Uвых Uпор p , где Uпор p 0.

Если = U0 ≈ 0 В, то транзистор будет открыт, пока Uвых > –Unop p. Это условие выполняется при передаче со входа на выход логической единицы U1

(U1 > Unop p ). Однако, при передаче на выход логического нуля конденсатор

Сн сможет разрядиться через транзистор только до напряжения Uвых = Unop p ,

так как при достижении такого выходного напряжения транзистор закроется.

Следовательно, р-канальный МДП транзистор передает со входа на выход

логическую единицу без |

искажений, а логический ноль - с искажением |

||||

(табл.1). |

|

|

|

|

|

|

|

|

|

Таблица 6.1 |

|

Передача логических уровней транзисторами разных типов |

|||||

|

|

|

|

|

|

|

|

|

Передача логических уровней |

|

|

|

Транзистор |

|

|

|

|

|

|

“0” |

“1” |

|

|

|

|

|

|

|

|

|

n-МДП |

|

без искажения |

с искажением |

|

|

p-МДП |

|

с искажением |

без искажения |

|

|

|

|

|

|

|

Включая параллельно n- и р-канальные МДП транзисторы (объединяя их свойства), получим схему с идеальной передачей амплитуды логических сиг-

налов со входа на выход под воздействием управляющих сигналов (рис.6.1,в).

Заметим, что эти транзисторы управляются парафазными импульсами и

(рис.6.1,г). Такую КМДП-схему часто называют проходным ключом, ПК

(transmission gate). В зарубежной литературе используются также два услов-

ных обозначения ПК, которые показаны на рис.6.1,д,е.

114

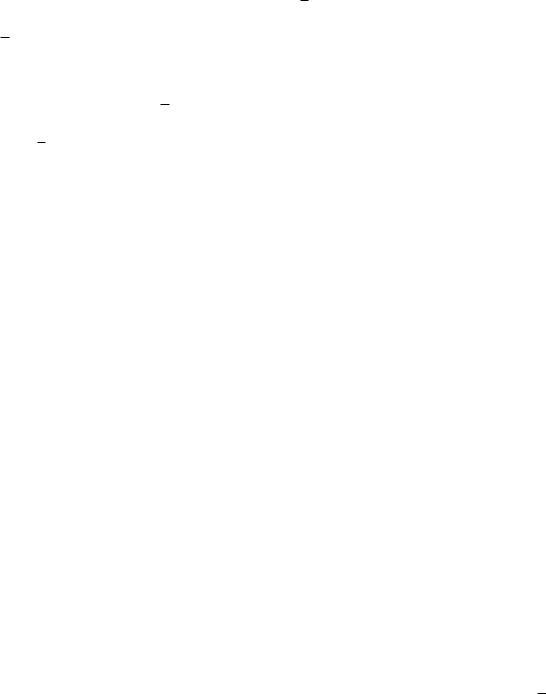

Итак, если = “0”, оба транзистора закрыты независимо от значения входного сигнала. Если же = “1”, оба транзистора открываются и пропуска-

ют входной сигнал на выход (логический ноль и логическую единицу). При этом сопротивление ПК слабо зависит от величины входного сигнала

(рис.6.2). Ток в открытом ПК может протекать в любом направлении. Сопро-

тивление между входом и выходом в открытом состоянии ключа достаточно сильно зависит от температуры подложки (причем с ростом температуры со-

противление растет (рис.6.3)), а также разности потенциалов между: входом

(истоком или стоком) и подложкой; затвором и подложкой.

R |

R(p-МДП) R(n-МДП) |

|

|

U |

|

U1 – U |

пор n |

U1 U |

вх |

|

пор p |

|

|

Рис.6.2. Зависимость сопротивления ПК от входного сигнала

В технологии КМДП схем с р-карманом чувствительность n-канального транзистора к изменению смещения подложки обычно выше, чем р-канально-

го. Для снижения этого влияния на сопротивление n-МДП можно использо-

вать схему, изображенную на рис.6.4. В этой схеме потенциал подложки из-

меняется от величины входного потенциала до напряжения 0 В.

Передающий ключ иногда называют аналоговым ключом из-за его спо-

собности пропускать или блокировать аналоговые сигналы. ПК - один из важ-

115

ных элементов цифровых синхронных КМДП схем. С его помощью можно |

|

упростить логические схемы, их топологию, уменьшить площадь кристалла |

|

по сравнению с традиционными вариантами воплощения, реализовать “Мон- |

|

тажные И или ИЛИ узлы”. Наиболее эффективно эти преимущества реализу- |

|

ются для мультиплексирования и хранения информации. |

|

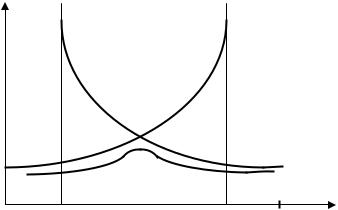

RПК |

T = 125o |

|

T = 25o |

|

T = 55o |

|

Uвх |

Рис.6.3. Температурная зависимость сопротивления ПК |

|

Uвх |

UИП |

|

|

|

|

|

UИП |

Рис.6.4. Схема управления смещением подложки |

|

116

Важной особенностью ПК является управление парафазными тактовыми импульсами (ТИ), получаемыми, например, с помощью простого инвертора.

Однако такое решение в некоторых случаях может привести к опасности лож-

ного срабатывания. Действительно, задержка между прямым и инверсным тактовыми импульсами приводит к искажению передающих свойств ключа.

Поэтому для правильной работы схемы время фронта и среза ТИ должны быть минимальными.

Дополнительные меры предосторожности следует использовать при объе-

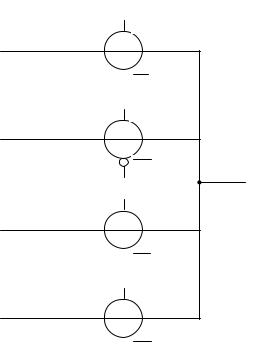

динении выходов двух ПК (рис.6.5), управляемых сигналами противополож-

ной полярности. Небольшое несовпадение тактовых импульсов может привес-

ти, например, к одновременному открытию обоих ПК и появлению неопреде-

ленного (метастабильного) состояния на выходе.

Вход A

|

Выход |

Вход B

Рис.6.5. Схема объединения выходов ПК

Цифровые схемы с использованием проходных ключей

ПК позволяет существенно уменьшить число элементов при построении мультиплексора. Любое число сигналов можно переключить (мультиплекси-

ровать) на общую выходную шину с использованием одного ПК на каждый

117

вход (рис.6.6). В традиционной МДП технике (рис.6.7) для этих же целей тре-

буется в два раза больше транзисторов. При одинаковых размерах транзисто-

ров вторая схема имеет меньшее быстродействие, поскольку в ней использу-

ется последовательное соединение транзисторов.

1

A

1

1

2

B

2 |

Выход |

3

C

3

3

4

D

4

4

Рис.6.6. Мультиплексор на основе ПК

Кроме того, к преимуществам мультиплексора на ПК следует отнести бо-

лее простую систему разводки межсоединений. С другой стороны, в таком мультиплексоре возможна ситуация, когда все сигналы завершаются одно-

временно, тогда напряжение на выходе схемы будут “плавать” в промежутке между 0 В и UИП (метастабильное состояние), что может привести к ложному срабатыванию последующих схем.

С помощью ПК можно уменьшить число транзисторов и в такой распро-

страненной схеме, как “исключающее ИЛИ”. Один из вариантов приведен на рис.6.8.

118

|

|

|

UИП |

|

A |

B |

C |

D |

|

1 |

2 |

3 |

4 |

Выход |

|

A |

|

|

1 |

|

B |

|

|

2 |

|

C |

|

|

3 |

|

D |

|

|

4 |

Рис.6.7. Традиционная схема мультиплексора

UИП

A |

B |

AB+AB

Рис.6.8. Схема “исключающее ИЛИ” с использованием ПК

В регистрах сдвига, счетчиках очень часто используют D-триггеры (на-

звание происходит от слова delay - задержка). Этот триггер имеет один вход D

и два выхода - прямой Q и инверсный Q (иногда нужен только один выход).

119

Функциональная особенность этого типа триггера состоит в том, что сигнал на выходе Q в такте (п + 1) повторяет значение входного сигнала D в преды-

дущем такте (п) и сохраняет (запоминает) это состояние до следующего такта.

Другими словами, D-триггер задерживает на один такт информацию, сущест-

вовавшую на входе D. Иногда этот триггер называют “защелкой”.

Закон функционирования D-триггера прост:

Qn 1 Dn

Таблица состояний в подробной и минимизированной формах представ-

лены в табл.6.2 и 6.3 (здесь С - тактовый сигнал).

Таблица 6.2

Таблица состояний D-триггера

|

Такт n |

|

Такт n+1 |

|

|

|

|

C |

Dn |

Qn |

Qn+1 |

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

Таблица 6.3

Сокращенная таблица состояний

|

Такт n |

Такт n+1 |

|

|

|

|

|

|

Dn |

Qn+1 |

|

|

|

|

|

|

0 |

0 |

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

120

D |

|

|

|

|

|

|

|

|

|

& |

|

|

& |

|

Q |

||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D T

C

& |

& |

|

|

||

Q |

|||||

|

|

|

|||

C

а |

б |

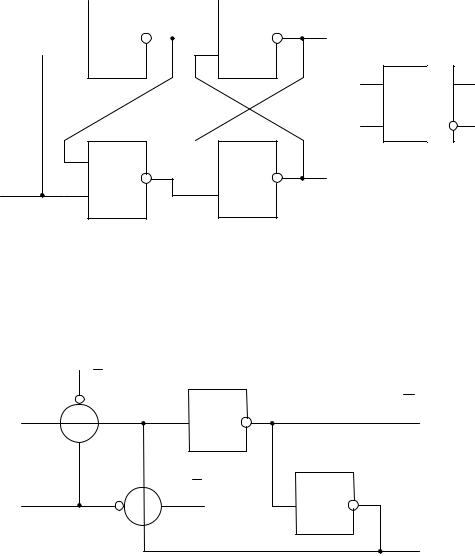

Рис.6.9. D-триггер в традиционном исполнении:

а - схема, б - обозначение

|

C |

|

D |

1 |

Q |

C |

C |

1 |

|

Q

Рис.6.10. D-триггер с использованием ПК

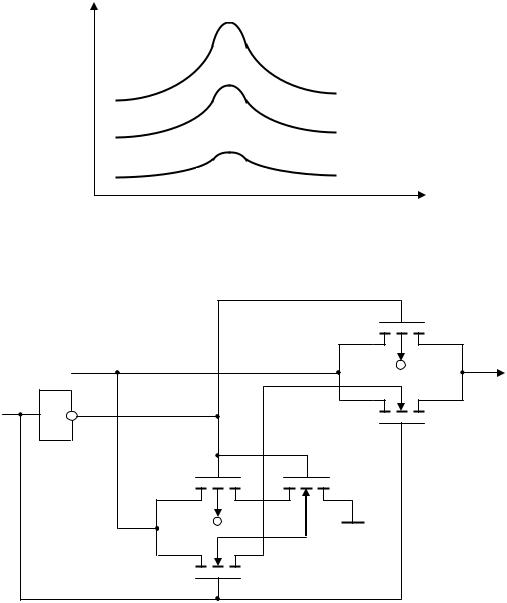

Смена состояний триггера происходит под действием тактового импульса

С = 1, поэтому все реальные D-триггеры - тактируемые (синхронные). Управ-

ление по тактовому входу может быть статическим, динамическим, а также двухступенчатым. Схема D-триггера в традиционном исполнении и его ус-

ловное обозначение представлены на рис.6.9. В два раза меньше КМДП-тран-

зисторов требуется для построения D-триггера с использованием ПК

(рис.6.10). Он состоит из пары инверторов и пары ПК. Когда ТИ имеет высо-

121

кий логический уровень, данные поступают на открытый ключ, на выходе Q

через инверторы появляется входной сигнал. Когда ТИ переходит в низкое со-

стояние, цепь инверторов закрывается, а через цепь обратной связи на выходе

Q фиксируется стабильное состояние.

На основе такого D-триггера можно построить цепочку защелок

(рис.6.11,a), которая в зависимости от значения управляющего сигнала разби-

вается на отдельные звенья (рис.6.11,6,в). D-триггеры строят также по двух-

ступенчатой схеме (master-slave). На рисунках 6.12 - 6.14 приведены электри-

ческие схемы таких защелок, причем во втором случае - с дополнительным сигналом очистки СLR, а в последнем варианте - с установкой S и сбросом R.

Двухступенчатый D-триггер (рис.6.13) срабатывает по фронту (положитель-

ному перепаду от “0” до “1”) тактового импульса. По срeзу ТИ данные посту-

пают в первую ступень (master), но блокированы от второй ступени. По фрон-

ту ТИ информация передается от первой ступени на вторую и на выходы Q и

Q . Недостатком схемы с использованием ПК является то, что выход Q всегда содержит на один вентиль больше, чем Q, и имеет большее время задержки.

122