Cборник_ЛР

.pdf

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

C |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

C |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|||||||||||

1 |

1 |

1 |

C |

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

а |

|

|

|

|

|

|

|

C |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

C=1 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

1 |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б

1 |

|

1 |

|

|

|

C=0

в

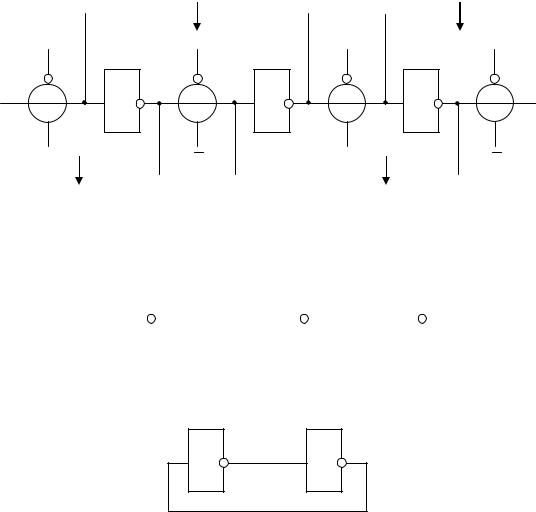

Рис.6.11. Цепочка защелок на основе D-триггеров: а - общая схема,

б - состояние схемы при С = 1, в - состояние схемы при С = 0

123

D |

C |

|

1 |

|

C |

1 |

Q |

|

|

|

|

||||

|

|

|

C |

|

|

C |

|

C |

|

|

1 |

C |

|

|

1 |

|

|

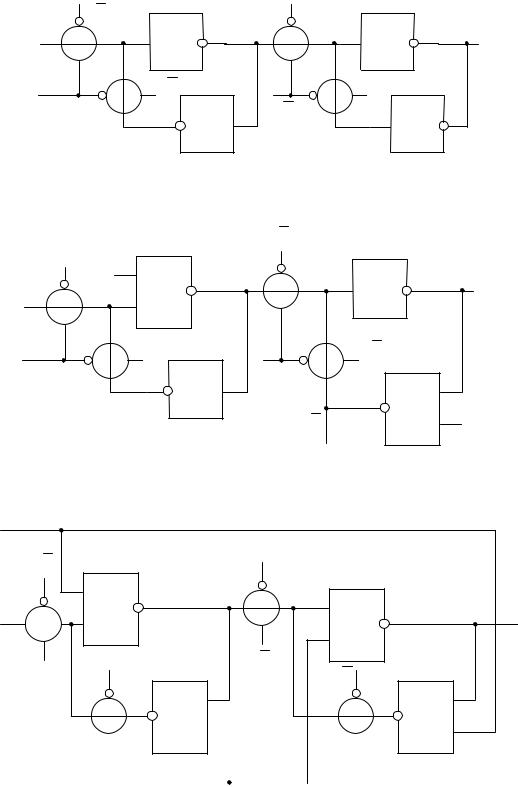

Рис.6.12. Схема двухступенчатого D-триггера |

|||||

|

|

|

|

C |

|

|

|

C |

CLR |

& |

|

|

1 |

|

|

|

|

|

|

|

Q |

||

D |

|

|

|

|

|

|

|

|

|

|

C |

|

|

C |

|

C |

|

|

1 |

C |

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

CLR |

|

|

|

|

|

|

|

|

Рис.6.13. Схема D-триггера с дополнительным входом |

|||||||

S |

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

|

D |

|

|

|

|

|

Q |

|

|

C |

|

|

C |

|

|

|

C |

|

|

|

|

C |

|

|

|

|

|

1 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

R |

C |

|

||||||

|

|

|

|

|

|

|

|

|

Рис.6.14. Схема D-триггера с установкой и сбросом

124

Домашнее задание

1.Изучить теоретические разделы лабораторной работы.

2.Выбрать вариант задания для расчета из табл.6.4. Номер варианта соот-

ветствует порядковому номеру студента по списку группы.

3. Провести анализ схемы с использованием программы Orcad.. При зада-

нии параметров моделей МДП-транзисторов рекомендуется использовать следующие значения: Uпop n = 1 B, Uпop p = –1 B, dок = 25 нм; k0п = 1/2Суд n, k0р = 1/2Суд р, где Суд = ( 0 ок)/dok = 0,03мкФ/см2 ; γ = 0,8; λ = 0,1.

Выбор геометрических размеров транзисторов осуществляется, исходя из условия kn ≈ kp. Полагая Ln = Lp = Lmin (Lmin = 2мкм), получаем Wn/Wp ≈ p/ n.

Оценить отношение p/ n можно по графикам, приведенным на рис.6.15.

|

|

|

|

|

|

Таблица 6.4 |

|

|

|

Варианты индивидуальных заданий |

|

|

|||

|

|

|

|

|

|

|

|

|

Номер |

Номер |

Вид |

Номер |

Номер |

Вид |

|

|

варианта |

рисунка |

расчета |

варианта |

рисунка |

расчета |

|

|

|

|

|

|

|

|

|

|

1 |

4 |

1 |

13 |

10 |

1 |

|

|

|

|

|

|

|

|

|

|

2 |

4 |

2 |

14 |

10 |

2 |

|

|

|

|

|

|

|

|

|

|

3 |

4 |

3 |

15 |

10 |

3 |

|

|

|

|

|

|

|

|

|

|

4 |

5 |

1 |

16 |

11.а |

1 |

|

|

|

|

|

|

|

|

|

|

5 |

5 |

2 |

17 |

11.а |

2 |

|

|

|

|

|

|

|

|

|

|

6 |

5 |

3 |

18 |

11.а |

3 |

|

|

|

|

|

|

|

|

|

|

7 |

6 |

1 |

19 |

12 |

4 |

|

|

|

|

|

|

|

|

|

|

8 |

6 |

2 |

20 |

13 |

4 |

|

|

|

|

|

|

|

|

|

|

9 |

6 |

3 |

21 |

14 |

4 |

|

|

|

|

|

|

|

|

|

|

10 |

8 |

1 |

22 |

12 |

3 |

|

|

|

|

|

|

|

|

|

|

11 |

8 |

2 |

23 |

13 |

3 |

|

|

|

|

|

|

|

|

|

|

12 |

8 |

3 |

24 |

14 |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

125

n,

см2/Вс

500

|

|

|

|

|

1 |

|

|

|

|

450 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

2 |

||

|

|

|

|

|

|

|

|

|

|

400 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

350 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

2 |

3 |

4 |

5 |

|

|

L,мкм |

|

|

|

|

|

|

|

|

|

|

|

р,

см2/Вс

200 |

|

|

|

|

|

|

|

|

|

190 |

1 |

|

|

|

|

|

|

|

|

180 |

|

|

|

|

|

2 |

б |

||

|

|

|||

170 |

|

|

|

|

|

|

|

||

|

|

|

|

|

160

150

1 |

2 |

3 |

4 |

5 |

L,мкм |

Рис.6.15. Среднее значение подвижности в канале МДП-транзистора: n-МДПТ (а); р-МДПТ (б). 1 - UИП = 4 В, 2 - UИП = 5 В.

126

Лабораторное задание

Провести моделирование переходных процессов на ЭВМ в соответствии с индивидуальным заданием.

В зависимости от варианта возможны несколько видов расчета:

1) рассчитать температурную зависимость времени задержки передачи сигнала на выход относительно тактового импульса (информационные сигна-

лы стабильны). Расчет проводить для Т = –55 оС; 25 оС; 125 оС;

2) рассчитать зависимость времени задержки передачи сигнала на выход относительно тактового импульса (информационные сигналы стабильны) от величины разброса (разницы 0%, 10%, 20%) удельной крутизны p- и n-каналь-

ных МДПТ; 3) исследовать влияние задержки инвертировапнного сигнала (задержка 0,

1, 5, 10 нс) на работоспособность схемы (выполнение логической функции,

время задержки сигнала на выходе);

|

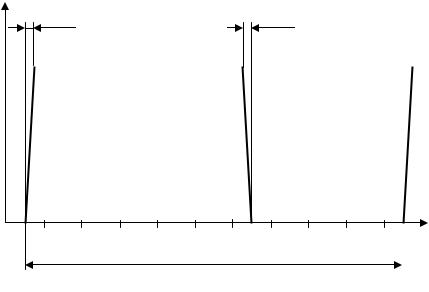

0,5 нс |

|

|

|

0,5 нс |

|

|

|

|

|

|

|

|

|

|

|

|

5 10 15 20 25 30 35 40 45 50  t, нс

t, нс

T = 50 нс

Рис.6.16. Форма входного импульса при анализе переходного процесса в схеме на ЭВМ

127

4) определить максимальную частоту тактовых импульсов, при которой схема работает без искажений.

При анализе переходных процессов использовать импульсы трапециедальной формы (рис.6.16): U1 = UИП = 5 B; U0 = 0 В; Cн = 1 пФ.

Порядок выполнения работы Рекомендуется следующий порядок выполнения работы:

1) изучить принципы работы проходного ключа и схемы с его использова-

нием;

2)ознакомиться с заданием и подготовить исходные данные для расчета по программе Orcad;

3)выполнить исследовательскую часть работы;

4)оформить отчет и защитить работу.

Требования к отчету

Отчет должен содержать:

1)название лабораторной работы;

2)краткий конспект теоретической части;

3)электрические схемы и геометрические размеры МДП-транзисторов;

4)результаты моделирования переходных процессов на ЭВМ;

5)выводы.

Контрольные вопросы

1. Какие преимущества передачи сигнала при параллельном объединении

п- и р-канальных МДП-транзисторов?

2.Для какого транзистора в ПК влияние подложки сказывается сильнее?

3.Как реализовать парафазное управление транзисторами в ПК?

128

4.Какие комбинации управляющих сигналов приводят к метастабильному состоянию ПК?

5.Какие преимущества у логических схем, использующих ПК?

6.Почему на зависимости сопротивления ПК от входного напряжения есть экстремум?

7.Расскажите о температурных свойствах ПК.

8.Сравните входные и выходные емкости ПК и обычного КМДП инвер-

тора.

9.Сравните быстродействие аналогичных схем на ПК и на традиционных КМДП-транзисторах.

10.Почему искажаются амплитуды логических уровней в схеме ПК от-

дельно по n- и p-канальным транзисторам, но нет искажений в собранной схе-

ме?

11. Как подается напряжение питания на ПК.

12. Какое соотношение размеров р- и п-канальных транзисторов опти-

мально?

13. Для чего необходимо использовать тактовые импульсы с крутыми фронтами?

14. Какие меры предосторожности надо соблюдать при использовании ПК в логических схемах?

129

Приложение 6.1

ПАРАМЕТРЫ МОДЕЛЕЙ ТРАНЗИСТОРОВ В учебной лаборатории для построения схем используются модели тран-

зисторов, сответствующие упрощенным моделям третьего уровня для техпр-

цесса AMIS_C5 (0,50 micron) фирмы ON Semiconductor. Текст SPICE описания моделей приведен ниже.

.MODEL nekt NMOS

+LEVEL = 3

+KP = 1.259355E 4 VTO = 0.7640855

+CGDO = 2.15E 10 CGSO = 2.15E 10 CGBO = 1E 10

+TOX = 1.4E 8 PHI = 0.7 GAMMA = 0.5483559

+NSUB = 1E17 DELTA = 3.0541177

+UO = 662.6984452 ETA = 3.162045E 6 THETA = 0.1013999

+VMAX = 1.442228E5 KAPPA = 0.3

+RSH = 7.513418E 3 NFS = 1E12 TPG = 1

+XJ = 3E 7 LD = 1E 13 WD = 2.334779E 7

+CJ = 4.258447E 4 PB = 0.9140376 MJ = 0.435903

+CJSW = 3.147465E 10 MJSW = 0.1977689

.MODEL pekt PMOS

+LEVEL = 3

+KP = 3.924644E 5 VTO = 0.9444911

+CGDO = 2.34E 10 CGSO = 2.34E 10 CGBO = 1E 10

+TOX = 1.4E 8 PHI = 0.7 GAMMA = 0.6243261

+NSUB = 1E17 DELTA = 0.1118368

+UO = 250 ETA = 0 THETA = 0.1633973

+VMAX = 1E6 KAPPA = 30.1015109

130

+RSH = 33.9672594 NFS = 1E12 TPG = 1

+XJ = 2E 7 LD = 5E 13 WD = 4.11531E 7

+CJ = 7.285722E 4 PB = 0.96443 MJ = 0.5

+CJSW = 2.955161E 10 MJSW = 0.3184873

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

1. Шишина Л.Ю. Основные устройства цифровой микросхемотехники.

Часть 1. Учебное пособие. Москва 2013, РИО МИЭТ.

2.Алексенко А.Г. Основы микросхемотехники. Лаборатория знаний. М.

Бином 2009.

3.Пухальский Г.И., Новосельцева Т.Я.. Проектирование цифровых уст-

ройств. Лань, 2012.

131

Лабораторная работа № 7

ИССЛЕДОВАНИЕ СХЕМЫ JK-ТРИГГЕРА

Цель работы: изучение принципов работы интегральных триггерных схем.

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

ТРИГГЕРНЫЕ СХЕМЫ

Логические схемы с несколькими логическими переменными на входах, в которых имеются два устойчивых состояния и два выхода, при этом на одном выходе схемы снимается высокий потенциал (“1”, Q), а на другом - его инверсия (“0”, Q ), называется триггерами. Выходные сигналы в триггерах зависят не только от входных управляющих переменных, но и от значений выходных переменных в предыдущем интервале времени. В интервале между входными управляющими логическими сигналами состояние триггера не меняется, он “помнит” набор предыдущих логических переменных, на выходах сохраняются соответствующие потенциалы (бистабильная ячейка, БЯ). Изменить состояние триггера и, значит, величины потенциалов на выходах, возможно только под действием определенного набора входных логических переменных и значений выходных переменных в предыдущем интервале работы схемы.

Поскольку для переустановки триггера в конечном диапазоне времени необходима некоторая последовательность управляющих сигналов при наличии на выходах конкретного логического состояния, триггерные схемы относятся к классу последовательностных логических схем. Способность триггеров под действием определенного набора входных логических переменных “запо-

132