Cборник_ЛР

.pdfПо способу формирования логических уровней U1 и U0 ключевые схемы на МДПТ условно разделяются на схемы “с отношением”, “без отношения” и

смешанного типа [5]. Схемы “с отношением” характеризуются тем, что вели-

чина хотя бы одного логического уровня определяется соотношением прово-

димостей ключевого транзистора и нагрузочного компонента.

Известны следующие типы ключевых схем:

1)инвертор с линейной нагрузкой; в качестве нагрузочного компонента используется резистор;

2)инвертор с нелинейной нагрузкой; в качестве нагрузки используется МДП-транзистор, работающий всегда в пологой области ВАХ (рис.5.3,в);

3)инвертор с квазилинейной нагрузкой; имеет в качестве нагрузки МДПТ,

работающий всегда в крутой области ВАХ (рис.5.3,г); 4) инвертор с токостабилизирующей нагрузкой; нагрузочным компонен-

том является МДПТ со встроенным каналом того же типа проводимости, что и у ключевого транзистора, а токовая стабилизация нагрузочного транзистора достигается постоянством напряжения UЗИ = 0 (рис.5.3,д);

5) инвертор на МДП-транзисторах с дополняющими (комплементарными)

типами проводимости (на КМДП-транзисторах) (рис.5.3,е).

Первые четыре типа инверторов являются схемами “с отношением”, а

КМДП-инвертор - схема “без отношения”, схемы смешанного типа являются разновидностью КМДП-схем.

Далее будем рассматривать характеристики схем “с отношением”.

Передаточные характеристики инверторов на МДП-транзисторах

Теоретический расчѐт передаточных характеристик инверторов на МДПТ проводится на основании условия равенства тока стока входного транзистора и тока нагрузочного элемента

93

Iвх Iн |

(5.11) |

Приняв выражение для ВАХ входного транзистора в соответствующей облас-

ти работы (5.1) - (5.6) и выражение для ВАХ нагрузочного компонента, реша-

ем полученное уравнение относительно Uвых или Uвх.

Рассмотрим пример построения передаточной характеристики для инвер-

тора с нелинейной нагрузкой. В соответствии со схемой включения (рис.5.3,в)

запишем уравнения для напряжений нагрузочного транзистора Tн:

U ЗИн U ИП U вых , |

|

U ПИн U вых , |

(5.12) |

U СИн U ИП U вых |

|

и входного транзистора Tвх: |

|

U ЗИвх U вх , |

|

U ПИвх 0, |

(5.13) |

UСИвх U вых .

Всхеме инвертора с нелинейной нагрузкой нагрузочный транзистор Tн

работает в пологой области ВАХ. Воспользуемся уравнением (5.6) с учѐтом заданных в схеме напряжений (5.12) и получим выражение для тока нагрузоч-

ного транзистора:

Iн kн UИП Uпор н 1 Uвых 2  1 (5.14)

1 (5.14)

В интегральных схемах пороговые напряжения однотипных транзисторов равны Uпор н = Uпор вх, поэтому опустим в дальнейшем индексы “н” и “вх”.

Коэффициенты влияния подложки входного и нагрузочного транзисторов в общем случае отличаются. Это объясняется тем, что потенциал истока на-

грузочного транзистора (рис.5.3) меняется в процессе переключения от уровня логической “1” до уровня логического “0”, а исток входного транзистора за-

землѐн. Отсюда следует, что н вх.

94

Iн

Uвых

A U ИП

Рис.5.4. ВАХ нагрузочного транзистора ключа с нелинейной нагрузкой.

|

|

|

|

|

|

|

U 1 |

|

UИП Uпор |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

вых |

|

|

1 |

|

|

|

|||||||||

|

Iвых |

|

|

II |

|

|

|

|

|

|

|

|

U1 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вх |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вх |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

III |

|

|

|

|

|

|||||||

а |

|

|

|

|

|

|

C |

|

|

Uвх Uвх C |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх Uпор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F C |

|

|

A U ИП |

|

|

|

Uвых |

||||||||||||||

б

Uвых |

B |

|

|

A |

|

C

F

Uпор

|

вх |

U |

|

|

|

вых |

|

U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

пор |

|

|

U |

|

|

|

|

|

|

|

вх |

|

|

U |

|

|

|

|

|

|

|

|

вых |

|

P |

U |

|

|

|

|

|

C F |

D |

C |

|

Uвх |

Рис.5.5. Выходные (а) и передаточная (б) характеристики ключа с нелинейной нагрузкой. Пунктирные линии характеристик для случая kн меньшей величины

95

В дальнейшем при выводе передаточной характеристики сохраним индек-

сы у этих коэффициентов н и вх, а при расчѐтах передаточных характери-

стик можно для упрощения принять н = вх.

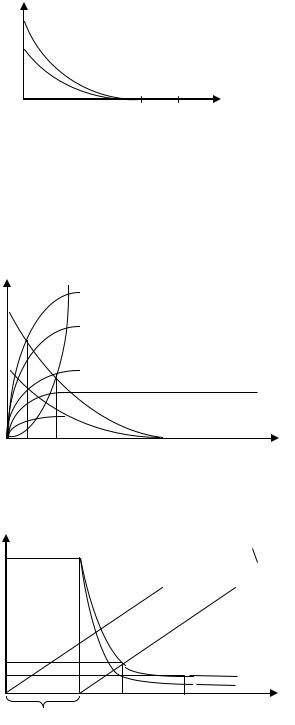

На рис.5.4 показана ВАХ нагрузочного транзистора, полученная из урав-

нения (5.14) в соответствии со схемой включения Tн, когда UСИ = UИП Uвых.

Штриховой линией показаны ВАХ Tн с меньшим значением удельной крутизны kн.

На рис.5.5,а представлены совмещѐнные ВАХ входного и нагрузочного транзистора.

Входной транзистор Tвх работает в области отсечки (область I) при

Uвх < Uпор вх, тогда, пренебрегая токами обратносмещѐнных переходов, полу-

чаем Iвх = 0, и так как Iвх = Iн = 0, то из (5.14) получаем в данном случае вели-

чину

U вых |

U ИП U пор |

(5.15) |

||

1 |

н |

|||

|

|

|||

(точка A на рис.5.4 и на рис.5.5,а).

Когда входное напряжение Uвх > Uпор вх, транзистор Tвх начинает работать в пологой области ВАХ (условия (5.5) и (5.13), область III на рис.5.5,а).

|

|

|

U вых |

U вх U пор |

|

|

|

|

|

|

|

(5.16) |

|||||||

|

|

|

|

|

1 вх |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Тогда |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Iвх kвх Uвх Uпор 2 1 вх , |

|

|

(5.17) |

||||||||||||||

приравняем (5.14) и (5.17) и получим линейную зависимость Uвых = f(Uвх). |

|||||||||||||||||||

|

|

|

Uпор |

|

|

|

|

|

|

|

|

|

Uвх |

Uпор |

|

||||

|

|

UИП |

|

|

k |

вх |

|

1 |

н |

|

|

||||||||

Uвых |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(5.18) |

||||

|

|

|

kн |

|

|

|

|

|

|

|

|

|

н |

|

|||||

|

|

1 |

|

|

|

1 вх |

1 |

|

|

||||||||||

По мере дальнейшего увеличения Uвх будет выполняться условие |

|

||||||||||||||||||

|

|

Uвых Uвх Uпор 1 вх , |

|

|

|

(5.19) |

|||||||||||||

96

входной транзистор перейдѐт в крутую область ВАХ (точка C на рис.5.5,а),

при этом уравнение ВАХ транзистора Tвх в области II рис.5.5,а имеет вид:

|

|

|

|

|

|

I |

вх |

k |

вх |

2 U |

вх |

U |

пор |

U |

вых |

|

1 |

U 2 |

|

. |

|

|

|

|

(5.20) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

вх |

|

|

вых |

|

|

|

|

|

|

|||||||

Соответственно из условия (5.13) получим |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

U вых |

|

|

|

|

|

|

kн |

U |

ИП |

U |

пор |

2 |

|

|

|

|

|

2 U |

|

|

|

|

||||||

U |

|

U |

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

U |

|

|

|

U |

|

. (5.21) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

вх |

|

пор |

|

2 |

|

|

|

вх |

|

|

2kвх |

U вых 1 н |

|

|

|

н |

|

вых |

|

ИП |

|

пор |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

На рис.5.5,б показана передаточная характеристика инвертора с нелинейной нагрузкой, полученная при помощи рис.5.5,а и уравнений (5.15), (5.18) и (5.21)

на участках AB, BC и CD соответственно.

Координаты точки A на рис.5.5 определяют величину уровня логической

“1” (уравнение (5.15)). Величина уровня логического “0” (точка F на рис.5.5)

определяется из уравнения (5.21) при подстановке значения U1 |

U1 . |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

вх |

вых |

|

Координаты точки C вычисляются из совместного решения уравнения |

|||||||||||||||

(5.18) и равенства (5.19). |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Координаты пороговой точки P, когда Uвх = Uвых, получим из уравнения |

|||||||||||||||

(18) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх P Uвых P |

|

UИП |

Uпор 1 |

, |

(5.22) |

||||||||||

1 н |

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|||

k |

|

|

|

1 |

|

|

|

|

|

|

|

|

|||

вх |

|

|

н |

|

2 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

. |

|

|

(5.23) |

||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

kн |

|

1 вх |

|

|

|

|

|||||||||

Передаточные характеристики для других инверторов получаются анало-

гично. Уровень логической единицы U1 в МДП ключевых схемах определяет-

ся только типом нагрузки: U1 = Uвых max. Уровень логического нуля U0 (точка F

на рис.5.5,а,б) определяется, как видно из уравнений (5.18) и (5.21), соотно-

шением удельных крутизн входного и нагрузочного транзистора. Выбор от-

ношения kвх / kн должен обеспечить работоспособность МДП-инвертора, что-

бы уровень логического нуля в инверторе Uвых0 Uпор .

97

Масштабирование параметров МДП-схем. При изготовлении МДП тран-

зисторных схем длина канала входного управляющего транзистора делается минимальной. Уменьшение длины канала достижимо только при использова-

нии прецизионных технологических операций. При уменьшении длины кана-

ла в S раз ряд параметров МДП-структуры необходимо масштабировать для обеспечения работоспособности прибора, чтобы скомпенсировать вклад эф-

фектов короткого канала. Правила масштабирования представлены в табл.5.1.

Переходные процессы в МДП-ключах

Инерционность МДП ИС определяется емкостями эквивалентной схемы транзистора (ѐмкости перекрытия затвор-исток, затвор-сток, распределѐнная ѐмкость затвор-канал, ѐмкости обратносмещѐнного p - n-перехода сток-под-

ложка, исток-подложка) и паразитными емкостями межсоединений. Заряд вы-

ходной ѐмкости Cн осуществляется током нагрузочного элемента, поэтому время фронта tфр01 зависит от крутизны нагрузочного транзистора и величины

Cн, а разряд выходной ѐмкости происходит через открытый входной транзи-

стор, время среза tср10 определяется прежде всего крутизной (величиной тока),

областью работы ВАХ управляющего транзистора. Время, в течение которого выходной сигнал изменяется в пределах 0,1 Uлог … 0,9 Uлог, вычисляется в результате решения нелинейного уравнения

Uко н

t Cн dU вых t  IС t ,

IС t ,

Uнач

где Uнач и Uкон соответствуют 0,1 (0,9) Uлог, а выражение для тока стока зави-

сит от режима работы транзистора.

98

|

|

|

|

|

|

Таблица 5.1 |

|

Правила масштабирования параметров МДП-транзисторов |

|

|

|||||

|

|

|

|

|

|

|

|

Параметр |

|

Масштабный коэффициент |

|

||||

|

|

|

|

|

|

|

|

|

|

|

E = const |

UИП = const |

|

||

|

|

|

|

|

|

|

|

|

|

|

= const |

Uдрейф = const |

= const |

Uдрейф = const |

|

|

|

|

|

|

|

||

Размеры прибора |

S |

S |

S |

S |

|

||

Толщина подзатворного диэлектрика dок |

S |

S |

S1/2 |

S1/2 |

|

||

Концентрация примеси в подложке N |

S-1 |

S-1 |

S-1 |

S-1 |

|

||

Пороговое напряжение Uпор |

S |

S |

S1/2 |

S1/2 |

|

||

Напряжение питания UИП |

S |

S |

1 |

1 |

|

||

Ток питания I |

S |

S |

S-1/2 |

S1/2 |

|

||

Ёмкость затвора C |

S |

S |

S3/2 |

S3/2 |

|

||

Время переключения вентиля |

S |

S |

S2 |

S1/2 |

|

||

Рассеиваемая мощность P |

S2 |

S2 |

S-1/2 |

S1/2 |

|

||

Произведение мощности на время переключения P |

S3 |

S3 |

S3/2 |

S |

|

||

99

Температурная зависимость параметров МДП ИС.

С увеличением температуры уменьшается абсолютное значение величины

Uпор. Это связано, главным образом, с температурной зависимостью уровня

Ферми. Знак d F отрицателен для n-МДПТ и положителен для p-МДПТ. dT

Величина коэффициента влияния подложки растѐт с увеличением темпе-

ратуры, что связано также с зависимостью F = f(T).

Температурное изменение удельной крутизны связано с температурной зависимостью подвижности носителей. Уменьшение подвижности носителей с ростом температуры может полностью скомпенсировать увеличение тока из-

за снижения порогового напряжения МДПТ.

Задание на лабораторную работу

Порядок проведения расчѐтов.

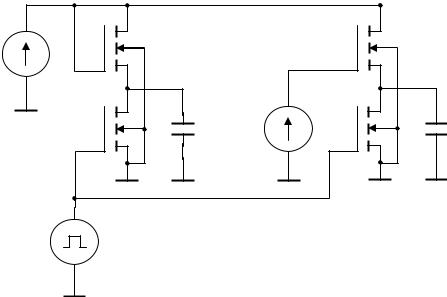

На основании изучения описания программы PSPICE и описания лабора-

торной работы составляется входной файл для расчѐтов на ЭВМ в соответст-

вии с заданным вариантом (пример схемы и входного файла представлен на рис.5.6). Номер варианта соответствует номеру фамилии студента в списке группы. Ряд параметров, необходимых для моделирования схемы, задаѐтся в табл.5.2, там же указаны номера исследуемых схем (рис.5.7) и измеряемые па-

раметры. В каждом варианте проводится расчѐт передаточной и переходной характеристик для указанных модификаций параметров схемы. Результаты расчѐта передаточных и переходных характеристик проверяются на дисплее преподавателем или инженером, после чего выводятся на печать.

100

VDD 1

T2 |

|

3 |

T4 |

|

|

|

|

4 |

VG |

|

5 |

C1 |

|

|

C2 |

T1 |

|

|

T3 |

2

VIN

0

* Example of input file

*The comparative analysis of MOS inverters with nonlinear and quasilinear load C1 4 0 0.5 PF

C2 5 0 0.5PF

VDD 1 0 DC 5

VIN 2 0 PULSE(0 5 10NS 1.5NS 1.5NS 50NS 300NS)

VG 3 0 DC 7

M1 4 2 0 0 MODN L=5U W=30U

M2 1 1 4 0 MODN L=5U W=5U

M3 5 2 0 0 MODN L=5U W=30U

M4 1 3 5 0 MODN L=5U W=5U

.MODEL MODN NMOS(VTO=0.8 KP=40E-6 LEVEL=1 TOX=40NM XJ=0.7U)

.DC VIN 0 5 0.001

.TRAN 3NS 300NS

.PROBE

.END

Рис.5.6. Пример схемы и входного файла для еѐ описания

101

Обработка результатов расчѐта

При помощи полученных распечаток графиков передаточных и переход-

ных характеристик определяются и заносятся в табл.5.3 следующие парамет-

ры (рис.5.8, 5.9) для всех вариантов:

- величина логического перепада Uлог Uвых1 Uвых0 ;

-пороговая точка характеристики Uп = Uвх = Uвых ;

-величины напряжений помехозащищѐнности для логических состояний

“0” и “1” |

U 0 |

|

U п U 0 |

, U 1 |

|

U 1 |

U п |

; |

|

пз |

|

вх |

пз |

|

вх |

|

|

- величины напряжений помехоустойчивости для логических состояний

“0” и “1” Uпу0 D0 Uвх0 , Uпу1 Uвх1 D1 , где D0 и D1 - точки единичного уси-

ления, определѐнные касательными прямыми к передаточной характеристике,

проведѐнными под углом в 45 ;

- времена фронта и среза tфр01 , tср10 , определяемые по уровням 0,1 Uлог и

0,9 Uлог выходного сигнала;

- времена задержки распространения сигнала из логического состояния

“0” в логическе состояние “1” и из логического состояния “1” в логическое состояние “0” tзд01р , t10зд р , tзд р. ср tзд01р t10зд р  2 , которые определяются по уров-

2 , которые определяются по уров-

ням 0,5 Uлог или 0,5(Uвх max – Uвх min). В общем случае входной сигнал может изменятьтся в пределах, не соответствующих значениям логических уровней схемы (например, Uвх max = UИП, Uвх min = 0 В).

- средняя потребляемая мощность Pпотр. ср U2ИП Iвых1 Iвых0 . В состоянии

“1” на выходе схемы в МДП ключевых схемах ток не течѐт, поэтому

Pпотр. ср 12 Iвых0 .

102