- •Комп’ютерна схемотехніка. Архітектура комп’ютерів 2 зміст

- •2.1. Класифікація, призначення та основні характеристики пам'яті

- •2.2. Оперативна пам’ять (оп)

- •2.2.2. Статична пам'ять на біполярних транзисторах

- •2.3. Постійна пам'ять (пп)

- •2.9. Зовнішня оптична пам'ять

- •1. Представлення та обробка інформації

- •Класифікація засобів обчислювальної техніки

- •1.2. Класифікація комп’ютерів

- •1.3. Структурна схема компю’терів, що використовують спільну шину

- •1.4. Системи числення

- •1.4.1. Базові параметри та класифікація систем числення

- •1.4.2.Загальні принципи побудови систем з послідовним обчисленням символів

- •1.4.3. Загальні принципи побудови систем числення з паралельним обчисленням символів

- •1.5. Кодування знакозмінної інформації. Коротка характеристика груп кодів, родинних прямому, зворотному, додатковому. Особливості застосування в комп'ютерах

- •1.6. Формати даних і команд сучасних комп’ютерів

- •1.7. Процесори

- •1.7.1. Склад і призначення пристроїв

- •1.7.2. Блок додавання чисел у формі з фіксованою крапкою

- •1.7.3. Особливості виконання складання чисел у формі з плаваючою крапкою

- •1.7.4. Реалізація процесора двійкового множення. Загальні положення

- •1.7.5. Реалізація множення в прямому коді

- •I варіант.

- •II варіант.

- •III варіант.

- •IV варіант

- •1.7.6. Реалізація в процесорі операції множення в додатковому коді

- •1.7.7. Реалізація методів прискореного множення в процесорах

- •1.7.8. Схемні методи прискореного множення

- •1.7.9. Особливості виконання множення чисел з плаваючою крапкою

- •1.8. Реалізація двійкового ділення в процесорі

- •1.8.1. Реалізація ділення чисел з фіксованою крапкою в прямому коді

- •1.8.2. Особливості ділення чисел у формі з плаваючою крапкою

- •1.9. Добування квадратного кореня

- •Частина 2. Пам'ять комп'ютерів

- •2.1. Класифікація, призначення та основні характеристики пам'яті

- •2.2 Оперативна пам’ять (оп)

- •2.2.1 Внутрішня організація оп

- •2.2.2.Статична пам'ять на біполярних транзисторах

- •2.2.3. Статична пам'ять на езл-інтегральних схемах (іс)

- •2.2.4. Статична пам'ять на уніполярних транзисторах (на мон іс)

- •2.2.5. Динамічна пам’ять (дп) на моп транзисторах

- •2.2.6. Побудова пам’яті необхідної розмірності

- •2.3. Постійна пам'ять (пп)

- •2.3.1. Типи пп

- •2.3.2. Масочні пп (мпп)

- •2.3.3. Однократнопрограмована пам'ять

- •2.3.4. Репрограмована пам'ять

- •2.3.5. Flash-пам'ять

- •2.4. Зп с послідовним доступом(зппд)

- •2.4.1. Зппд на регістрах зсуву

- •2.4.2. Елемент зп з послідовним доступом на мон-транзисторах

- •2.4.3. Буферний зп типу "черга" (бп)

- •2.4.4. Пам'ять типу "список"/"стек"

- •2.5. Асоціативна пам'ять

- •2.6. Зовнішня пам'ять (зп)

- •2.6.1. Типи зп

- •2.6.2. Зовнішня магнітна пам'ять (змп)

- •2.6.3. Способи цифрового магнітного запису

- •2.7. Зовнішня пам'ять з прямим доступом(зпПрД)

- •2.7.1. Накопичувачі на гнучких магнітних дисках(нгмд)

- •2.7.2. Накопичувачі на жорстких магнітних дисках(нжмд)

- •2.7.3. Raid – дискові масиви

- •2.8. Зовнішні зп з послідовним доступом. Накопичувачі на магнітних стрічках(нмс). Стримери

- •2.9. Зовнішня оптична пам'ять

- •2.9.1. Оптичні диски типу cd

- •2.9.2. Оптичні диски типу dvd

- •2.10. Контроль роботи пристроїв пам’яті

- •3.1. Пристрій управління

- •3.1.1 Склад пристрою управління

- •3.1.2. Пу з жорсткою логікою

- •3.1.3. Мікропрограмний пристрій управління (пристрій управління з гнучкою логікою)

- •3.1.4. Мікропрограмний пристрій управління зі змінною тривалістю реалізації мікрокоманд.

- •3.2. Системи переривань

- •3.2.1. Типи і основні характеристики системи переривань

- •3.3. Система управління вводом/виводом

- •3.4. Організація мультипрограмного режиму роботи в сучасних комп’ютерах

- •3.4.1. Форми обслуговування користувачів і види мультипрограмування (мпр)

- •3.4.2. Динамічний розподіл пам'яті

- •3.4.3. Система захисту пам’яті (сзп)

- •0 1 2 3 4 5 6 7

- •3.5. Системи автоматичного контролю

- •3.5.1. Види помилок і способи контролю

- •3.5.2. Контроль передачі кодів

- •3.5.3. Контроль роботи комбінаційних схем

- •3.5.4. Контроль виконання операцій в процесорах

- •3.5.5. Контроль роботи процесорів по модулю 3

II варіант.

![]()

Множене множимо на молодшу цифру множника, отриманий перший ЧД передаємо в суматор, зсуваємо множене на 1 розряд вліво, множимо множене на сусідню старшу цифру множника і т.д. Множення закінчується можливою передачею на суматор зсунутого вліво на (n -1) розрядів множеного. Результат добутку також представлений подвоєним числом розрядів, але старші цифри добутку будуть розташовані в додаткових n-розрядах.

Приклад X = 0.1011 Y = 0.1101

|

|

|

|

|

1 0 1 1 |

X | |||

|

|

|

|

0 0 0 0 |

0 0 0 0 |

0 | |||

|

|

1 1 0 |

1 |

|

|

1 0 1 1 |

| ||

|

|

|

|

0 0 0 0 |

1 0 1 1 |

1 | |||

|

|

|

0 |

|

1 |

0 1 1 |

X21 | ||

|

|

|

|

|

0 0 0 0 |

1 0 1 1 |

2 | ||

|

|

|

1 |

|

1 0 |

1 1 |

X22 | ||

|

|

|

|

|

0 0 1 1 |

0 1 1 1 |

3 | ||

|

|

|

1 |

|

1 0 1 |

1 |

X23 | ||

|

|

|

|

|

1 0 0 0 |

1 1 1 1 |

Z | ||

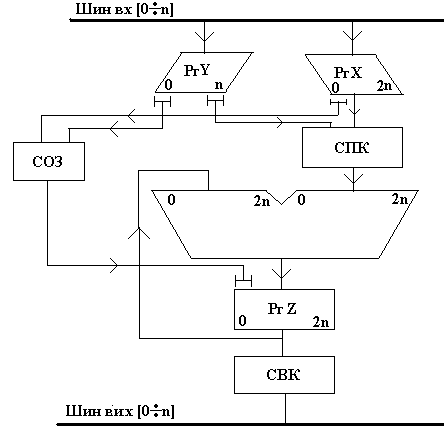

Схемна реалізація II варіанту, як і першого, вимагає 3-х регістрів, причому 2 з них (РгХ - множене, Рг Z - добутки) мають подвійну кількість розрядів, в РгХ і РгУ ораганізовані ланцюги зсуву на 1 розряд в РгХ - вліво, в РгУ-вправо. До складу БО входять: 2 n-розрядних комбінаційних суматори, схеми передачі коду (СПК), схема видачі коду (СВК), визначення знака (СВЗ) результату.

СПК управляють молодшим розрядом множника, якщо в ньому 1, то зсунуте множене на суматор передається, якщо 0 - немає. СВ3 включає логічну схему mod2, що запам'ятовує тригер.

Реалізація I варіанта можлива за скороченою схемою, при цьому можна зменшити число розрядів в регістрі множеного до величини ~ 15-20% від n.

III варіант.

Z

n

Помножити множене на молодшу цифру множника, і цей ЧД передати на суматор. Потім зсунути суматор на 1 розряд вправо. Примножуючи множене на наступну цифру множника, отримуємо другий ЧД, яке передаємо в суматор, після чого суматор знову зсувається на 1 розряд вправо. Множення завершується n-м зрушенням суматора вправо.

|

|

|

|

0 |

1 0 1 1 |

|

X | |||

|

|

|

|

0 |

0 0 0 0 |

0 0 0 0 |

0 | |||

|

|

1 1 0 |

1 |

|

0 |

1 0 1 1 |

|

| ||

|

|

|

|

0 |

1 0 1 1 |

0 0 0 0 |

1 | |||

|

|

|

|

|

0 |

0 1 0 1 |

1 0 0 0 |

1*2-1(1-й зсув) | ||

|

|

1 1 |

0 |

|

0 |

1 0 1 1 |

|

| ||

|

|

|

|

|

0 |

0 1 0 1 |

1 0 0 0 |

2 | ||

|

|

|

|

|

0 |

0 0 1 0 |

1 1 0 0 |

2*2-1(2-й зсув) | ||

|

|

1 |

1 |

|

0 |

1 0 1 1 |

|

XY-(n-2) | ||

|

|

|

|

|

0 |

1 1 0 1 |

1 1 0 0 |

3 | ||

|

|

|

|

|

0 |

0 0 1 1 |

0 1 1 1 |

3*2-1(3-й зсув) | ||

|

|

|

1 |

|

0 |

1 0 1 |

1 |

X23 | ||

|

|

|

|

|

1 |

0 0 0 1 |

1 1 1 0 |

4 | ||

|

|

|

|

|

0 |

1 0 0 0 |

1 1 1 1 |

Z | ||

Склад схеми: 3 регістра, тільки Рг Z має подвійну кількість розрядів, в Рг Y є ланцюг правого зсуву, ланцюг може бути і в Рг Z, замість зсуву можна використовувати «косу» передачу на 1 розряд вправо. В даному БО СПК управляється молодшим розрядом множника. Т.ч. додавання виконується по старшим n розрядам в цьому БО можна використовувати n-розрядний комбінаційний суматор.

Мікропрограма

1

1

1

1 1

1