- •Содержание

- •1. Техническое задание на курсовой проект.

- •2. Разработка проекта полного технологического маршрута создания кмоп-структуры.

- •3 .1. Предварительные расчёты порогового напряжения транзисторов с учётом их конструктивно-технологических параметров.

- •3.2. Расчёт зависимости порогового напряжения от концентрации примеси на поверхности полупроводника.

- •3.3. Расчёт зависимости порогового напряжения от толщины подзатворного оксида.

- •3.4. Построение эскизов одномерных распределений примеси в вертикальных сечениях затвора и стока-истока.

- •3.5. Определение режимов операций технологического маршрута.

- •3.5.1. Определение режимов формирования кармана.

- •3.5.2. Определение режимов формирования подзатворного оксида.

- •3.5.3. Определение режимов корректировки порогового напряжения.

- •3.5.4. Определение режимов формирования стока-истока.

- •3.6. Двухмерное моделирование технологического маршрута создания

- •4. Реферативная часть курсового проекта

- •Заключение

- •Список использованных источников.

- •Приложение.

1. Техническое задание на курсовой проект.

Разработать технологический маршрут создания n- и p-канальных МОП-транзисторов в составе КМОП-структуры, имеющих параметры, представленные в табл.1.1.

Таблица 1.1 - Исходные данные КМОП-структуры

|

|

|

|

|

Тип затвора |

|

мкм |

Тип кармана |

|

|

0,8 |

|

|

|

|

|

p |

|

|

|

|

|

Тип изоляции |

|

|

|

|

|

LOCOS |

Общие данные для всех вариантов технического задания:

Концентрация примеси в подложке:

.

.Концентрация примеси в

и

и

затворе:

затворе:

,

, .

.Заряд электрона:

.

.Диэлектрическая постоянная:

.

.Относительная проницаемость

:

:

.

.

Относительная проницаемость

:

:

.

.

Для наглядности указанные параметры показаны на рисунке 1 на примере n-МОП-транзистора с n+-затвором и p-карманом.

Рисунок 1. Структура и основные размеры n-МОП-транзистора с n+затвором и p-карманом.

2. Разработка проекта полного технологического маршрута создания кмоп-структуры.

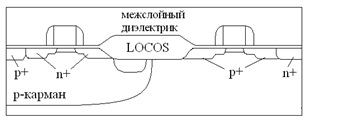

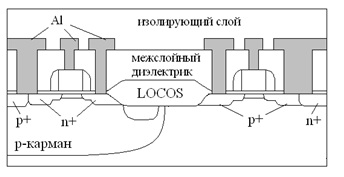

В приложении изображены эскизы конструкции КМОП–структуры с p- (рисунок 2.1) и n-каналами (рисунок 2.2).

Технологический маршрут изготовления КМОП-структуры представляет собой последовательность технологических операций, необходимых для формирования интегральных n- и p-канальных транзисторов, области изоляции и металлизации.

В соответствии с примером технического задания, приведенного выше, КМОП-структура содержит следующие элементы:

n-канальный МОП-транзистор с n+-Si*- затвором в p-кармане на n-подложке;

p-канальный МОП-транзистор с n+-Si*-затвором в на n-подложке;

область щелевой изоляции (LOCOS) между транзисторами;

металлизацию.

Выбор подложки: n-тип, КЭФ-4,5 (N=1015см−3), кристаллографическая ориентация поверхности (100).

Таблица 2.1 – Технологический маршрут создания КМОП-структуры

№ п/п |

Технологическая операция |

Режим обработки |

Примечание |

|

|

Окисление |

1000°С, 30мин, О2 |

|

|

|

Фотолитография "p-карман” |

|

4мкм |

|

|

Имплантация |

B, 20 кэВ, 2*1013 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Окисление |

1200°С,

25

мин,

|

|

|

|

Отжиг |

1200°С, 50 мин, N2 |

|

|

|

Удаление всего SiO2 |

|

|

|

|

Окисление под Si3N4 |

950 °С, 30 мин, О2 |

30-50 нм |

|

|

Нанесение Si3N4 |

|

|

|

|

Фотолитография "Маска для LOCOS". |

|

|

|

|

ПХТ Si3N4 на всю толщину |

|

|

|

|

Удаление фоторезиста. |

|

|

|

|

Фотолитография "p+-охрана под LOCOS". |

|

|

|

|

Имплантация |

B, 40кэВ, 7·1013 см−2. |

|

|

|

Удаление фоторезиста. |

|

|

|

|

Отжиг p-охраны |

1050 °С, 60 мин, N2. |

|

|

|

Окисление LOCOS: |

950 °С, 50 мин, Н2О. |

Tпар = 100°С, Pпар = 10 атм. |

|

|

Удаление Si3N4. |

|

|

|

|

Травление SiO2 |

|

|

|

|

Окисление |

1000°С, 30 мин, О2 |

|

|

|

Фотолитография "Подгонка порогового напряжения n-МОП-транзистора" |

|

|

|

|

Имплантация |

P, 20кэВ, 8,97*1012 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Фотолитография "Подгонка порогового напряжения p-МОП-транзистора" |

|

|

|

|

Имплантация |

P, 20 кэВ, 1,16*1012 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Удаление SiO2 до Si |

|

|

|

|

Под затворное окисление |

994 °С, 34 мин, O2 |

33нм |

|

|

Нанесение поликремния |

P, 0,8 мкм, 1020 см-3 |

|

|

|

Фотолитография "Затвор n+". |

|

|

|

|

ПХТ Si* до SiO2 |

|

|

|

|

Удаление фоторезиста |

|

|

|

|

Нанесение поликремния |

B, 0,8 мкм, 1020 см-3 |

|

|

|

Фотолитография "Затвор p+". |

|

|

|

|

ПХТ Si* до SiO2 |

|

|

|

|

Удаление фоторезиста |

|

|

|

|

Фотолитография "n-LDD". |

|

|

|

|

Имплантация |

P, 60 кэВ, 3*1013 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Фотолитография "p-LDD” |

|

|

|

|

Имплантация |

B, 20 кэВ, 3*1013 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Осаждение окисла |

0.4 мкм |

|

|

|

ПХТ SiO2 |

0.427 мкм |

|

|

|

Окисление |

850°С, 20 мин, O2 |

|

|

|

Фотолитография «n+-сток, исток, контакт к n-карману» |

|

|

|

|

Имплантация |

P, 55 кэВ, 1,5*1015 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Фотолитография «p+-сток, исток, контакт к p-карману (подложке)» |

|

|

|

|

Имплантация |

B, 20 кэВ, 2,3*1015 см-2 |

|

|

|

Удаление фоторезиста |

|

|

|

|

Окисление |

900 °С, 15 мин, O2 |

|

|

|

Нанесение межслойного диэлектрика SiO2 |

|

|

|

|

Фотолитография «Контактные окна» |

|

|

|

|

ПХТ SiO2 |

|

|

|

|

Удаление фоторезиста |

|

|

|

|

Нанесение металла(Al+Si) |

|

|

|

|

Фотолитография «Металлизация» |

|

|

|

|

ПХТ Al |

|

|

|

|

Удаление фоторезиста |

|

|

|

|

Нанесение изолирующего слоя |

|

|

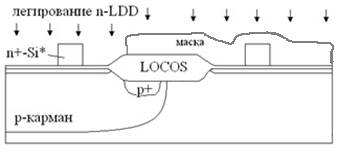

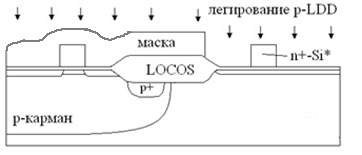

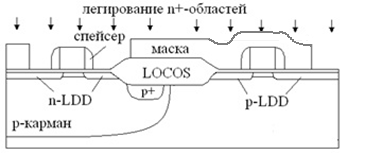

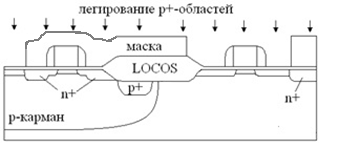

Маршрутная карта в виде последовательных модификаций поперечного сечения КМОП-структуры на этапах изготовления согласно приведенному выше технологическому маршруту показана на рисунках 2.1 – 2.10.

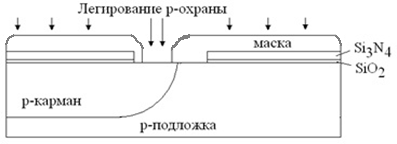

Рисунок 2.1 - Эскиз поперечного сечения КМОП-структуры (Создание карманов)

Рисунок 2.2 - Эскиз поперечного сечения КМОП-структуры (Фотолитография "Маска для LOCOS" и "p+-охрана под LOCOS")

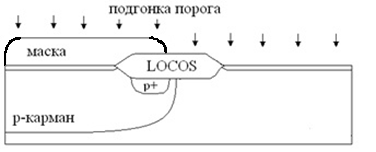

Рисунок 2.3 - Эскиз поперечного сечения КМОП-структуры (Создание изоляции LOCOS и p+ - охранной зоны)

Рисунок 2.4 - Эскиз поперечного сечения КМОП-структуры (Подгонка порогового напряжения p-МОП-транзистора)

Рисунок 2.5 - Эскиз поперечного сечения КМОП-структуры (Создание n+ - затворов)

Рисунок 2.6 - Эскиз поперечного сечения КМОП-структуры (Создание сток-истоковых областей)

Рисунок 2.7 - Эскиз поперечного сечения КМОП-структуры (Создание оксидных спейсеров)

Рисунок 2.8 - Эскиз поперечного сечения КМОП-структуры (Легирование сток – истоковых областей)

Рисунок 2.9 - Эскиз поперечного сечения КМОП-структуры (Нанесение межслойного диэлектрика – оксида)

Рисунок 2.10 - Эскиз поперечного сечения КМОП-структуры (Создание контактных окон)

,

мкм

,

мкм ,

мкм

,

мкм ,

мкм

,

мкм ,

мкм

,

мкм ,

нм

,

нм ,

мкм

,

мкм ,

,

,

мкм

,

мкм ,

см-3

,

см-3 ,

В

,

В ,

В

,

В ,

см−2

,

см−2