- •1. Представлення текстової інформації

- •2. Представлення графічної інформації

- •2.1. Растрова графіка

- •2.2. Методи растрування

- •4. Способи описання кольору

- •4.1. Моделі кольорів

- •4.2. Колірна модель cmyk та розділення кольорів

- •1. Теоретичні основи стиснення даних

- •2. Основні методи стиснення

- •2.1. Стиснення без втрати інформації

- •2.2. Стиснення з втратою інформації

- •3. Алгоритми стиснення без втрати інформації

- •3.1. Алгоритм rle

- •3.2. Коди Хафмана

- •4. Програмні засоби стиснення даних

- •5. Формати графічних даних

- •5.3. Різниця між форматом та алгоритмом стиснення

- •6. Автоматизована обробка документів

- •6.2. Вплив масштабування

- •1. Теоретичні відомості

- •1. Теоретичні відомості

- •1.1 Колір і методи опису кольору

- •1.1. Колірна модель rgb

- •1.3. Колірна модель cmyk та розділення кольорів

- •1.5. Формати графічних даних

- •4. Контрольні запитання

- •1. Теоретичні відомості

- •1.1. Параметри растрових зображень

- •1.2. Методи растрування

- •1.3. Параметри сканування.

- •1. Порядок виконання роботи

- •1.1. Сканування документа.

- •1.2. Перетворення зображення в текстовий документ.

- •1.3. Ручна сегментація документа.

- •1.4. Розрахунок лініатури растру.

- •1.5. Розрахунок роздільної здатності

- •1. Теоретичні відомості

- •1.1. Кодування

- •1.2. Декодування

- •1. Теоретичні відомості

- •1.1. Розмір біта даних на магнітному носії

- •1.2. Способи кодування даних

- •3 Питання з екзамена в якоїсь групи з попередніх років :

- •1)Приклади використання команд simd

- •2)Приклади використання кодів з корекцією помилок і пояснити принцип їх дії

- •3)Принципи архітектури numa–систем і smp–систем

- •1.Теоретичні відомості

- •1.1. Стандартні тести пк.

- •1.2. Деякі фактори, що впливають на швидкодію пк.

- •1.3. Організація роботи кеш-пам’яті.

- •1.1. Магнітні явища, на яких ґрунтується робота жорсткого диску.

- •1.2. Принцип запису інформації.

- •1.3. Принцип зчитування інформації.

- •1.4. Конструктивні елементи нагромаджувача на жорстких дисках.

- •1.5. Організація інформації на жорсткому диску.

- •1.6. Стандарти.

- •Теоретичні відомості

- •1.1. Принцип дії crt-монітору

- •1.2. Маски та їх основні типи

- •1.3. Особливості та переваги окремих типів трубок

- •1.4. Параметри монітору

- •Хід роботи

- •Теоретичні відомості

- •1.1. Динамічна і статична пам'ять.

- •1.2. Структура та призначення sram.

- •1.3. Структура та принцип дії динамічної пам'яті.

- •1.4. Типи динамічної пам'яті.

- •1.5. Специфікації модулів пам’яті.

- •1. Теоретичні відомості

- •1.1. Шинна архітектура

- •1.2. Чіпсети

- •1.3. Програмні засоби для забезпечення моніторингу

- •1.3.1. Core Temp

- •1.3.2. Hard Drive Inspector

- •1.3.3. HddScan

- •Теоретичні відомості

- •1.2.1. Системна шина

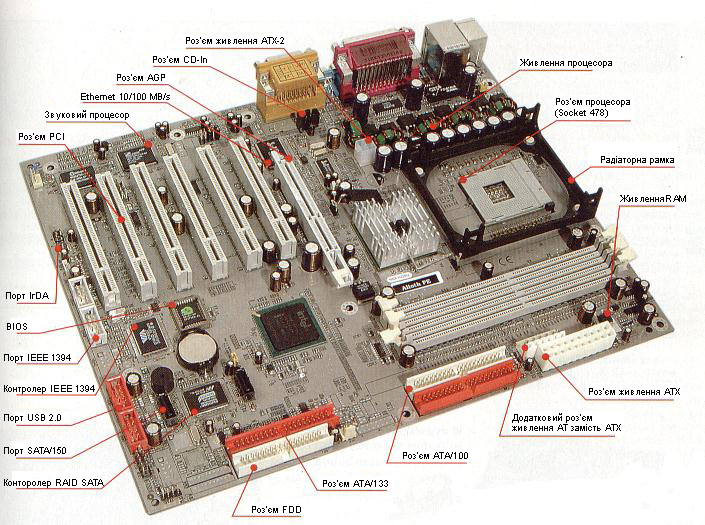

1.2.1. Системна шина

Системну шину умовно можна розділити на шину даних, адресну і шину керування. Якщо найважливішою характеристикою перших двох шин є розрядність, то стосовно до третьої говорять про кількість ліній апаратних переривань IRQ і ліній вимоги зовнішніми пристроями прямого доступу до пам'яті DMA.

Архітектура системної шини тієї або іншої моделі системної плати залежить від виробника і визначається типом платформи ПК (типом центрального процесора), застосованим набором мікросхем chipset і кількістю і розрядністю периферійних пристроїв, що підключаються до даної системної плати. Так, системні шини платформи Pentium забезпечують обмін центрального процесора з оперативною пам'яттю 64 розрядами даних, при цьому адресація даних здійснюється 32-розрядною адресою. В даний час у сучасних системних платах повсюдно застосовують локальні шини, які зв'язують процесор безпосередньо з контролерами зовнішніх пристроїв, що дозволяє значно прискорити обмін інформацією. Зараз саме шина PCI (Peripheral Component Interconnect) фірми Intel практично стала стандартом для платформ Pentium.. У сучасних комп'ютерах попередниця РСІ - системна шина ISA (Industry Standard Architecture) - використовується тільки для підключення застарілих пристроїв.

Шина EISA (Extended Industry Standard Architecture) лишилася в основному в системних платах також досить старих файл-серверів і робочих станцій.

У шині PCI між шиною процесора і самої шиною PCI розташована мікросхема узгоджувального моста. На спеціальний контролер, що розділяє керуючі сигнали шини PCI і процесора, також покладено арбітраж на шині. До шини PCI може підключатися до десяти пристроїв, у їхнє число входять і вже встановлені на системній платі. Передача даних по шині PCI може бути 32- і 64-розрядною - для цього використовуються 124- і 188-контактні роз’єми, а швидкість обміну при фіксованій тактовій частоті 33 МГц може досягати 132 Мбайт/с і 264 Мбайт/с відповідно.

Взагалі кажучи, на сьогоднішній день існує декілька схем організації шини PCI. Дві більш старі PCI Bridge Architecture і PCI Semi-Host Architecture зроблені так, що в конкретний момент шина обслуговує тільки один запит. Специфікація PCI-2.1, що побудована за схемою PCI Host Concurrent Bus Architecture, що припускає конкурентні цикли “процесор - пам'ять” і “шина PCI - пам'ять”, а також роботу з тактовою частотою 33-66 МГц і швидкістю обміну по шині до 520 Мбайт/с. Для підключення периферійних пристроїв до системної і локальної шин використовують відповідні роз’єми (slots), кількість яких вказується в описі машини (наприклад, 3xPCI slots).

1.3. Чіпсети

Але функціональні можливості плати в першу чергу визначає встановлений на ній чіпсет ( ChipSet – набір мікросхем). Це одна чи декілька мікросхем, спеціально розроблених для “допомоги” процесору. Вони містять системи керування пам’яттю і шинами, контролери переривань, прямого доступу до пам’яті - всі ті компоненти, які в оригінальній IBM PC були зібрані на окремих мікросхемах. В останніх розробках у склад наборів мікросхем для інтегрованих плат почали включатися і контролери зовнішніх пристроїв, звуку, відео, контролери Ethernet і т.п..

Зовні мікросхеми набору виглядають, як найбільші після процесора, і містять від декількох десятків до двох сотень виводів. Назва набору звичайно походить від маркировки основної мікросхеми – OPTi495SLC, SiS471, UMC491 і т.і. При цьому використовується тільки код мікросхеми всередині серії. Наприклад, повне найменування SiS471 – SiS85C471. Останні розробки використовують і власні імена (наприклад, кодова назва Whitney).

Тип набору в основному визначає функціональні можливості плати: типи процесорів, що підтримуються, структуру / об’єм кеш-пам’яті, можливі поєднання типів і об’ємів модулів пам’яті, підтримку режимів енергозбереження, можливість програмної настройки параметрів і т.п. На одному і тому ж наборі може випускатися декілька модулів системних плат, від найпростіших до досить складних, з інтегрованими контролерами портів, дисків, відео і т.п.

Вже класичною можна вважати схему чіпсета, коли ПК будувався на архітектурному стержні між північним і південним мостами. Північний міст містив в собі контролер пам'яті (плюс графічний інтерфейс AGP з 1998 року) і контролер шини PCI, через яку підключалися шина ISA і інтерфейс IDE в складі південного моста. Вінцем цієї архітектури і був чіпсет Intel 440BX, який був призначений для плат з процесором Pentium II і вперше офіційно підтримував зовнішню частоту (системної шини) 100 МГц. Тоді вже розпочалась ера нарощування частоти системної шини, що до того протягом декількох років затримувалася на позначці 66 МГц. Ця ера ще триває і кінця їй не видно – найближчі роки частота системної шини може піднятися до 800 МГц. Власне, в й підтримці 100-мегагерцової шини і полягала основна відмінність інтеловських чіпсетів 440BX і випущеного трохи раніше чіпсета Intel 440LX, у якому був вперше застосований прискорений графічний порт AGP і підтримувалася пам'ять SDRAM.

Процесор

Підтримка всіх Slot-1 процесорів Pentium II , а пізніше і Socket 370 для процесорів Celeron

Можливість двохпроцесорності, підтримка SMP

Підтримка пам'яті типу EDO RAM і SDRAM

Максимально підтримується до 512 МБайт SDRAM або 1024 Мбайт EDO RAM

Часова діаграма для EDO RAM 5-2-2-2 (при зовнішній частоті 66 МГц)

Часова діаграма для SDRAM 5-1-1-1 (при зовнішній частоті 66 МГц)

64-бітна шина пам'яті

Підтримка ECC

PIIX4 IDE-контролер

Чіп 82371AB

Підтримка Bus Mastering

Підтримка UltraDMA

Робота в режимах PIO Mode 5/DMA Mode 3

Синхронний інтерфейс PCI

Підтримується 30 і 33 МГц на шині PCI

Відповідність специфікації PCI 2.1

Power Management

Відповідність PC97

Прискорений графічний порт AGP

Підтримується AGP 1х/2x mode (66/133 МГц)

Підтримка Unified Memory Architecture відсутня

Підтримка USB

1 x 492-pin BGA чіп 82443BX

Підтримувані частоти системної шини 66 і 100 МГц

Нова архітектура з’явилася через рік після виходу 440BX в наборі мікросхем Intel 810, що в планах Intel фігурував під кодовою назвою Whitney. Нова архітектура називається хабовою, “Accelerated Hub Architecture”.

Зерно нової архітектури в тому, що дві основні мікросхеми з’єднуються між собою без використання шини PCI, але через нову виділену шину «з малим числом висновків" (low pin count LPC), вдвічі перевершуючи PCI по пропускній спроможності. Тепер кожний пристрій, включаючи шину PCI, може напряму зв'язуватися з центральним процесором, контролером пам'яті, а також з графічним контролером по каналу шириною 8 біт на тактовій частоті 133 MHz в режимі 2x, що забезпечує смугу пропускання 266 МБ/с.

2