- •Цифровые устройства и микропроцессоры

- •1. Практические занятия по цифровым устройствам

- •1.1. Практическое занятие «Основы теории цифровых устройств» Учебные цели

- •Содержание занятия

- •Учебно-материальное обеспечение занятия

- •Содержание учебных вопросов

- •1. Тест на знание логических элементов ( лэ )

- •2. Перевод чисел из десятичной системы счисления в двоичную

- •3. Методика получения переключательной функции лэ

- •4. Минимизация переключательной функции методом

- •5. Построение цифрового устройства по переключательной

- •6. Построение цифрового устройства по переключательной функции в заданном базисе

- •1.2. Практическое занятие «Минимизация переключательных функций»

- •Ицхоки я.С., Овчинников н.И., Поздняков в.Г. Импульсные и цифровые устройства. – м.: ввиа, 1983. С. 41 – 61.

- •Конспект лекций.

- •1. Описание работы цифрового устройства на языке

- •2. Проверка работоспособности цифрового устройства

- •3. Построение и заполнение карты Карно

- •4. Минимизация пф с помощью карты Карно

- •5. Синтез цифровых устройств (общее задание для всех курсантов)

- •1.3. Практическое занятие «Синтез цифровых устройств»

- •Ицхоки я.С., Овчинников н.И., Поздняков в.Г. Импульсные и цифровые устройства. – м.: ввиа, 1983. С. 41-61.

- •Конспект лекций.

- •Синтез цифрового устройства по неполному словесному описанию

- •2. Синтез полусумматора

- •3. Синтез одноразрядного сумматора

- •1.4. Практическое занятие «Элементы цифровых устройств»

- •Конспект лекций.

- •Теоретическое исследование реакции триггеров на входные сигналы заданной формы

- •2. Теоретическое исследование реакции цифровых устройств

- •2. Практические занятия по микропроцессорным системам

- •2.1. Практическое занятие «Система команд микропроцессора»

- •2. Конспект лекций.

- •1. Шестнадцатеричная система счисления (сс)

- •1.1. Примеры перевода чисел из шестнадцатеричной сс

- •2. Система команд микропроцессора

- •Все команды по функциональному назначению делятся на шесть групп (см. На рис. 15 схему команд мп кр580вм80):

- •2.. 00000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000003. Программная реализация временной задержки

- •4. Выполнение индивидуальных заданий по составлению программ

- •2. Конспект лекций.

- •1. Принцип работы бис 580вв55

- •2. Программирование бис 580вв55( по индивидуальным заданиям)

- •3. Формирование управляющего сигнала для внешнего устройства

- •4. Разработка программы «Формирование управляющего сигнала для внешнего устройства» ( по индивидуальным заданиям)

- •2.3. Практическое занятие «Программируемый интервальный таймер бис 580ви53»

- •2. Конспект лекций.

- •1. Принцип работы бис 580ви53

- •2. Программирование бис 580ви53 (по индивидуальным заданиям)

- •3. Формирователь импульсов запуска внешнего устройства с большим периодом повторения импульсов ( общее задание)

- •2.4. Практическое занятие «Организация микропроцессорной системы (мпс)»

- •2. Конспект лекций.

- •1. Шины или линии групповой связи

- •2. Разработка схемы управления мпс и организация связей между бис мпс

- •Литература

2. Синтез полусумматора

ЗАДАЧА 2 (общая для всех курсантов). Построить полусумматор на любых логических элементах. Полусумматор – цифровое устройство, формирующее на выходах P, S двоичный код арифметической суммы двух одноразрядных двоичных чисел А и В.

3. Синтез одноразрядного сумматора

ЗАДАЧА 3 (общая для всех курсантов). Построить одноразрядный сумматор на любых логических элементах. Одноразрядный сумматор – цифровое устройство, формирующее на выходах P2, S двоичный код арифметической суммы трех одноразрядных двоичных чисел А, В и Р1.

1.4. Практическое занятие «Элементы цифровых устройств»

Учебные цели

Получение практических навыков в исследовании логических элементов и триггеров.

Содержание занятия

-

Теоретическое исследование реакции триггеров на входные сигналы заданной формы.

2. Теоретическое исследование реакции цифровых устройств на входные сиг-

налы заданной формы.

Учебно–материальное обеспечение занятия

Литература

-

Ицхоки Я.С., Овчинников Н.И., Поздняков В.Г. Импульсные и цифровые устройства. – М.: ВВИА, 1983. – С . 33 – 34.

-

Конспект лекций.

Содержание учебных вопросов

-

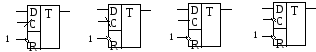

Теоретическое исследование реакции триггеров на входные сигналы заданной формы

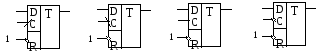

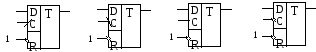

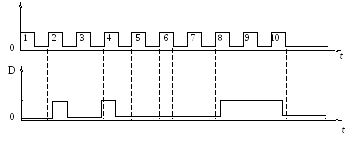

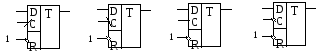

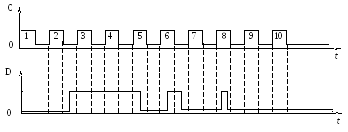

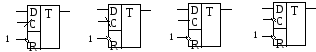

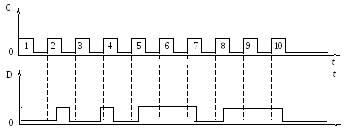

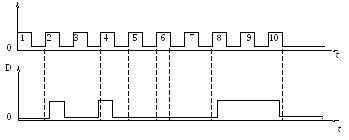

ЗАДАНИЕ: проведите теоретическое исследование реакции триггеров на входные сигналы заданной формы (рис. 11 – 15), а именно: нарисуйте согласованные по времени диаграммы напряжений на выходах Q триггеров .

П

Q1

Q2

Q3

Q4

C

t

0

D

1 2 3

4 5 6 7 8 9

10

t

0

Q1

0

Q2

0

Q3

0

Q4

0

t

t

t

t

В

Q1

Q2

Q3

Q4

Рис.11

В

Q1

Q2

Q3

Q4 ариант

№ 2

ариант

№ 2

С

Рис.12

Вариант № 3

Q1

Q2

Q3

Q4

Рис.13

В

Q1

Q2

Q3

Q4

t

Вариант № 5

Q1

Q2

Q3

Q4

D

C

R T

D

C R T

1

D

C R T

1

D

C

R T

1

1

С

Рис.15

Рис.15