Shamrov_M_I_Telnov_G_G_Organizatsia_ustroystv_na_baze_protsessorov_maloy_razryadnosti

.pdfМОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ |

|

МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ |

ПУТЕЙ СООБЩЕНИЯ (МИИТ) |

|

ПУТЕЙ СООБЩЕНИЯ (МИИТ) |

Институт управления и информационных технологий |

|

Институт управления и информационных технологий |

|

|

|

Кафедра «Вычислительные системы и сети» |

|

Кафедра «Вычислительные системы и сети» |

М.И. ШАМРОВ, Г.Г. ТЕЛЬНОВ |

|

М.И. ШАМРОВ, Г.Г. ТЕЛЬНОВ |

ОРГАНИЗАЦИЯ УСТРОЙСТВ НА БАЗЕ |

|

ОРГАНИЗАЦИЯ УСТРОЙСТВ НА БАЗЕ |

ПРОЦЕССОРОВ МАЛОЙ РАЗРЯДНОСТИ |

|

ПРОЦЕССОРОВ МАЛОЙ РАЗРЯДНОСТИ |

ДЛЯ ИНФОРМАЦИОННЫХ СИСТЕМ |

|

ДЛЯ ИНФОРМАЦИОННЫХ СИСТЕМ |

НА ЖЕЛЕЗНОДОРОЖНОМ ТРАНСПОРТЕ |

|

НА ЖЕЛЕЗНОДОРОЖНОМ ТРАНСПОРТЕ |

|

|

Рекомендовано |

Учебное пособие |

|

Учебно-методическим объединением |

|

|

в качестве учебного пособия для студентов вузов |

|

|

железнодорожного транспорта |

МОСКВА – 2007

МОСКВА – 2007

УДК 681.3 Ш 19

Шамров М.И., Тельнов Г.Г. Организация устройств на базе процессоров малой разрядности для информационных систем на железнодорожном транспорте: Учебное пособие. – М.: МИИТ, 2007. – 160 с.

Учебное пособие предназначено для изучения организации и функционирования устройств на базе процессоров малой разрядности, используемых в различных информационных системах на железнодорожном транспорте и в промышленности. Включает теоретический материал и циклы лабораторных работ. В качестве лабораторного оборудования используется микроЭВМ «Учебный микропроцессорный комплект» на базе микросхем серии К580.

Предназначено для студентов, обучающихся по специальностям направления «Информатика и вычислительная техника», специальности «Вычислительные машины, комплексы, системы и сети». Может быть использовано в дисциплинах «Организация ЭВМ и систем», «Информационные системы и технологии на железнодорожном транспорте», «Микропроцессорные системы», «Архитектура вычислительных систем», «Системы реального времени» и других.

Рецензенты:

Первый заместитель директора ВНИИАС МПС России доктор технических наук, профессор Е.Н.Розенберг

Проректор РГОТУПС, доктор технических наук, профессор В.Ю.Горелик

© Московский государственный университет путей сообщения (МИИТ), 2007

– 3 –

ВВЕДЕНИЕ

Внастоящее время значительное число задач управления техническими объектами, используемыми на железнодорожном транспорте, не требует применения процессоров большой разрядности. Поэтому большая часть подобных задач может быть решена с помощью 8-разрядных однокристальных микроконтроллеров. Современный микроконтроллер может быть достаточно сложным устройством, поэтому основные принципы построения систем малой разрядности можно изучать на примере 8-разрядных микропроцессорных систем.

Внастоящем учебном пособии подробно описывается микроЭВМ «Учебный микропроцессорный комплект» (УМК), предназначенная для изучения принципов построения систем на однокристальных 8-разрядных микропроцессорах. Приведены как описание взаимодействия пользователя с УМК, необходимое для отладки программ, так и особенности аппаратной реализации микропроцессорной системы.

Приведенные особенности аппаратной реализации позволяют глубоко изучить принципы построения систем на используемой в УМК элементной базе. Представленная в учебном пособии реализация различных режимов исполнения программы позволяет довести знания студента до уровня, необходимого разработчику систем.

Настоящее учебное пособие содержит теоретические сведения о системах на процессорах малой разрядности, примеры реализации узлов таких систем и задания для самостоятельного выполнения с помощью УМК.

–4 –

1.ОБЩИЕ СВЕДЕНИЯ

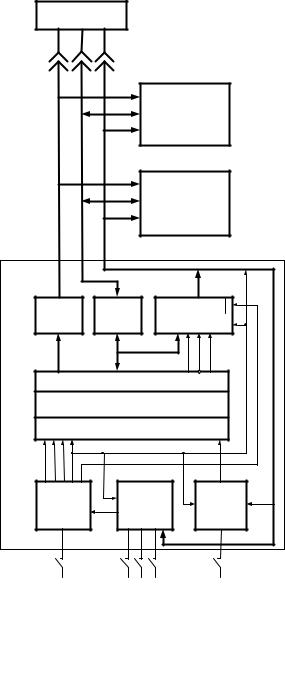

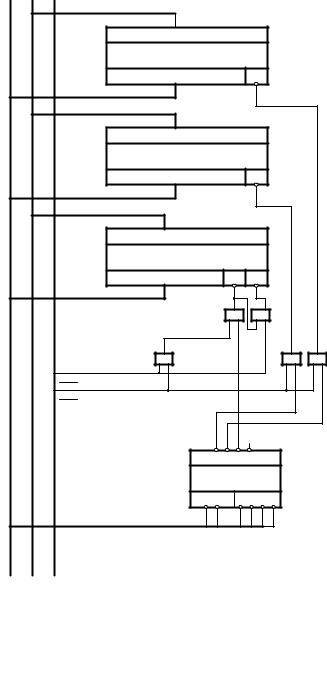

УМК представляет собой простейшую микроЭВМ, построенную на базе микропроцессора К580ВМ80. Укрупненная структурная схема УМК представлена на рис. 1. В состав УМК входят следующие основные блоки, соединенные внутрисистемной магистралью:

−процессор на основе однокристального микропроцессора К580ВМ80 со схемами обрамления;

−память для хранения системных и пользовательских программ и данных, выполненная на базе БИС ПЗУ и ОЗУ;

−блок ввода-вывода, состоящий из клавиатуры, линейного дисплея на семисегментных индикаторах и светодиодных индикаторов состояния.

В свою очередь, в процессоре можно выделить:

−микропроцессор К580ВМ80;

−схему синхронизации и начальной установки на базе БИС К580ГФ24;

−схему управления режимами работы процессора (непрерывный, покомандный, поцикловый);

−блок прерываний для организации прерывания программ пользователя при нажатии клавиши ПР;

−однонаправленный буфер адреса и двунаправленный буфер данных для увеличения нагрузочной способности шин;

−системный контроллер для формирования управляющих сигналов процессора на основе слова состояния машинного цикла.

Информацию по микропроцессорному комплекту К580 можно найти в учебной литературе [1–9], справочниках [10–13], и методических указаниях [14–16].

– 5 –

Рис. 1. Структурная схема УМК

– 6 – |

– 7 – |

К УМК через разъем может быть подключен один из сменных блоков, выполненных в виде печатных плат и предназначенных для введения в УМК дополнительных устройств.

Подключение и отключение сменных блоков можно выполнять только при выключенном питании.

Обмен информацией между процессором и другими блоками УМК осуществляется с помощью 16-разрядной шины адреса A[15-0], двунаправленной 8-разрядной шины данных D[7-0] и шины управления. Перечень всех сигналов шины управления приведен в табл. 1.

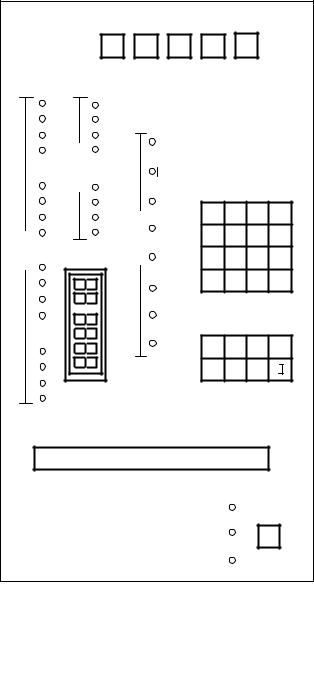

Внешний вид передней панели УМК приведен на рис. 2. Светодиоды «АДРЕС» и «ДАННЫЕ» указывают состояние соответственно шин адреса (А) и данных (D) микропроцессора, а светодиоды «СОСТОЯНИЕ» указывают разряды слова состояния машинного цикла (см. табл. 1). Светодиодные индикаторы функционируют только в пошаговом режиме. Директивные и информационные клавиши используются для ввода директив монитора, программ пользователя и другой информации. Информация, в том числе содержимое памяти, выдается монитором на 6-разрядный дисплей в шестнадцатеричной форме. Клавиши СБ, ПР, РБ/ШГ, КМ/ЦК, ШГ используются только для задания различных режимов работы процессора. Курсивом на рис. 2 приведены надписи, отсутствующие на передней панели УМК.

Включение УМК осуществляется нажатием клавиши «~». При нормальной работе источника питания индикаторы +5В, –5В, +12В погашены. Горящий светодиод указывает на аварию соответствующей цепи питания. Повторное включение УМК

после выключения допускается только при погашенных индикаторах.

Рис. 2. Вид передней панели УМК

– 8 –

Таблица 1

Управляющие сигналы УМК

Источник |

|

Обозначение |

Пояснения |

||||||

сигнала |

англ. |

|

рус. |

||||||

|

|

||||||||

|

|

|

|

|

|

|

|

Сигнал подтверждения |

|

|

ST0 |

INTA |

ППР |

прерывания. Используется для |

|||||

|

помещения на шину данных |

||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

команды RST |

|

|

ST1 |

|

|

|

|

|

|

Указывает, что в текущем |

|

цикла |

|

WO |

|

|

ЗПВ |

|

машинном цикле выполняется |

||

|

|

|

|

|

|

|

запись в память или вывод в порт |

||

|

|

|

|

|

|

|

|

||

машинного |

ST2 |

STACK |

СТЕК |

Указывает, что в текущем |

|||||

(по команде HLT) |

|||||||||

|

машинном цикле выполняется |

||||||||

|

|

|

|

|

|

|

|

обращение к стеку |

|

|

ST3 |

HLTA |

ПОСТ |

Сигнал подтверждения останова |

|||||

|

|

|

|

|

|

|

|

|

|

состояния |

ST4 |

OUT |

ВЫВ |

Указывает, что в текущем |

|||||

Указывает, что в текущем |

|||||||||

|

машинном цикле выполняется |

||||||||

|

|

|

|

|

|

|

|

вывод в порт |

|

Слово |

ST5 |

|

M1 |

ВЫБ |

машинном цикле выполняется |

||||

|

|

|

|

|

|

|

чтение первого байта команды |

||

|

|

|

|

|

|

|

|

||

|

ST6 |

|

INP |

|

ВВ |

Указывает, что в текущем |

|||

|

|

|

машинном цикле выполняется |

||||||

|

|

|

|

|

|

|

|

ввод из порта |

|

|

ST7 |

MEMR |

ЧТП |

Указывает, что в текущем |

|||||

|

машинном цикле производится |

||||||||

|

|

|

|

|

|

|

|

чтение из памяти |

|

|

|

SYNC |

СИНХР |

Идентифицирует начало |

|||||

Микро- |

машинного цикла (на шине D |

||||||||

|

|

|

|

|

|

в это время – слово состояния) |

|||

процессор |

|

|

|

|

|

|

|||

INTE |

РПР |

Указывает на то, что прерывания |

|||||||

|

|

||||||||

|

|

|

|

|

|

|

|

по входу INT разрешены |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 9 – |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Продолжение табл. 1 |

|

|

|

|

|

|

Обозначение |

|

|||||||||||||||||

Источник |

|

|

|

|

|

Пояснения |

||||||||||||||||||

сигнала |

|

|

|

|

англ. |

|

|

|

|

рус. |

||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Указывает на выдачу байта |

|

|

|

|

|

|

WR |

|

|

|

|

ЗП |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

на шину D из микропроцессора |

||||||||||||||

Микро- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DBIN |

|

|

|

|

|

ЧТ |

Указывает на прием байта |

||||||||||||||

процессор |

|

|

|

|

|

|

|

|

с шины D в микропроцессор |

|||||||||||||||

|

|

|

HLDA |

|

ПЗХВ |

Подтверждение состояния |

||||||||||||||||||

|

|

|

|

захвата |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HOLD |

|

|

|

|

ЗХВ |

Запрос захвата шин |

|||||||||||||||

|

|

|

|

|

|

|

(к микропроцессору) |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Внешние |

|

|

|

|

INT |

|

|

|

|

ЗПР |

Запрос прерывания |

|||||||||||||

|

|

|

|

|

|

|

|

(к микропроцессору) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

схемы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

— |

Входной сигнал сброса |

||||||

|

|

RESIN |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

(к генератору) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RDYIN |

|

|

|

|

|

— |

Входной сигнал готовности |

||||||||||||||||

|

|

|

|

|

|

(к генератору) |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

СБРОС |

Сигнал начальной установки |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(сброса) |

|

READY |

|

|

|

|

|

ГТ |

Сигнал готовности |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб фиксации в системном |

|

|

STSTB |

СТРОБ |

|||||||||||||||||||||

Генератор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

контроллере слова состояния |

|

|

|

|

|

F2 |

Ф2ТТЛ |

Синхросигнал Ф2 уровня ТТЛ |

|||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

OSC |

|

|

|

|

|

— |

Сигнал с частотой кварцевого |

||||||||||||

|

|

|

|

|

|

|

|

|

|

резонатора (в 9 раз больше F2) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ф1, Ф2 |

Ф1, Ф2 |

Сигналы синхронизации |

|||||||||||||||||||

|

|

|

микропроцессора (0…+12 В) |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб чтения из памяти |

|

|

|

MRDC |

|

|

|

|

|

ЧТП |

|

|

|

||||||||||||

Системный |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб записи в память |

||

|

MWTC |

|

|

|

ЗПП |

|||||||||||||||||||

контроллер |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб чтения из порта |

||||

|

|

|

|

IORC |

|

|

|

|

|

|

ЧТВВ |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Строб записи в порт |

|||||

|

|

|

IOWC |

|

ЗПВВ |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

– 10 – |

– 11 – |

2. УСТРОЙСТВО И ПРИНЦИПЫ РАБОТЫ УМК

2.1. Процессор УМК

Сброс УМК в начальное состояние осуществляется при нажатии клавиши СБ. При этом управляющие триггеры всех блоков процессора устанавливаются в исходное состояние, а в программный счетчик микропроцессора загружается код 0000H. Сигнал сброса формируется БИС К580ГФ24, составляющей схему синхронизации и начальной установки. Эта же схема формирует

синхросигналы Ф1, Ф2 (амплитудой 12 В), сигнал СТРОБ(STSTB ) загрузки слова состояния машинного цикла в регистр системного контроллера (СК) и сигнал готовности ГТ(READY), используемый обычно при операциях с медленно функционирующими блоками, а в УМК – для организации пошаговых режимов. Длительность такта (период синхросигналов Ф1, Ф2 амплитудой 12 В, а также F2, амплитудой 5 В) у разных УМК может различаться и составляет примерно 600 нс.

В начале каждого машинного цикла на шину данных выдается слово состояния машинного цикла, используемое в СК для расширения шины управления микропроцессора. Сигналы управления на выводах микропроцессора, которые могут изменяться в каждом такте, дополняются сигналами с СК, которые могут изменяться один раз за машинный цикл.

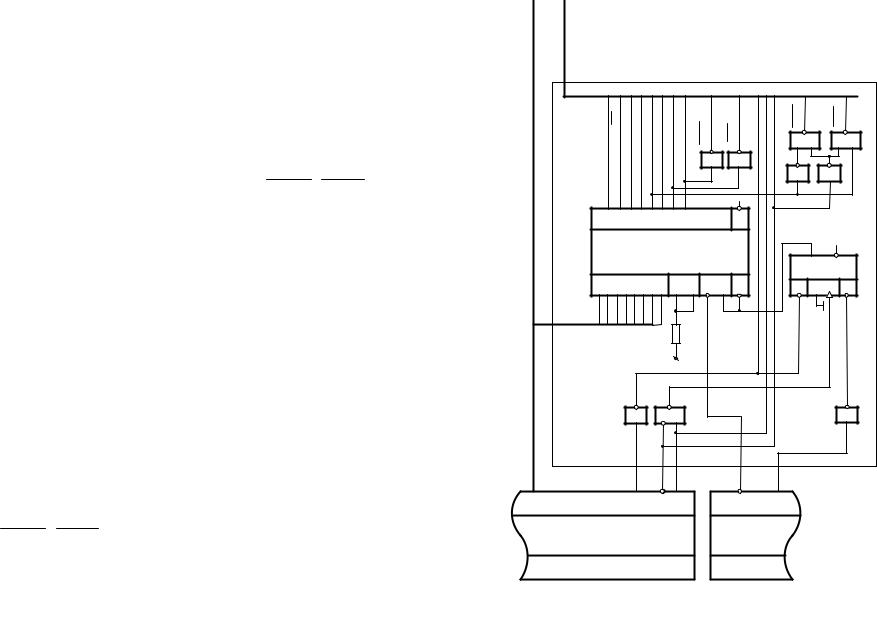

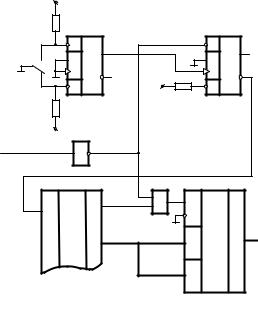

Схема блока СК представлена на рис. 3. Основу схемы составляют многорежимный буферный регистр К589ИР12. Запись слова состояния в регистр осуществляется по нулевому уровню

сигнала СТРОБ(STSTB ) из схемы синхронизации и начальной установки. Сброс регистра в нулевое состояние выполняется либо по сигналу СБРОС(RESET), либо по окончании действия сигналов

Рис. 3. Системный контроллер УМК

– 12 –

ЗП ( WR ) или ЧТ(DBIN) из микропроцессора, что обычно означает завершение машинного цикла.

Процессор УМК может работать в одном из трех режимов:

−непрерывный (клавиша РБ/ШГ в положении РБ);

−покомандный (клавиша РБ/ШГ в положении ШГ, клавиша КМ/ЦК в положении КМ);

−поцикловый (клавиша РБ/ШГ в положении ШГ, клавиша КМ/ЦК в положении ЦК).

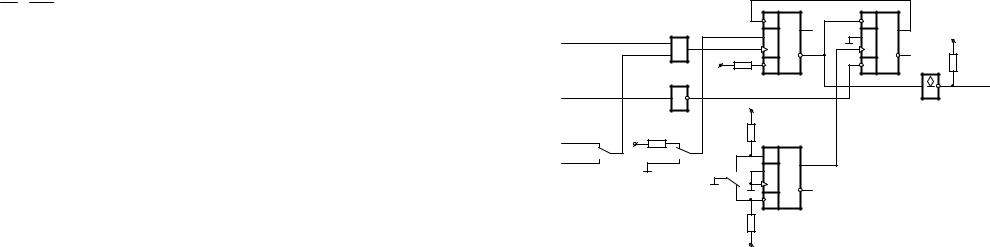

Реализация режимов осуществляется схемой управления режимами, фрагмент которой показан на рис. 4. Схема вырабатывает сигнал RDYIN для БИС К580ГФ24. Сигнал RDYIN стробируется синхросигналом и передается на выход READY, откуда поступает на вход READY микропроцессора.

После сброса в исходном состоянии Т1=1, Т2=1. Непрерывный режим задается переключением клавиши РБ/ШГ в положение РБ. При этом на вход D триггера Т1 подается единица, триггер сохраняет единичное состояние и выдается сигнал готовности

RDYIN=1.

Пошаговые режимы (покомандный и поцикловый) реализуются при переключении клавиши РБ/ШГ в положение ШГ. При этом на вход D триггера Т1 подается нуль. На вход С этого триггера

взависимости от положения клавиши КМ/ЦК подается либо сигнал ВЫБ(М1), указывающий на начало исполнения команды, либо сигнал СИНХР(SYNC), вырабатываемый в каждом машинном цикле. Эти сигналы переводят триггер Т1 в нулевое состояние (исходное состояние Т1=1, Т2=1), что приводит к выдаче в микропроцессор сигнала RDYIN=0, по которому он после второго такта текущего машинного цикла переходит в состояние ожидания.

– 13 –

Бит программного запрета пошаговых режимов

RESET

M1 КМ +5В

SYNC

ЦК

S T |

S T |

|

D |

|

D |

+5В |

& |

|

|

||

C |

|

C |

|

|

|

|

|

||

|

+5В |

T1 |

R |

T2 |

|

R |

|||

|

|

|

|

RDYIN |

1 |

|

|

|

|

|

+5В |

|

|

|

РБ

S T

S T

ШГ |

|

D |

|

|

|

|

ШГ |

C |

|

R |

|

|

|

|

|

|

+5В |

Рис. 4. Схема организации пошаговых режимов УМК

При нажатии клавиши ШГ триггер Т2 переключается в нулевое состояние, Т1 устанавливается в единицу и вырабатывается сигнал RDYIN=1 с возвращением триггера Т2 в состояние 1.

Таким образом, при установке клавиши КМ/ЦК в положение КМ, по нажатию клавиши ШГ исполняется одна команда (один период сигнала ВЫБ(М1)), а при установке в положение ЦК – один машинный цикл (один период сигнала СИНХР(SYNC)). При переходе из пошагового режима в непрерывный после перевода клавиши РБ/ШГ в положение РБ необходимо однократное нажатие клавиши ШГ: только после этого вырабатывается сигнал RDYIN=1.

В момент останова процессора на светодиодах «АДРЕС», «ДАННЫЕ», «СОСТОЯНИЕ» присутствуют сигналы соответствующих шин микропроцессора и слова состояния из СК.

– 14 –

Пошаговые режимы работы процессора разрешаются только при исполнении программ пользователя. С этой целью в схему управления режимами работы введен конъюнктор на входе С триггера Т1. На один из входов этого конъюнктора подается программно устанавливаемый бит запрета пошаговых режимов. Бит подается из младшего разряда порта вывода с адресом 0FCH. При записи в младший разряд этого порта нуля происходит запрет пошаговых режимов сразу после исполнения команды OUT 0FCH. При записи в этот разряд единицы происходит разрешение пошаговых режимов через 6 циклов после исполнения команды OUT 0FCH. Схема, организующая задержку в 6 циклов, на рис. 4 не показана. Задержка в 6 циклов необходима при запуске программы пользователя в пошаговом режиме. При этом первый останов после запуска программы всегда происходит в программе пользователя (а не в мониторе). При переходе в программу монитора пошаговые режимы запрещаются.

Краткое описание системы команд микропроцессора К580ВМ80 приведено в приложении А.

2.2. Память УМК

Память УМК состоит из ПЗУ программ монитора, резервного ПЗУ и ОЗУ. Программы пользователя могут быть занесены в ОЗУ по адресам с 0800Н по 0ВС9Н. При использовании других адресов ОЗУ нарушается работа монитора. Указатель стека пользователя инициализируется значением 0ВСАН. Это означает, что стек пользователя расположен начиная с адреса 0ВС9Н в сторону уменьшения адресов. Таким образом, использовать старшие адреса ОЗУ пользователя следует с осторожностью, поскольку они

– 15 –

используются для размещения стека пользователя. Адреса памяти УМК приведены в табл. 2.

Схема организации памяти УМК приведена на рис. 5. Адреса ПЗУ и ОЗУ задаются дешифратором DC. ПЗУ монитора и резервное ПЗУ реализованы на перепрограммируемых ПЗУ с ультрафиолетовым стиранием типа К573РФ1. Чтение из ПЗУ разрешается при наличии разрешающего уровня на соответствующем выходе DC по сигналу ЧТП(MEMR)=1 из седьмого разряда регистра СК.

Чтение из ОЗУ допускается при наличии разрешающего уровня на соответствующем выходе DC при ЧТП(MEMR)=1,

MRDC =0 (при этом сигнал разрешения записи в ОЗУ WR =1, так как сигнал ЗП ( WR ) из микропроцессора равен 1 и, следовательно,

MWTC =1).

Запись в ОЗУ допускается при ЧТП(MEMR)=0, ЗП ( WR )=0, ВЫВ(OUT)=0 и нуле на соответствующем выводе дешифратора.

|

|

|

|

|

Таблица 2 |

|

|

|

Адреса памяти УМК |

|

|

|

Тип памяти |

|

|

|

|

|

Объем (в байтах) |

|

Адрес |

||

|

ПЗУ монитора |

1 К |

|

0000H–03FFH |

|

|

ПЗУ резервное |

1 К |

|

0400H–07FFH |

|

|

ОЗУ |

пользователя |

970 |

|

0800H–0BC9H |

|

монитора |

54 |

|

0BCAH–0BFFH |

|

– 16 –

Рис. 5. Память УМК

–17 –

2.3.Организация прерываний в процессоре УМК

Для организации прерываний в системе на основе микропроцессора К580ВМ80 необходимо, чтобы на вход ЗПР(INT) микропроцессора был подан единичный уровень сигнала. Запрос обычно поступает на вход микропроцессора со специальной схемы

– блока прерываний, получающей запросы от различных источников. Далее в случае, если прерывания разрешены (выход РПР(INTE)=1), при чтении очередной команды происходит следующее:

−в словах состояния машинного цикла вместо сигнала ЧТП(MEMR) вырабатывается сигнал ППР(INTA) – ЧТП(MEMR)=0,

ППР(INTA)=1;

−запрещается увеличение программного счетчика;

−происходит запрет прерываний.

Если считываемая команда многобайтная, первые два пункта выполняются для циклов чтения каждого байта команды. Выдача сигнала ППР(INTA) вместо ЧТП(MEMR) позволяет считывать не очередную команду из памяти, а команду, выдаваемую блоком прерываний. В качестве основы блока прерываний обычно используется один из трех типов микросхем: контроллер прерываний К580ВН59, выдающий команду CALL, блок приоритетных прерываний К589ИК14, выдающий команду RST или системный контроллер К580ВК28(ВК38), который без дополнительных схем может самостоятельно выдать команду RST 7. Запрет увеличения программного счетчика необходим для правильной организации возврата из подпрограммы обработки прерывания к команде, на которую программный счетчик указывал до прерывания (до считывания команды со схемы прерывания). Автоматический

– 18 –

запрет прерываний необходим для того, чтобы не возникло бесконечной цепочки прерываний от одного запроса. Прерывания в дальнейшем могут быть разрешены в подпрограмме обработки прерывания командой EI.

Блок прерываний УМК предназначен для организации прерывания пользовательской программы при нажатии клавиши ПР. Прерывание выполняется путем подстановки на шину данных вместо очередной команды, адресуемой из программного счетчика, команды RST 7. Такое прерывание можно назвать внешним. В системе возможны также программные прерывания – в этом случае команда RST 7 должна находиться в программе пользователя. При программном прерывании блок прерываний не используется, а просто исполняется команда RST 7, эквивалентная команде

CALL 0038Н.

Прерывание уровня 7 – единственно возможное прерывание в УМК. В подпрограмме обработки прерываний осуществляется запрет пошаговых режимов и передача управления монитору с сохранением состояния всех регистров микропроцессора в специальной области ОЗУ монитора. Это дает пользователю возможность просмотра всех регистров с помощью вызова соответствующей директивы монитора. После прерывания на дисплей выдается содержимое программного счетчика (адрес команды, с которой можно продолжить исполнение программы пользователя) и приглашение монитора к вводу директив. Более подробно действия подпрограммы обработки прерываний уровня 7, находящейся начиная с адреса 0038Н, описаны в разд. 3.3.

Блок прерываний УМК приведен на рис. 6. В исходном состоянии ТПР=1. При нажатии клавиши ПР триггер ТПР переходит в нулевое состояние. Единичный сигнал с инверсного

– 19 –

выхода ТПР подается на вход ЗПР(INT) микропроцессора, что вызывает в первом машинном цикле очередной команды выдачу слова состояния машинного цикла в регистр СК с сигналом ППР(INTA) вместо ЧТП(MEMR): ППР(INTA)=1, ЧТП(MEMR)=0.

Сигнал ППР(INTA) из СК возвращает ТПР в состояние 1 и одновременно запрещает перевод буфера данных, реализованного на микросхемах К589АП16, в режим ввода. При этом вместо очередной команды, адресуемой по шине адреса из программного счетчика, в микропроцессор по сигналу ЧТ(DBIN) вводится код «все единицы» (0FFH), являющийся командой RST 7. В нормальном режиме работы микропроцессора (ППР(INTA)=0) буфер данных при ЧТ(DBIN)=1 настраивается на ввод.

Рис. 6. Блок прерываний УМК