Shamrov_M_I_Telnov_G_G_Organizatsia_ustroystv_na_baze_protsessorov_maloy_razryadnosti

.pdf

– 60 –

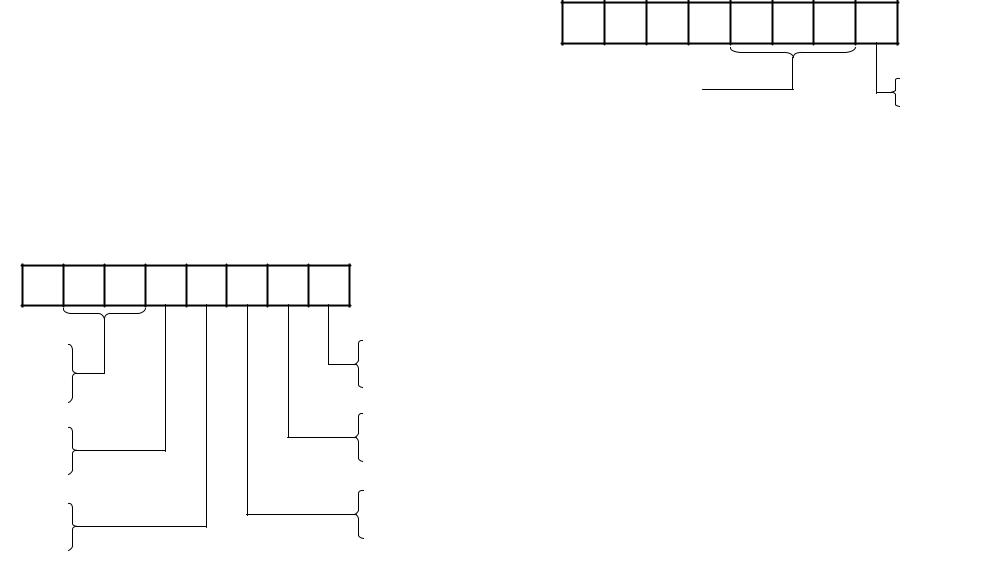

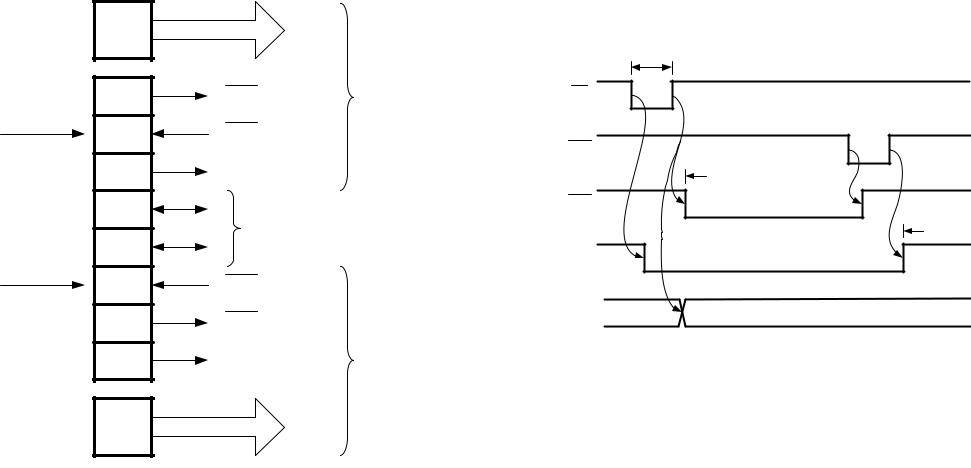

Настройка ППИ на выполнение различных типов операций ввода-вывода осуществляется путем загрузки регистра управляющего слова. На рис. 15 приведен формат управляющего слова настройки каналов ППИ для обмена в различных режимах (D7=1).

Возможна организация трех режимов обмена: 0, 1, 2. По сигналу RESET все каналы настраиваются на ввод в режиме 0.

На рис. 16 приведен формат управляющего слова для установки отдельных разрядов канала С (D7=0). Номер устанавливаемого бита задается разрядами D3–D1, а устанавливаемое значение – в разряде D0. Такое управляющее слово введено для удобства изменения отдельных разрядов канала С, особенности которого описаны ниже.

Рис. 15. Формат управляющего слова выбора режимов ППИ

– 61 –

Рис. 16. Формат управляющего слова для установки отдельных разрядов канала С

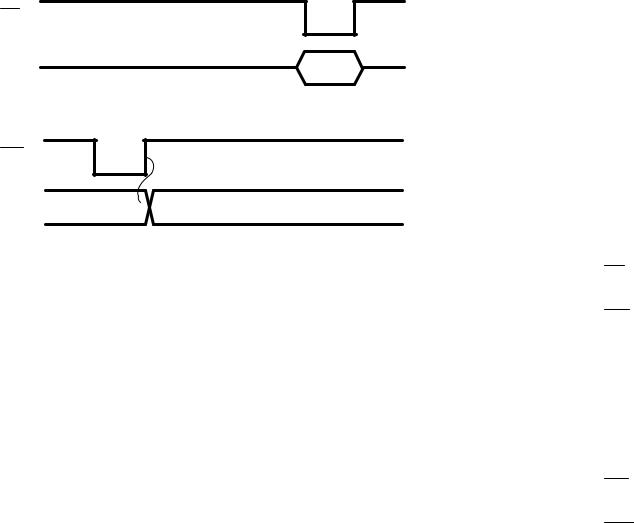

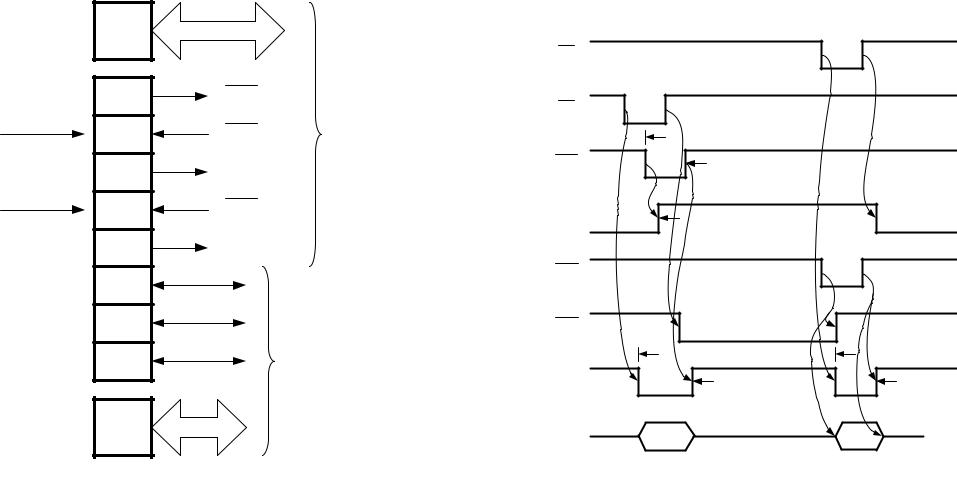

Врежиме 0 обмен между каналами ППИ и периферийными устройствами осуществляется без дополнительных сигналов, стробирующих обмен. В этом случае ППИ может рассматриваться как устройство, состоящее из четырех портов: два 4-разрядных РС3–РС0, РС7–РС4 и два 8-разрядных РА7–РА0, РВ7–РВ0. (Канал

Симеет смысл рассматривать как два раздельных 4-разрядных порта только при их различной настройке: один на ввод, другой на вывод.) Вывод осуществляется командой OUT с фиксацией выдаваемой информации в регистрах каналов. Ввод информации осуществляется командой IN без фиксации в регистрах каналов (происходит только передача данных, поданных на вход соответствующего канала на шину D7–D0). Возможен ввод информации, предварительно выведенной в порты. Временные диаграммы функционирования ППИ в режиме 0 приведены на рис. 17, 18.

Врежиме 1 ППИ обеспечивает стробируемый однонаправленный обмен информацией между каналами ППИ и периферийными устройствами. В этом режиме могут работать каналы А и В, а для передачи управляющих сигналов используются по три линии канала С.

– 62 –

RD

PA7-PA0,

PB7-PB0, данные PC7-PC0

Рис. 17. Временная диаграмма ввода в режиме 0

WR

PA7-PA0,

PB7-PB0,  данные PC7-PC0

данные PC7-PC0

Рис. 18. Временная диаграмма вывода в режиме 0

При этом остальные линии канала С могут быть настроены на ввод или вывод в режиме 0. В качестве управляющих сигналов для каждого из каналов А и В используются три сигнала:

−сигнал готовности передающего устройства (периферийного устройства при вводе или канала при выводе) к выдаче информации;

−сигнал подтверждения приема информации от принимающего устройства (канала при вводе или периферийного устройства при выводе);

−сигнал прерывания, информирующий микропроцессор о завершении операции ввода-вывода и готовности канала ППИ к чтению принятого байта командой IN (при вводе) или готовности канала ППИ к приему от микропроцессора по команде OUT очередного байта для передачи периферийному устройству (при выводе). Сигнал прерывания вырабатывается в ППИ при

– 63 –

установленном в единицу сигнале разрешения прерывания от соответствующего канала. Сигнал разрешения берется из фиксированного разряда канала С, который устанавливается с помощью управляющего слова побитной установки (см. рис. 16).

Сигналы готовности, подтверждения и запроса на прерывание вырабатываются ППИ автоматически. Предусмотрена возможность чтения их из канала С командой IN для последующего программного анализа.

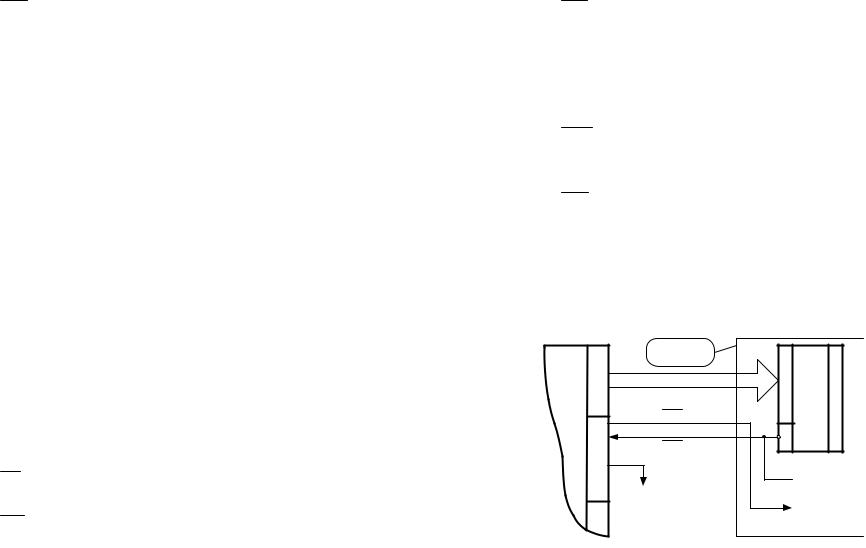

Пример использования ППИ для вывода в режиме 1 показан на рис. 19. Назначение выводов ППИ в режиме 1 представлено на рис. 20, 22. Временные диаграммы функционирования ППИ в режиме 1 приведены на рис. 21, 23. Сигналы, приведенные на временной диаграмме ввода в режиме 1 (см. рис. 21):

−RD – сигнал чтения из ППИ (см. табл. 6). Выдается микропроцессором при исполнении команды IN;

−STB (Strobe) – сигнал выдачи данных периферийным устройством;

−IBF (Input Buffer Full) – сигнал подтверждения приема данных от ППИ;

−INTR (Interrupt Request) – запрос на прерывание микропроцессору.

Сигналы, приведенные на временной диаграмме вывода в режиме 1 (см. рис. 23):

−WR – сигнал записи в ППИ (см. табл. 6). Выдается микропроцессором при исполнении команды OUT;

−ACK (Acknowledge) – сигнал подтверждения приема от периферийного устройства;

–64 –

−OBF (Output Buffer Full) – сигнал готовности к выдаче данных от ППИ;

−INTR (Interrupt Request) – запрос на прерывание микропроцессору.

Режим 1 позволяет организовать между ППИ и периферийным устройством асинхронный обмен с квитированием.

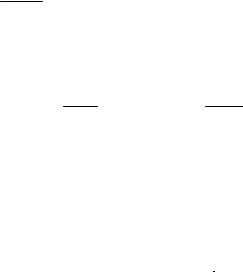

В режиме 2 ППИ обеспечивает стробируемый двунаправленный обмен данными между каналом ППИ и периферийным устройством. В этом режиме может работать только канал А, а для передачи управляющих сигналов используется пять линий канала С. Канал В и оставшиеся три линии канала С могут работать в режимах 0, 1. Режим 2 отличается от режима 1 тем, что операции ввода и вывода через канал могут чередоваться в произвольном порядке без перенастройки канала. Возможен, например, прием байта данных от периферийного устройства (операция ввода) и затем запись байта данных в тот же канал ППИ командой OUT (операция вывода). Для одновременного хранения вводимых и выводимых байт, канал А ППИ имеет два внутренних регистра данных. Назначение выводов ППИ в режиме 2 представлено на рис.

24.Временные диаграммы функционирования ППИ в режиме 2 приведены на рис. 25.

Сигналы, приведенные на временной диаграмме вводавывода в режиме 2 (см. рис. 25):

−RD – сигнал чтения из ППИ (см. табл. 6). Выдается микропроцессором при исполнении команды IN;

−WR – сигнал записи в ППИ (см. табл. 6). Выдается микропроцессором при исполнении команды OUT;

–65 –

−STB (Strobe) – сигнал выдачи данных периферийным устройством при операции ввода (источник сигнала – периферийное устройство);

−IBF (Input Buffer Full) – сигнал подтверждения приема данных ППИ от периферийного устройства при операции ввода (источник сигнала – ППИ);

−ACK (Acknowledge) – сигнал подтверждения приема данных периферийным устройством от ППИ при операции вывода (источник сигнала – периферийное устройство);

−OBF (Output Buffer Full) – сигнал готовности ППИ к выдаче данных при операции вывода (источник сигнала – ППИ);

−INTR (Interrupt Request) – общий запрос на прерывание микропроцессору и от ввода и от вывода.

Режим 2 позволяет организовать между ППИ и периферийным устройством двунаправленный асинхронный обмен с квитированием.

Рис. 19. Сопряжение ППИ с периферийным устройством при выводе в режиме 1

Разрешение

прерывания от канала А

Разрешение

прерывания от канала B

PA

PC5

PC4

PC3

PC6

PC7

PC2

PC1

PC0

PB

– 66 –

К

а

н

IBF а

л

STB

А

INTR

Ввод – вывод в режиме 0

STB

IBF |

К |

а |

|

INTR |

н |

а |

|

|

л |

|

B |

Рис. 20. Сигналы ППИ при вводе в режиме 1

– 67 –

Ввод данных в микропроцессор

RD

Данные готовы

Данные готовы

STB |

Окончание передачи данных |

Входной буфер ППИ заполнен

Входной буфер ППИ заполнен

IBF

Запрос на ввод данных микропроцессору

Запрос на ввод данных микропроцессору

INTR

PA7-PA0,  данные

данные

PB7-PB0

Рис. 21. Временная диаграмма ввода в режиме 1

– 68 – |

– 69 – |

Вывод данных из микропроцессора

WR

Данные приняты

Данные приняты

ACK

|

Данные в выходном буфере ППИ |

|

OBF |

|

|

|

Запрос на |

|

|

вывод |

|

INTR |

следующего |

|

байта данных |

||

PA7-PA0, |

данные |

|

PB7-PB0 |

||

|

Рис. 23. Временная диаграмма вывода в режиме 1

Рис. 22. Сигналы ППИ при выводе в режиме 1

– 70 –

Рис. 24. Сигналы ППИ при вводе-выводе в режиме 2

– 71 –

Ввод данных D2 в микропроцессор

RD

Вывод данных D1 из микропроцессора

Вывод данных D1 из микропроцессора

WR

|

Данные D2 готовы |

STB |

Окончание передачи данных D2 |

IBF |

Данные D2 во входном буфере ППИ |

Данные D1 приняты

Данные D1 приняты

ACK

Данные D1 в выходном буфере ППИ

Данные D1 в выходном буфере ППИ

OBF

|

Сброс запроса на вывод D1 |

Сброс запроса на ввод D2 |

INTR |

|

Запрос на вывод |

Запрос на ввод D2 |

следующего после |

|

|

|

D1 байта данных |

PA7-PA0 |

D2 |

D1 |

Рис. 25. Временная диаграмма ввода-вывода в режиме 2

–72 –

6.2.Организация процедур ввода-вывода

сиспользованием ППИ

Для выполнения обмена информацией между периферийными устройствами и процессором через ППИ могут быть использованы два основных способа:

−программно управляемый обмен;

−программно управляемый обмен с прерываниями.

В первом случае между ППИ и периферийным устройством может быть реализован как синхронный обмен, так и асинхронный обмен с квитированием.

Синхронный обмен выполняется без использования стробирующих сигналов (режим 0 ППИ). Обычно этот способ используется для связи с цифровыми датчиками или исполнительными механизмами при использовании микроЭВМ в контуре управления.

Асинхронный обмен с квитированием используется при подключении ППИ к периферийному устройству, вырабатывающему сигналы готовности к выдаче данных в ППИ при операциях ввода или подтверждения приема данных из ППИ при операциях вывода. Формирование аналогичных сигналов в ППИ может быть выполнено программным путем в режиме 0, путем побитной установки разрядов порта С и программного опроса входных сигналов, а также аппаратным путем в режимах 1 и 2 без использования линий запросов на прерывания. Моменты завершения операций ввода-вывода при этом могут быть определены путем программного опроса (поллинга) канала С, в котором состояния управляющих сигналов доступны для считывания командой IN.

– 73 –

Во втором случае, при организации программно управляемого обмена с прерываниями, ППИ может использоваться в режиме 1 или 2. При этом обмен управляющими сигналами между ППИ и периферийным устройством при передаче информации выполняется без участия микропроцессора. В момент завершения операции обмена происходит выдача из ППИ запроса на прерывание микропроцессору. Пример такого использования ППИ – см. рис. 19.

При организации программно управляемого обмена с прерываниями возможна одновременная работа микропроцессора по выполнению основной программы и ППИ, реализующего обмен очередным байтом информации с периферийным устройством. После завершения операции обмена микропроцессор прерывает свою работу по запросу от ППИ и осуществляет переход к программе обработки прерывания. При этом происходит автоматический запрет прерываний в микропроцессоре.

Если запросы прерывания от нескольких каналов объединяются в один, или ППИ функционирует в режиме 2, когда выдается только объединенный запрос прерывания по вводу и выводу, уточнение источника прерывания возможно с помощью программного опроса (поллинга) канала С в подпрограмме обработки прерывания. Далее подпрограмма обработки прерывания считывает из ППИ с помощью команды IN принятые от периферийного устройства данные (при вводе) или записывает в ППИ с помощью команды OUT данные для передачи их периферийному устройству (при выводе). После этого необходимо изменить значение текущего адреса массива данных в памяти, куда записываются вводимые данные или откуда читаются выводимые. Момент окончания всей операции обмена заданным количеством информации проверяется в программе обработки прерывания, например путем проверки на

– 74 –

нуль содержимого счетчика данных, уменьшаемого при каждом исполнении программы на единицу. Перед командой возврата из программы обработки прерывания должна находиться команда разрешения прерываний.

В основной программе для выполнения программно управляемого обмена с прерываниями необходимо установить начальное значение счетчика данных и начальный адрес области данных в памяти микроЭВМ, в который должны быть помещены вводимые данные или из которого должны быть взяты выводимые. После этого необходимо настроить ППИ на требуемый режим работы, в том числе разрешить выдачу сигналов прерывания от соответствующих каналов ППИ. Далее необходимо разрешить прерывания в микропроцессоре (если они запрещены) с помощью команды EI.

Более подробное описание способов организации процедур ввода-вывода через ППИ можно найти, например, в [2, 3].

6.3. Описание платы М2

Лабораторная работа № 5 выполняется с помощью учебной микроЭВМ УМК и платы М2. Плата М2 предназначена для расширения функциональных возможностей УМК:

−подключения периферийных устройств через БИС программируемого параллельного интерфейса К580ВВ55А;

−увеличения объема памяти.

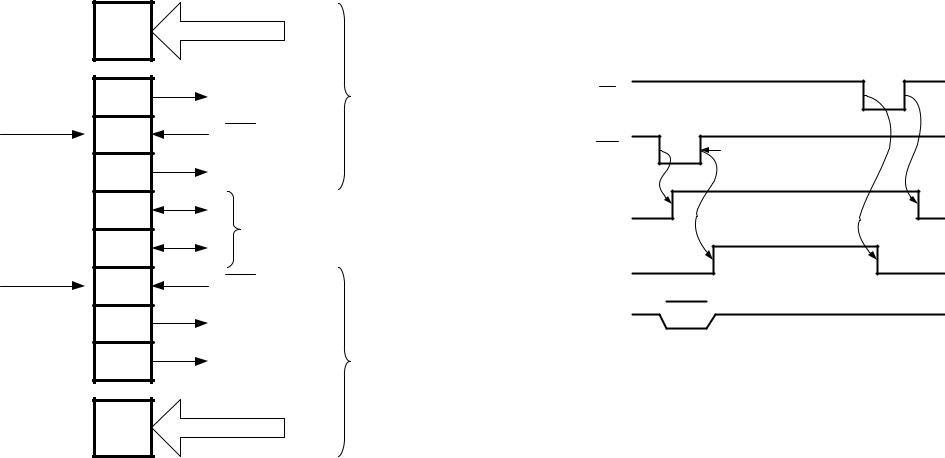

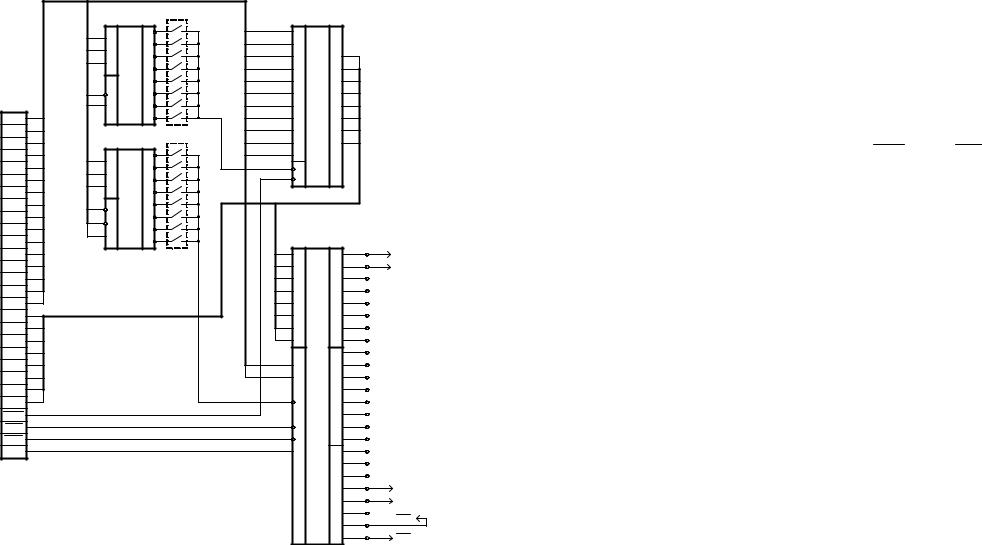

Функциональная схема платы М2 приведена на рис. 26. Увеличение объема памяти достигается подключением к шинам УМК БИС ПЗУ с ультрафиолетовым стиранием емкостью 2К байт (микросхема К537РФ2). Адреса ПЗУ не пересекаются с адресами

– 75 –

внутреннего ОЗУ и ПЗУ УМК и задаются блоком переключателей SA1, подключенным к выходам неполного дешифратора DC1 старших 5 разрядов шины адреса УМК. При включении одного из переключателей соответствующий выход дешифратора подключается к входу выборки ПЗУ. Номера переключателей в блоке SA1 и назначаемые ими диапазоны адресов ПЗУ приведены в табл. 7. Выдача байта из ПЗУ на шину данных УМК разрешается сигналом

MRDC , формируемым в УМК.

Функции ввода-вывода на плате М2 реализуются с помощью БИС ППИ К580ВВ55А. Обмен данными между ППИ и микропроцессором осуществляется через шину данных УМК. Выбор типа операции осуществляется стандартными сигналами УМК: для

чтения – IORC , для записи – IOWC . Начальная установка ППИ выполняется по сигналу RESET. Адресация внутренних регистров ППИ осуществляется сигналами А1, А0 и сигналом выборки ППИ. Входы А1, А0 подключены к соответствующим разрядам шины адреса.

Таблица 7

Назначение адресов ПЗУ

Номер переключателя |

Диапазон адресов |

|

|

|

|

1 |

8000Н – 87FFH |

|

2 |

8800H |

– 8FFFH |

|

|

|

3 |

9000H |

– 97FFH |

|

|

|

4 |

9800H |

– 9FFFH |

5 |

A000H – A7FFH |

|

6 |

A800H – AFFFH |

|

7 |

B000H – B7FFH |

|

8 |

B800H – BFFFH |

|

|

|

|

|

|

|

– 76 – |

|

|

|

|

|

|

|

|

|

|

SA1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

12 |

DC1 |

0 |

|

A0 |

ПЗУ |

|

|

|

|

|

|

|

2 |

|

|

|

|||||

|

|

13 |

X0 |

1 |

|

A1 |

|

|

|

|

|

|

|

X1 |

|

3 |

|

|

|

1 |

|||

|

|

14 |

2 |

|

A2 |

|

D0 |

|

|||

|

|

X2 |

|

4 |

|

|

2 |

||||

|

|

|

3 |

|

A3 |

|

D1 |

|

|||

|

|

|

|

|

|

|

|

3 |

|||

|

|

|

|

4 |

|

5 |

A4 |

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

15 |

& |

5 |

|

6 |

A5 |

|

D3 |

|

4 |

|

|

|

|

|

|

|

|||||

|

|

16 |

|

7 |

|

|

5 |

||||

|

|

V |

6 |

|

A6 |

|

D4 |

|

|||

|

|

|

8 |

|

|

|

6 |

||||

A0 |

1 |

|

|

7 |

8 |

|

|

|

|

||

|

|

|

A7 |

|

D5 |

|

|||||

|

|

|

|

|

|

|

|

||||

A1 |

2 |

|

|

|

|

9 |

A8 |

|

D6 |

|

7 |

|

|

|

|

SA2 |

|

|

|

8 |

|||

A2 |

3 |

|

|

|

10 |

A9 |

|

D7 |

|

||

|

|

|

|

1 |

11 |

|

|

|

|||

|

4 |

|

|

|

|

|

|

|

|

||

A3 |

|

DC2 |

0 |

|

A10 |

|

|

|

|

||

3 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|||||

A4 |

5 |

|

X0 |

1 |

|

|

CS |

|

|

|

|

6 |

4 |

X1 |

|

|

2K x 8 |

|

|

|

|||

A5 |

|

5 |

X2 |

2 |

|

|

OE |

|

|

|

|

7 |

|

|

|

|

|

|

|

||||

A6 |

|

3 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

A7 |

8 |

6 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

A8 |

9 |

7 |

& |

5 |

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

||||

A9 |

8 |

V |

6 |

|

|

|

|

|

|

|

|

11 |

8 |

|

|

|

|

|

|

||||

A10 |

|

|

7 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

1 |

|

|

|

|

||

A11 |

12 |

|

|

|

|

|

ППИ |

|

4 |

A0 |

|

13 |

|

|

|

|

|

D0 |

A0 |

3 |

|||

A12 |

|

|

|

|

|

2 |

|

A1 |

A1 |

||

|

|

|

|

|

|

D1 |

|

|

|||

A13 |

14 |

|

|

|

|

|

3 |

|

A2 |

|

|

|

|

|

|

|

|

D2 |

|

|

|

||

A14 |

15 |

|

|

|

|

|

4 |

|

A3 |

|

|

16 |

|

|

|

|

|

D3 |

|

|

|

||

A15 |

|

|

|

|

|

5 |

|

A4 |

|

|

|

|

|

|

|

|

|

D4 |

|

|

|

||

D0 |

1 |

|

|

|

|

|

6 |

|

A5 |

|

|

|

|

|

|

|

|

D5 |

|

|

|

||

D1 |

2 |

|

|

|

|

|

7 |

|

A6 |

|

|

|

|

|

|

|

|

D6 |

|

|

|

||

D2 |

3 |

|

|

|

|

|

8 |

|

|

|

|

|

|

|

|

|

D7 |

|

A7 |

|

|

||

|

|

|

|

|

|

|

|

|

|||

D3 |

4 |

|

|

|

|

|

|

|

B0 |

|

|

|

|

|

|

|

1 |

|

|

|

|

||

D4 |

5 |

|

|

|

|

A0 |

|

B1 |

|

|

|

|

|

|

|

|

2 |

|

|

|

|||

D5 |

6 |

|

|

|

|

A1 |

|

B2 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

D6 |

7 |

|

|

|

|

|

|

|

B3 |

|

|

8 |

|

|

|

|

|

|

|

|

|

||

D7 |

|

|

|

|

|

CS |

|

B4 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

MRDC |

|

|

|

|

|

|

|

|

B5 |

|

|

IORC |

|

|

|

|

|

|

RD |

|

B6 |

|

|

IOWC |

|

|

|

|

|

|

WR |

|

B7 |

|

|

RESET |

|

|

|

|

|

|

RES |

|

C0 |

|

|

|

|

|

|

|

|

|

|

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

|

|

|

|

|

|

C3 |

17 |

INTR |

|

|

|

|

|

|

|

|

|

C4 |

13 |

PC4 |

|

|

|

|

|

|

|

|

|

C5 |

|

ACK |

|

|

|

|

|

|

|

|

|

C6 |

11 |

|

|

|

|

|

|

|

|

|

|

C7 |

10 |

OBF |

Рис. 26. Функциональная схема платы М2

– 77 –

Адреса внутренних регистров (портов) ППИ задаются блоком переключателей SA2, подключенным к выходам неполного дешифратора DC2 старших 6 разрядов адреса порта УМК. При включении одного из переключателей соответствующий выход дешифратора подключается к входу выборки ППИ. Номера переключателей в блоке SA2 и назначаемые ими диапазоны адресов внутренних регистров (портов) ППИ приведены в табл. 8. Выводы

ППИ РА0(А0), РА1(А1), РС3(INTR), РС4, РС6( ACK ), РС7( OBF )

выведены на контактные площадки для удобства подключения осциллографа.

Таблица 8

Назначение адресов портам ППИ

Номер переключателя |

Диапазон адресов |

1 |

80Н – 83H |

2 |

84H – 87H |

3 |

88H – 8BH |

|

|

4 |

8CH – 8FH |

|

|

5 |

90H – 93H |

|

|

6 |

94H – 97H |

7 |

98H – 9BH |

8 |

9CH – 9FH |

В блоках переключателей SA1 и SA2 переключатель с номером 1 окрашен в темный цвет. Блок переключателей SA1, определяющий адреса ПЗУ, расположен на плате в позиции D1 (при рабочем положении платы находится ниже, чем SA2). Блок переключателей SA2, определяющий адреса портов ППИ, расположен на плате в позиции В2 (при рабочем положении платы

– 78 –

находится выше, чем SA1). Во всех блоках должен быть включен переключатель темного цвета (номер 1). Таким образом, ПЗУ назначаются адреса 8000H–87FFH в адресном пространстве памяти, а портам ППИ – адреса 80H–83H в адресном пространстве портов ввода-вывода. Изменять положение переключателей запрещено.

6.4. Описание платы ПС

Лабораторная работа № 6 выполняется с помощью учебной микроЭВМ УМК и платы ПС. Плата ПС предназначена для расширения функциональных возможностей УМК:

−ввода информации с клавиатуры;

−вывода информации на светодиодную матрицу 5×8;

−увеличения объема памяти.

Функциональная схема платы ПС приведена на рис. 27. Увеличение объема памяти достигается за счет подключения БИС ПЗУ с ультрафиолетовым стиранием К537РФ2. ПЗУ назначены адреса 8000Н–87FFН в адресном пространстве памяти. Портам ППИ назначены адреса 00Н–03Н в адресном пространстве портов ввода-вывода. Изменение указанных адресов невозможно.

Ввод информации от клавиш блока SA осуществляется через канал А ППИ. Обращение к каналу А выполняется по адресу 00Н.

Вывод информации на светодиодную матрицу осуществляется через канал В (адрес 01Н) и канал С (адрес 02Н) ППИ. Для свечения светодиода, находящегося на пересечении i-й строки и j-го столбца необходимо через канал B в i-м разряде и через канал С в j-м разряде выдать 0. При этом на анод будет подано +5В, а катод светодиода через открытый транзистор будет подключен к нулю.

– 79 –

Настройка ППИ на режим должна осуществляться путем загрузки константы 90Н в регистр управляющего слова (адрес 03Н).

При статическом режиме индикации набор светящихся светодиодов определяется парой кодов, выдаваемых через каналы В и С. При невозможности такой реализации (например, свечение светодиодов по диагонали матрицы) может быть использован динамический режим индикации, при котором информация последовательно во времени выводится построчно, то есть в любой момент «подключаются» только светодиоды одной строки. В остальных строках видимое свечение сохраняется за счет инерционности светодиодов и глаза человека.

В ПЗУ платы ПС записана программа, осуществляющая при нажатии какой-либо клавиши на клавиатуре зажигание соответствующего столбца. Начальный адрес программы – 8000Н. Программа может быть использована для проверки работоспособности платы.

Программа использует в своей работе подпрограмму индикации на светодиодной матрице содержимого ячеек памяти с адресами 0801Н–0805Н. Ячейка с адресом 0801Н должна содержать код для отображения в верхней строке светодиодной матрицы, а ячейка с адресом 0805 – код для отображения в нижней строке матрицы. При этом старший бит байта управляет крайним правым светодиодом в строке, а младший бит байта – крайним левым. Единичное значение бита соответствует зажженному светодиоду, нулевое – погашенному. (Подпрограмма инвертирует байты перед выдачей в порт). Начальный адрес подпрограммы – 8065Н. Подпрограмма может быть вызвана из программ пользователя.

Текст программы, записанной в ПЗУ платы ПС, приведен на рис. 28.