Shamrov_M_I_Telnov_G_G_Organizatsia_ustroystv_na_baze_protsessorov_maloy_razryadnosti

.pdf

– 120 –

RA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

СИНХР |

|

|

|

|

ЦАП2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

5 |

6 |

+12В |

|

R19 |

–15В |

|

|

|

|

|

|

|

|

|

7 |

8 |

+12В |

R21 |

|

–15В |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

R22 |

R18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

R23 |

R20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

R11 |

|

|

|

|

R15 |

|

|

|

|

|

|

|

|

|

|

R12 |

|

|

|

|

|

R16 |

|

|

|

|

|

|

|

|

|

|

|

|

ЦАП1 |

|

|

Va |

|

|

|

Va’ |

|

|

|

|

|

+12В |

|

|

|

ЦАП2 |

|

Va |

|

|

|

Va’ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦА |

|

D10 |

D9 |

|

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

Vоп |

R8 |

|

R9 |

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

|

Vоп |

|

|

|

|

|

|

|

|

|

|

|

платы |

||

2ППИ A6 |

|

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

C7 |

C6 |

C5 |

C4 |

C3 |

C2 |

C1 |

C0 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

схема |

|

A7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Функциональная |

A7 |

A6 |

|

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

C7 |

C6 |

C5 |

C4 |

C3 |

C2 |

C1 |

C0 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

|

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

A8 |

A9 |

A10 |

CS OE |

|||

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

A0 |

A1 |

|

CS |

|

RD |

WR |

RES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

1 |

2 |

|

|

8 |

|

26 |

27 |

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

1 |

2 |

|

|

7 |

|

26 |

27 |

28 |

|

|

|

|

|

|

17 |

18 |

19 |

20 |

21 |

22 |

23 |

24 |

|

|

|||||||

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

A0 |

A1 |

|

CS |

|

RD |

WR |

RES |

|

|

|

|

|

|

|

D0 |

|

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

|

||||||

ППИ1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ПЗУ |

|

|

|

|

|

|

|

|

|

|

2K x 8 |

|

||

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 11 |

|

41. |

||

D10 |

D9 |

|

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

RA |

|

|

|

|

|

D10 |

D9 |

D8 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

|

RA |

|

|

|

|

|

25 |

16 |

|

|

|

& |

Рис. |

АЦП1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦП2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Va |

|

|

|

|

|

|

|

|

CH |

R |

|

|

|

|

|

|

Va |

|

|

|

|

|

|

|

CH |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

R1 |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

R2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

SA1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦП2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

21 |

22 |

23 |

|

24 |

25 |

26 |

27 |

28 |

|

|

|

|

|||||||

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

A6 |

A7 |

A8 |

A9 |

A10 |

A11 |

A12 |

A13 A14 |

A15 |

D0 |

D1 |

D2 |

D3 |

D4 |

|

D5 |

D6 |

D7 |

MRDC |

IORC |

IOWC RESET |

|

|

|

|||||||||||

– 121 –

выше примере на двух крайних правых индикаторах появится 2,5. Далее аналогичным образом можно ввести новое значение напряжения, которое заменит предыдущее.

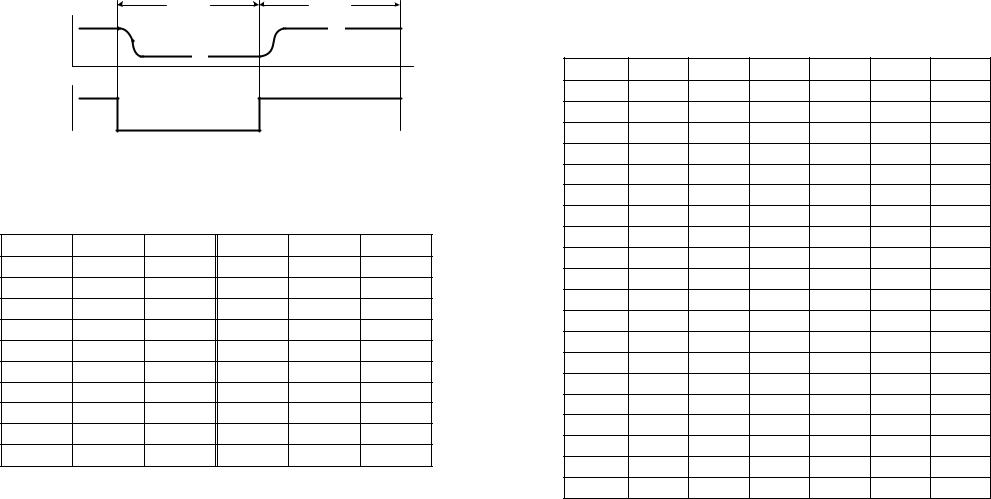

Ввод информации от двух АЦП К1113ПВ1А (на схеме – АЦП1 и АЦП2) осуществляется через БИС программируемого параллельного интерфейса К580ВВ55А (на схеме обозначена как ППИ1). У каждого из двух АЦП задействованы только 8 из 10 цифровых разрядов (два младших не используются). Выходы АЦП1 подключены к каналу А ППИ1 (адрес 80Н). Выходы АЦП2 подключены к каналу В ППИ1 (адрес 81Н).

Сброс и запуск аналого-цифрового преобразования производится подачей вначале единичного, а затем нулевого уровня на объединенные входы R двух АЦП. Объединенный сигнал сбросазапуска формируется на выводе С0 (младший разряд канала С) ППИ1. Таким образом, сброс-запуск аналого-цифрового преобразования производится и в АЦП1, и в АЦП2 одновременно. Сброс-запуск аналого-цифрового преобразования производится также по сигналу RESET из УМК. Объединенный сигнал сбросазапуска R выдается на контактную площадку для удобства подключения осциллографа.

Выводы готовности RA от двух АЦП объединены через дизъюнктор и образуют единый сигнал готовности, который поступает на выводы С7–С4 (старшие четыре разряда канала С) ППИ1. Таким образом, при готовности данных для считывания и в АЦП1, и в АЦП2, на выводы С7–С4 ППИ1 подаются нули, если же хотя бы в одном из двух АЦП данные не готовы – на выводы С7–С4

ППИ1 подаются единицы. Объединенный сигнал готовности RA

– 122 – |

|

|

– 123 – |

|

выдается на контактную площадку для удобства подключения |

ЦАП2. Опорное напряжение для обоих ЦАП равно +10,24 В. |

|||

осциллографа. Канал С ППИ1 имеет адрес 82Н. |

Потенциометры R19 и R21 предназначены для установки нуля на |

|||

На вход АЦП1 подается сигнал с переключателя, установ- |

выходах усилителей соответственно для ЦАП1 и ЦАП2. |

|||

ленного на плате АЦА. С помощью данного переключателя |

Потенциометры R22 и R23 предназначены для установки |

|||

возможно подключение к аналоговому входу АЦП1 либо сигнала с |

коэффициента усиления выходных усилителей соответственно для |

|||

выхода ЦАП1, либо нулевого уровня. |

ЦАП1 и ЦАП2. |

|

|

|

Вход АЦП2 выведен на контактную площадку для |

Выход усилителя ЦАП1 подключен к переключателю и с его |

|||

обеспечения возможности подачи внешних аналоговых сигналов. |

помощью может быть соединен с входом АЦП1. |

|

||

Его напряжение должно находиться в диапазоне от 0 до +10,2 В. |

Выход усилителя ЦАП2 выведен на контактную площадку |

|||

Оставление входа АЦП неподключенным эквивалентно подаче на |

для подключения внешних устройств, например осциллографа. |

|||

него нулевого напряжения. |

Старший разряд кода, подаваемого на ЦАП2 выведен на |

|||

Вывод информации на два ЦАП К572ПА1А (на схеме |

контактную площадку СИНХР и может использоваться для |

|||

обозначены как ЦАП1 и ЦАП2) осуществляется через БИС |

синхронизации осциллографа (в случае, если старший разряд кода |

|||

программируемого параллельного интерфейса К580ВВ55А (на |

принимает единичное (и нулевое) значение один раз за период |

|||

схеме – ППИ2). У каждого из двух ЦАП задействованы только 8 из |

исследуемого сигнала). |

|

|

|

10 цифровых разрядов (на два младших подан нулевой уровень). |

Значения опорных напряжений, подключение и настройка |

|||

Входы ЦАП1 подключены к каналу А ППИ2 (адрес 40Н). Входы |

ЦАП и АЦП на плате АЦА обеспечивают одинаковую разрешаю- |

|||

ЦАП2 подключены к каналу В ППИ2 (адрес 41Н). |

щую способность всех ЦАП и АЦП: 40 мВ на единицу младшего |

|||

К выходам обоих ЦАП подключены быстродействующие |

разряда 8-разрядного кода. При этом двоичный код |

00000000 |

||

операционные усилители КР574УД1А, регулировка которых |

соответствует |

напряжению |

0 В, а двоичный код |

11111111 |

рассчитана на выходное напряжение от 0 до +10,2 В. Но из-за |

соответствует напряжению +10,2 В. Исключением из этого правила |

|||

нелинейности операционного усилителя реально получаемое |

является функционирование ЦАП, в которых при попытке |

|||

максимальное выходное напряжение составляет примерно +9,7 В. |

сформировать |

напряжение, |

превышающее +9 В получается |

|

При этом выходное напряжение от 0 до +9 В растет линейно с |

напряжение меньше ожидаемого (двоичный код 11111111 |

|||

возрастанием кода, поданного на ЦАП, а при подаче кода для |

формирует напряжение около +9,7 В). |

|

||

формирования напряжения, превышающего +9 В, реально |

Адреса и назначение портов на плате АЦА приведены в |

|||

получаемое напряжение будет меньше ожидаемого. |

табл. 16. |

|

|

|

Потенциометры R8 и R9 предназначены для подстройки |

Кроме перечисленных блоков, в состав платы АЦА включен |

|||

величины опорного напряжения Vоп соответственно для ЦАП1 и |

вторичный источник напряжения –15 В (на рис. 41 не показан). |

|||

|

|

|

– 124 – |

|||

|

|

|

|

Таблица 16 |

||

|

Адреса портов на плате АЦА |

|||||

|

|

|

|

|

|

|

ППИ |

Канал |

Адрес |

|

Назначение |

||

1 |

А |

80Н |

|

Код от АЦП1 |

||

|

В |

81Н |

|

Код от АЦП2 |

||

|

С[0] |

82Н |

|

Сигнал сброса-запуска R |

||

|

|

для АЦП1, АЦП2 |

||||

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

Сигнал готовности |

|

|

|

C[7–4] |

82Н |

|

RA |

||

|

|

от АЦП1, АЦП2 |

||||

|

|

|

|

|||

|

|

|

|

|

||

|

Управления |

83Н |

|

Управляющее слово для ППИ1 |

||

2 |

А |

40Н |

|

Код на ЦАП1 |

||

|

В |

41Н |

|

Код на ЦАП2 |

||

|

С |

42Н |

|

Не используется |

||

|

Управления |

43Н |

|

Управляющее слово для ППИ2 |

||

8.4. Изучение цифро-аналогового преобразователя К572ПА1А

ПОДГОТОВКА К РАБОТЕ

1.Используя настоящее учебное пособие изучить параметры

испособы использования ЦАП К572ПА1А, а также особенности его подключения на плате АЦА.

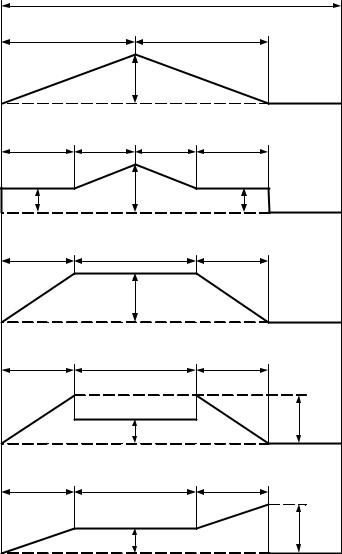

2.По варианту задания 1 из табл. 17 написать и закодировать программу, осуществляющую формирование периодического сигнала, один период которого представлен на рис. 42. Сигнал должен формироваться на выходе ЦАП2. Программа должна настроить ППИ2 на выдачу информации в ЦАП2, а затем осуществлять циклическую выдачу в ЦАП2 попеременно двух кодов для формирования напряжений U1 и U2. Длительность

– 125 –

выдачи каждого из двух уровней должна составлять не менее 10 мкс. Требуемые задержки реализовать программным способом, считая, что длительность такта УМК равна 600 нс.

3. По варианту задания 2 из табл. 18 написать и закодировать программу, осуществляющую формирование периодического сигнала, один период которого (Т) представлен на рис. 43. Сигнал сформировать на выходе ЦАП2. Программа должна настроить ППИ2 на выдачу информации в ЦАП2, затем осуществлять циклическую выдачу в ЦАП2 кодов для формирования периодического сигнала.

Линейно возрастающие и линейно убывающие участки сигнала формировать с помощью монотонного увеличения или уменьшения текущего значения кода. Участки с постоянным уровнем сигнала формировать с помощью программной задержки. Считать, что длительность такта УМК равна 600 нс.

Данная программа будет использована также в одной из следующих работ (см. разд. 8.6).

РАБОЧЕЕ ЗАДАНИЕ

1.Ввести в УМК и запустить на исполнение программу, подготовленную по варианту задания 1. Снять микровременные диаграммы процессов переключения U1 → U2 и U2 → U1. Время срабатывания ЦАП2 определять относительно изменения старшего разряда цифрового кода, выведенного на контактную площадку СИНХР. Для синхронизации осциллографа также использовать сигнал СИНХР.

2.Ввести в УМК и запустить на исполнение программу, подготовленную по варианту задания 2. Снять временную диаграмму сигнала и измерить его параметры. При их расхождении

сзаданными – скорректировать программу и повторить измерение.

|

|

|

– 126 – |

|

|

|

|

|

|

|

– 127 – |

|

|

|

||

|

|

|

>10 мкс |

|

|

>10 мкс |

|

|

|

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

U2 |

|

|

|

|

|

|

|

|

Таблица 18 |

|

|

|

|

|

|

|

|

|

|

Варианты задания 2 к лабораторной работе № 8 |

|||||||

|

|

|

U1 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

Вариант |

Сигнал U1, B |

U2, B |

T, мс |

t1, мс |

t2, мс |

|||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

1 |

S1 |

6 |

– |

3 |

1 |

1,5 |

|

СИНХР |

|

|

|

|

|

|

|

2 |

S2 |

6 |

8 |

4 |

0,5 |

1 |

||

|

|

Рис. 42. Временная диаграмма измерения |

|

|

3 |

S3 |

7 |

– |

5 |

1 |

2 |

|||||

|

|

|

|

4 |

S4 |

3 |

8 |

4 |

1 |

1 |

||||||

|

|

времени срабатывания ЦАП |

|

|

||||||||||||

|

|

|

|

5 |

S5 |

2 |

6 |

3 |

1 |

0,5 |

||||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

Таблица 17 |

6 |

S1 |

8 |

– |

4 |

2 |

1 |

||

|

|

|

|

|

|

|

7 |

S2 |

4 |

8 |

6 |

1 |

1 |

|||

|

|

Варианты задания 1 к лабораторной работе № 8 |

|

|||||||||||||

|

|

|

8 |

S3 |

6 |

– |

4 |

1 |

0,5 |

|||||||

Вариант |

U1, B |

U2, B |

Вариант |

U1, B |

U2, B |

|||||||||||

9 |

S4 |

4 |

9 |

5 |

1 |

2 |

||||||||||

|

1 |

0 |

9 |

|

11 |

3 |

|

9 |

||||||||

|

|

|

10 |

S5 |

3 |

7 |

4 |

1 |

1 |

|||||||

|

2 |

4 |

6 |

|

12 |

2 |

|

7 |

||||||||

|

|

|

11 |

S1 |

7 |

– |

3 |

0,5 |

1,5 |

|||||||

|

3 |

3 |

7 |

|

13 |

3 |

|

6 |

||||||||

|

|

|

12 |

S2 |

3 |

9 |

3 |

0,5 |

0,5 |

|||||||

|

4 |

0 |

8 |

|

14 |

2 |

|

9 |

||||||||

|

|

|

13 |

S3 |

9 |

– |

6 |

1 |

3 |

|||||||

|

5 |

4 |

9 |

|

15 |

0 |

|

7 |

||||||||

|

|

|

14 |

S4 |

2 |

8 |

6 |

1 |

3 |

|||||||

|

6 |

3 |

8 |

|

16 |

1 |

|

9 |

||||||||

|

|

|

15 |

S5 |

4 |

8 |

6 |

2 |

1 |

|||||||

|

7 |

4 |

7 |

|

17 |

4 |

|

8 |

||||||||

|

|

|

16 |

S1 |

9 |

– |

5 |

1 |

2 |

|||||||

|

8 |

0 |

6 |

|

18 |

1 |

|

8 |

||||||||

|

|

|

17 |

S2 |

4 |

7 |

5 |

0,5 |

1 |

|||||||

|

9 |

1 |

7 |

|

19 |

2 |

|

6 |

||||||||

|

|

|

18 |

S3 |

8 |

– |

3 |

1 |

0,5 |

|||||||

|

10 |

2 |

8 |

|

20 |

1 |

|

6 |

||||||||

|

|

|

19 |

S4 |

3 |

7 |

6 |

1,5 |

2 |

|||||||

|

|

|

|

|

|

|

|

|

||||||||

Для |

синхронизации |

осциллографа |

можно |

использовать |

сигнал |

20 |

S5 |

5 |

9 |

5 |

1 |

1 |

||||

СИНХР. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

СОДЕРЖАНИЕ ОТЧЕТА |

|

|

|

|

|

|

|

|

|

|

|

|

|||

−тексты и коды программ;

−временные диаграммы.

|

|

– 128 – |

|

|

|

T |

|

t1 |

|

|

t2 |

S1 |

|

U1 |

|

t1 |

t2 |

t2 |

t1 |

S2 |

|

U2 |

|

U1 |

|

|

U1 |

t1 |

|

t2 |

t1 |

S3 |

|

U1 |

|

t1 |

|

t2 |

t1 |

S4 |

|

U1 |

U2 |

|

|

|

|

t1 |

|

t2 |

t1 |

S5 |

|

U1 |

U2 |

|

|

|

|

Рис. 43. Варианты сигналов к заданию 2 лабораторной работы № 8 |

|||

–129 –

8.5.Изучение аналого-цифрового преобразователя

К1113ПВ1А

ПОДГОТОВКА К РАБОТЕ

1.Используя настоящее учебное пособие изучить параметры

испособы использования АЦП К1113ПВ1А, а также особенности его подключения на плате АЦА.

2.Написать и закодировать программу, осуществляющую настройку ППИ1, ППИ2 и выдачу с выхода ЦАП1 напряжения, рассчитываемого как

U = 4N / 10,

где N – номер варианта, U – выходное напряжение ЦАП1 (в вольтах). Затем программа должна в цикле осуществлять сброс – запуск АЦП, ожидание готовности АЦП, считывание кода из АЦП1

изапись его в память по адресу 0900Н.

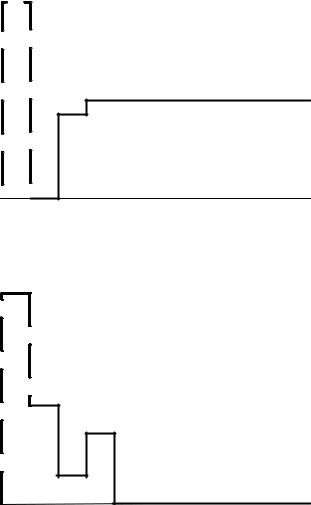

3.Написать и закодировать программу, осуществляющую «фотографирование» переходного процесса (дребезга) на выходе переключателя и его отображение на экране осциллографа. Рекомендуемая блок-схема программы приведена на рис. 44.

Программа должна в начале настроить ППИ1 и ППИ2, сформировать на выходе ЦАП1 напряжение +4 В и записать код FFН по адресу 0900Н. Циклическая выдача этого кода на ЦАП2 даст возможность использовать сигнал СИНХР для синхронизации осциллографа.

Далее выполняется цикл ввода значений из АЦП1 и записи их в память по последовательным адресам до тех пор, пока не будет заполнена область памяти 0901Н–09FFН. Текущий адрес для обращения к памяти удобно хранить в регистровой паре НL, а для перехода к следующему адресу увеличивать содержимое только

– 130 –

младшего регистра L. Это позволит использовать регистр L и как счетчик адреса, и как счетчик числа повторений цикла. Достижение конца области памяти может быть определено с помощью проверки на нуль содержимого регистра L по признаку, вырабатываемому командой INR L. Использование регистра L и в качестве счетчика адреса, и в качестве счетчика числа повторений цикла уменьшает длительность исполнения тела цикла, что дает возможность чаще опрашивать АЦП и получать более качественную «фотографию».

По окончании цикла ввода значений из АЦП необходимо зафиксировать последнее введенное значение, например, записать его в регистр В. Это же значение хранится в памяти по адресу 09FFН, но для ускорения исполнения цикла, рассматриваемого далее, это значение удобнее хранить в регистре.

Далее выполняется цикл вывода в ЦАП2 введенных ранее значений до тех пор, пока напряжение на входе АЦП1 не изменится на достаточную величину. Внутри цикла удобнее сначала выполнить сброс-запуск АЦП, затем (пока идет преобразование в АЦП) вывести очередное значение из памяти в ЦАП2, а только после этого выполнять опрос сигнала готовности АЦП. Здесь, как и в первом цикле, целесообразно хранить текущий адрес области памяти в регистровой паре HL, а для перехода к следующему адресу увеличивать содержимое регистра L, что дает возможность при достижении последнего адреса области памяти 09FFН автоматически переходить на начальный адрес 0900Н и, таким образом, осуществлять бесконечный цикл выдачи. Если считанное из АЦП1 значение отличается от зафиксированного в регистре (и совпадающего с записанным в памяти по адресу 09FFН) не более, чем на 2, то необходимо продолжить исполнение цикла. Если же считанное значение отличается от зафиксированного более чем на 2, то

– 131 –

необходимо выйти из цикла и выполнить новое «фотографирование» переходного процесса. В этом случае зафиксированное значение записывается в память по адресу 0901Н, последнее введенное значение (отличающееся от зафиксированного более, чем на 2) записывается по адресу 0902Н, а далее осуществляется переход к началу цикла опроса АЦП1, в котором вводимые значения записываются в память по адресам 0903Н–09FFН. Необходимость запуска нового процесса «фотографирования» только в том случае, если разница между зафиксированным и введенным значением превышает 2, обусловлена небольшим «дрожанием» выходного кода АЦП.

Моменты времени в процессе переключения, когда аналоговый вход АЦП ни к чему не подключен, рассматриваются как подача на него нулевого напряжения.

Длительный переходный процесс при переключении возникает в основном при размыкании контактов, при замыкании переходный процесс практически отсутствует.

Примерный вид временной диаграммы переходного процесса 0 В → +4 В представлен на рис. 45. Перед началом переходного процесса в зависимости от настройки синхронизации осциллографа иногда можно увидеть импульс амплитудой 10 В, который вставлен в «фотографию» переходного процесса только для удобства синхронизации осциллографа и не является частью самого переходного процесса (на рис. 45 показан штриховой линией). При размыкании контактов входа АЦП и источника 0 В переходный процесс отсутствует, поскольку оставление входа АЦП неподключенным и подача на него нуля эквивалентны. При замыкании контактов входа АЦП и источника +4 В переходный процесс очень мал, как обычно при замыкании.

– 132 –

Примерный вид временной диаграммы переходного процесса +4 В → 0 В представлен на рис. 46. Здесь также можно увидеть импульс синхронизации амплитудой 10 В. При размыкании контактов входа АЦП и источника +4 В возникает переходный процесс, который может длиться относительно долго. При замыкании контактов входа АЦП и источника 0 В переходный процесс практически отсутствует.

РАБОЧЕЕ ЗАДАНИЕ 1. С помощью переключателя соединить вход АЦП1 с

выходом ЦАП1. Ввести в УМК и запустить на исполнение программу, осуществляющую вывод и ввод напряжения U. Снять

временные диаграммы сигналов R, RA . Измерить время срабатывания АЦП. Прервать исполнение программы нажатием клавиши ПР. Прочитать содержимое ячейки памяти по адресу 0900Н. Определить абсолютную погрешность преобразования для пары ЦАП1–АЦП1.

2. Ввести в УМК и запустить на исполнение программу «фотографирования» переходного процесса. Снять на выходе ЦАП2 временные диаграммы переходных процессов 0 В → +4 В и +4 В → 0 В. Для синхронизации осциллографа использовать выход СИНХР. Развертка осциллографа для наблюдения переходного процесса должна быть установлена на значение около 100 мкс/деление.

СОДЕРЖАНИЕ ОТЧЕТА

−тексты и коды программ;

−временные диаграммы сигналов и абсолютная погрешность преобразования для первой части работы;

−временные диаграммы переходных процессов.

|

– 133 – |

|

НАЧАЛО |

|

Настройка ППИ1, ППИ2 |

|

Формирование +4 В на ЦАП1 |

|

Запись FFH по адресу 0900H |

|

Сброс - запуск АЦП |

нет |

Есть готовность АЦП? |

|

|

|

да |

|

Ввод значения из АЦП1 и запись в память |

нет |

Область памяти заполнена? |

|

|

|

да |

|

Запись последнего введённого значения в регистр В |

|

Сброс - запуск АЦП |

|

Чтение значения из памяти и вывод в ЦАП2 |

нет |

Есть готовность АЦП? |

|

|

|

да |

нет |

Начался новый переходный процесс? |

|

|

|

да |

|

Запись по адресу 0901Н значения из регистра В |

|

Запись по адресу 0902Н последнего введённого значения |

Рис. 44. Блок-схема программы «фотографирования» |

|

|

переходного процесса (дребезга) |

– 134 –

Рис. 45. Примерный вид временной диаграммы переходного процесса 0 В → +4 В

Рис. 46. Примерный вид временной диаграммы переходного процесса +4 В → 0 В

–135 –

8.6.Совместное использование ЦАП и АЦП

ПОДГОТОВКА К РАБОТЕ

1.Написать и закодировать программу, осуществляющую ввод значений из АЦП2 и выдачу этих значений в ЦАП2. Программа должна в начале настроить ППИ1 и ППИ2, а затем осуществлять в цикле сброс-запуск АЦП, ожидание готовности АЦП, ввод кода из АЦП2 и выдачу введенного кода в ЦАП2.

Эксперимент выполняется с использованием двух УМК (объединяются две бригады). Первая УМК, с помощью программы, подготовленной ранее, осуществляет циклическую выдачу сигнала (см. табл. 18, рис. 43) на выход ЦАП2. Вторая УМК осуществляет непрерывный опрос сигнала на входе АЦП2, соединенного с выходом ЦАП2 первой УМК, и выдачу принятых значений сигнала через ЦАП2.

РАБОЧЕЕ ЗАДАНИЕ

1.Соединить выход ЦАП2 одной УМК с входом АЦП2 второй УМК. Соединить выводы «земля» двух УМК.

2.Ввести в первую УМК и запустить на исполнение программу генерации сигнала.

3.Ввести во вторую УМК и запустить на исполнение программу двойного (аналог-цифра-аналог) преобразования.

4.Снять осциллограммы сигналов с выходов ЦАП2 обоих

УМК.

СОДЕРЖАНИЕ ОТЧЕТА

−текст и коды программы;

−осциллограммы сигналов.

– 136 –

ЛИТЕРАТУРА

1.Пухальский Г.И. Проектирование микропроцессорных систем. – СПб.: Политехника, 2001. – 544 с.

2.Каган Б.М., Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. – М.: Энергоатомиздат, 1987. – 304 с.

3.Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. – М.: Радио и связь, 1989. – 288 с.

4.Микро-ЭВМ / Под ред. А.Дирксена; Пер. с англ. – М.: Энергоиздат, 1982. – 328 с.

5.Микропроцессоры. В 3-х кн. Кн. 1. Архитектура и проектирование микро-ЭВМ. Организация вычислительных процессов / П.В.Нестеров, В.Ф.Шаньгин, В.Л.Горбунов и др.; Под ред. Л.Н.Преснухина. – М.: Высшая школа, 1986. – 495 с.

6.Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л. Справочное пособие по микропроцессорам и микро-ЭВМ / Под ред. Л.Н.Преснухина. – М.: Высшая школа, 1988. – 272 с.

7.Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов. – М.: Радио и связь, 1988.

–368 с.

8.Гибсон Г., Лю Ю-Ч. Аппаратные и программные средства микро-ЭВМ / Пер. с англ. – М.: Финансы и статистика, 1983. – 256 с.

9.Григорьев В.Л. Программное обеспечение микропроцессорных систем. – М.: Энергоатомиздат, 1983. – 208 с.

10.Хвощ С.Т., Варлинский Н.Н., Попов Е.А. Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник / Под общ. ред. С.Т.Хвоща. – Л.: Машиностроение.

Ленингр. отд., 1987. – 640 с.

–137 –

11.Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2-х тт. / Н.Н.Аверьянов, А.И.Березенко, Ю.И.Борщенко и др.; Под ред. В.А.Шахнова. – М.:

Радио и связь, 1988. – Т. 1. – 368 с.

12.Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др.; Под ред. С.В.Якубовского. – М.: Радио и связь, 1989. – 496 с.

13.Микропроцессоры: Справочное пособие для разработчиков судовой РЭА / Г.Г.Гришин, А.А.Мошков, О.В.Ольшанский, Ю.А.Овечкин; Под ред. Ю.А.Овечкина. – 2-е изд., стереотип. – Л.: Судостроение, 1988. – 520 с.

14.Микропроцессор К580: архитектура и принципы работы: Методические указания / Сост. В.В.Сташин, А.В.Урусов. – М.:

МИИТ, 1986. – 40 с.

15.Система команд микропроцессора К580ИК80: Методические указания / Сост. В.В.Сташин, О.Ф.Мологонцева. – М.: МИИТ, 1986. – 44 с.

16.Программная реализация типовых функций управления в микропроцессоре К580: Методические указания / Сост. В.В.Сташин, О.Ф.Мологонцева. – М.: МИИТ, 1987. – 36 с.

17.Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. – М.: Энергоатомиз-

дат, 1990. – 320 с.

18.Федорков Б.Г., Телец В.А., Дегтяренко В.П. Микроэлектронные цифро-аналоговые и аналого-цифровые преобразователи. – М.: Радио и связь, 1984. – 120 с.

19.Чернов В.Г. Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных. – М.: Машиностроение, 1988. – 184 с.

– 138 – |

|

– 139 – |

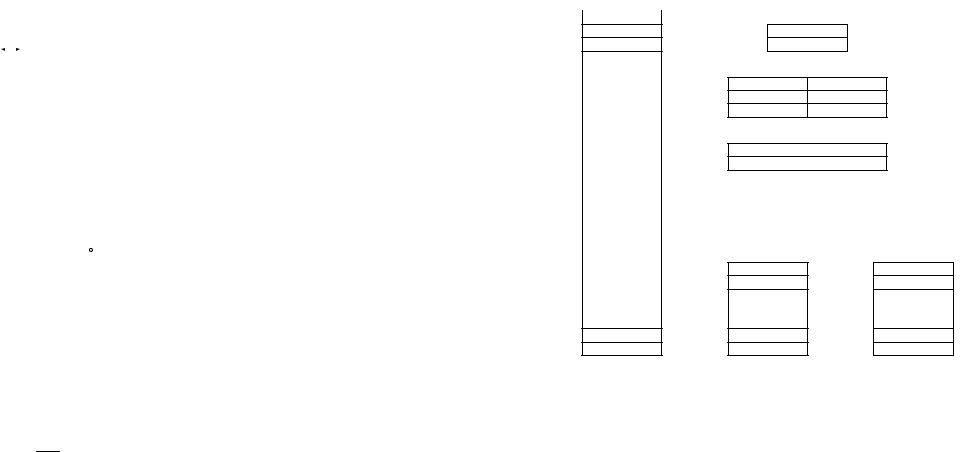

ПРИЛОЖЕНИЕ А |

2. Программистская модель |

|

CПРАВОЧНЫЕ ДАННЫЕ ПО МИКРОПРОЦЕССОРУ |

|

|

К580ВМ80 |

|

|

1. Назначение выводов микросхемы |

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

D0 |

|

|

||

|

|

|

|

|||

|

|

CPU |

A1 |

|

||

|

|

D1 |

|

|||

|

|

A2 |

|

|||

|

|

D2 |

|

|

||

|

|

|

A3 |

|

||

|

|

D3 |

|

|

||

|

|

|

A4 |

|

||

|

|

D4 |

|

|

||

|

|

|

A5 |

|

||

|

|

D5 |

|

|

||

|

|

|

A6 |

|

||

|

|

D6 |

|

|

||

|

|

|

A7 |

|

||

|

|

D7 |

|

|

||

|

|

|

A8 |

|

||

|

|

|

|

|

|

|

|

|

Ф1 |

|

A9 |

|

|

|

|

|

|

|||

|

|

|

A10 |

|

||

|

|

|

|

|||

|

|

Ф2 |

|

A11 |

|

|

|

|

|

|

|||

|

|

|

|

|

A12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

A13 |

|

|

|

|

|

|

|

|

|

RESET |

|

A14 |

|

||

|

|

|

||||

|

|

|

|

|

A15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WAIT |

|

|

|

|

|

|

|

|

|

READY |

|

HLDA |

|

||

|

|

|

||||

|

|

INTE |

|

|||

|

HOLD |

|

|

|||

|

|

SYNC |

|

|||

|

INT |

|

|

|||

|

|

WR |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

DBIN |

|

|

|

|

|

|

|

|

Двунаправленные выводы:

D7–D0 – шина данных

Входы:

Ф1, Ф2 – сигналы синхронизации

RESET – сигнал начальной установки (сброса) READY – сигнал готовности

HOLD – запрос захвата шин

INT – запрос прерывания

Выходы:

A15–A0 – шина адреса

WAIT – сигнал подтверждения состояния ожидания (при отсутствии сигнала готовности)

HLDA – подтверждение состояния захвата шин INTE – сигнал разрешения прерываний по входу INT

SYNC – сигнал (строб) выдачи на шину данных слова состояния машинного цикла

WR – сигнал (строб) операции записи или вывода DBIN – сигнал (строб) операции чтения или ввода