Shamrov_M_I_Telnov_G_G_Organizatsia_ustroystv_na_baze_protsessorov_maloy_razryadnosti

.pdf– 40 –

для организации связи микропроцессора с памятью, устройствами ввода-вывода и другими блоками УМК. В табл. 4 приведены значения всех управляющих сигналов для каждого типа машинного цикла.

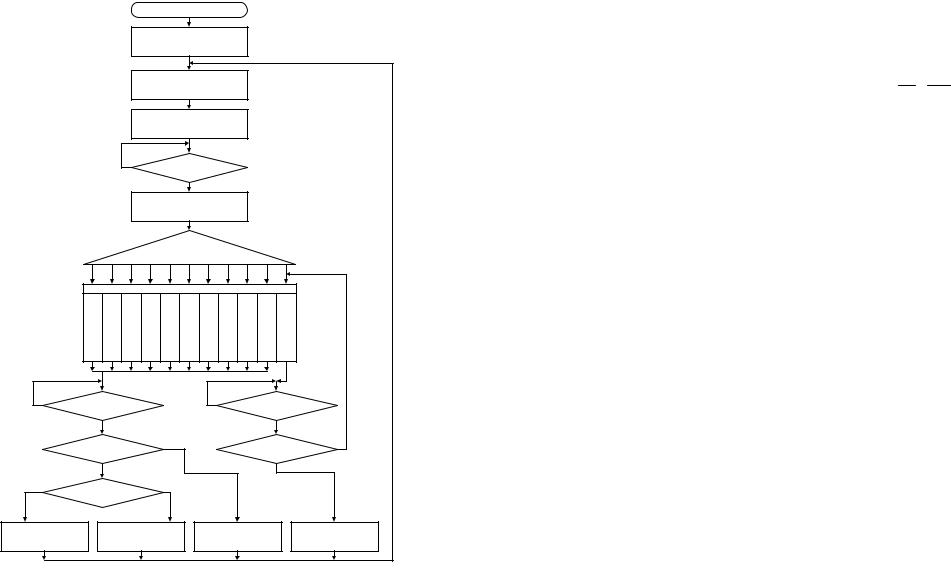

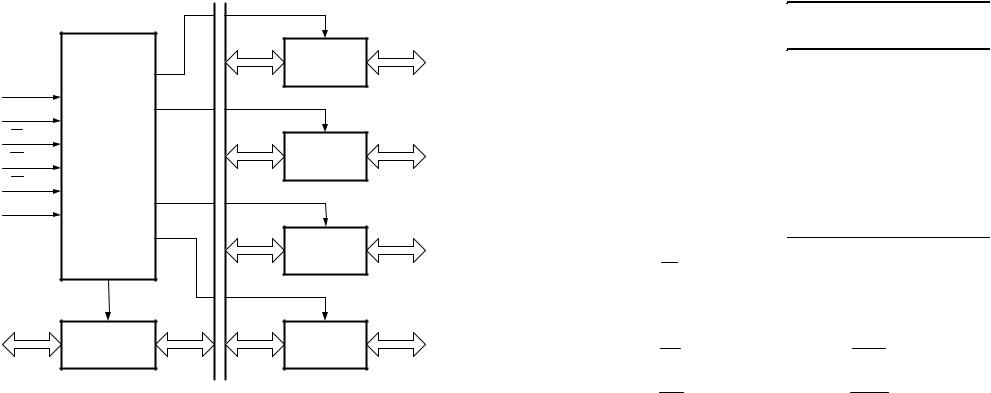

Машинный цикл имеет переменную длительность в зависимости от типа реализуемой команды и может состоять из 3–5 тактов Т1–Т5. Блок-схема организации машинного цикла микропроцессора представлена на рис. 8. После начальной установки или окончания исполнения очередной команды выполняются первые три такта машинного цикла выборки первого байта команды. Такты Т1–Т3 присутствуют в любом машинном цикле. В такте Т1 на шину A микропроцессора выдается адрес памяти или порта, а на шину D – слово состояния машинного цикла, идентифицирующее тип выполняемого машинного цикла. Выдача слова состояния каждого машинного цикла сопровождается сигналом СИНХР(SYNC). В такте Т2 сигнал СИНХР(SYNC) сбрасывается и слово состояния больше не присутствует на шине D. В машинном цикле записи в такте Т2 на шину D выставляются данные для записи. После такта Т2 микропроцессор может перейти в режим ожидания (при отсутствии сигнала ГТ(READY)), останова (по команде HLT) или перейти к такту Т3 (основной режим).

В режиме ожидания микропроцессор приостанавливает работу до получения единичного уровня на входе готовности ГТ(READY). Этот режим может быть использован для согласования работы микропроцессора и медленных периферийных устройств. После окончания режима ожидания выполняется возврат в основной режим.

– 41 –

Таблица 4

Слово состояния машинного цикла

Тип машинного |

Разряды слова состояния машинного цикла |

|||||||||

цикла |

M E M R |

INP |

M1 |

OUT |

HLTA |

STACK |

|

|

|

INTA |

WO |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

Выборка первого |

1 |

0 |

1 |

0 |

0 |

0 |

|

1 |

|

0 |

байта команды |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Чтение из памяти |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

0 |

Запись в память |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

Чтение из стека |

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

|

0 |

Запись в стек |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

|

0 |

Чтение из порта |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

|

0 |

Запись в порт |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

Прерывание (выборка |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

|

1 |

первого байта |

|

|

||||||||

команды) |

|

|

|

|

|

|

|

|

|

|

Прерывание (выборка |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

1 |

не первого байта |

|

|

||||||||

команды) |

|

|

|

|

|

|

|

|

|

|

Останов |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

|

0 |

Прерывание в |

|

|

|

|

|

|

|

|

|

|

останове (выборка |

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

|

1 |

первого байта |

|

|

|

|

|

|

|

|

|

|

команды) |

|

|

|

|

|

|

|

|

|

|

– 42 – |

Рис. 8. Упрощенная блок-схема машинного цикла |

–43 –

Втакте Т3 микропроцессор осуществляет запись выданных данных или чтение по адресу, выставленному на шине А. При чтении информации микропроцессор выставляет единичный уровень на выходе ЧТ(DBIN) в такте Т2. При записи информации

микропроцессор выдает нулевой уровень на вывод ЗП ( WR ) в такте Т3. После такта Т3 в некоторых типах машинных циклов осуществляется переход к такту Т1 следующего цикла, либо исполняются еще один или два такта Т4–Т5. Такты Т4–Т5 нужны для выполнения действий внутри микропроцессора.

После окончания машинного цикла может произойти переход в режим захвата (при ЗХВ(HOLD)=1). При этом выдается сигнал ПЗХВ(HLDA), а шины адреса, данных и некоторые линии шины управления отключаются (переводятся в третье состояние) сразу после выполнения действий в такте Т3. Если остановленный машинный цикл включал такты Т4–Т5, то они выполняются уже в режиме захвата. Обычно режим захвата используется для организации прямого доступа в память от периферийных устройств при отключенном микропроцессоре.

Режим останова устанавливается программным путем после команды HLT. В режиме останова микропроцессор переводит шины адреса и данных в третье состояние. В режиме останова микропроцессор может перейти в режим захвата, при котором выдается сигнал подтверждения захвата ПЗХВ(HLDA), а процессор продолжает находиться в режиме останова. Выход из режима останова возможен с помощью прерывания. Выход из любого режима на начало рабочего цикла может быть выполнен по сигналу СБРОС(RESET).

Большинство сигналов на выходах микропроцессора изменяется по переднему фронту сигнала Ф2(F2).

–44 –

Вконце последнего машинного цикла команды проверяется возможность прерывания работы микропроцессора. Прерывание возникает при выполнении следующего условия:

ЗПР(INT) & ТРПР = 1,

где ТРПР – внутренний триггер разрешения прерываний микропроцессора. Состояние ТРПР всегда присутствует на выходе РПР(INTE). При выполнении этого условия микропроцессор переходит к машинному циклу «Прерывание (выборка первого байта команды)». В этом машинном цикле ТРПР сбрасывается и запрещается увеличение программного счетчика. Если в цикле считан код операции многобайтной команды, следующим будет исполняться машинный цикл «Прерывание (выборка не первого байта команды)» на каждый последующий байт команды. Триггер ТРПР можно установить впоследствии командой EI. При этом прерывания разрешаются после исполнения следующей, после EI, команды. Сброс триггера ТРПР осуществляется также командой DI или по сигналу СБРОС(RESET).

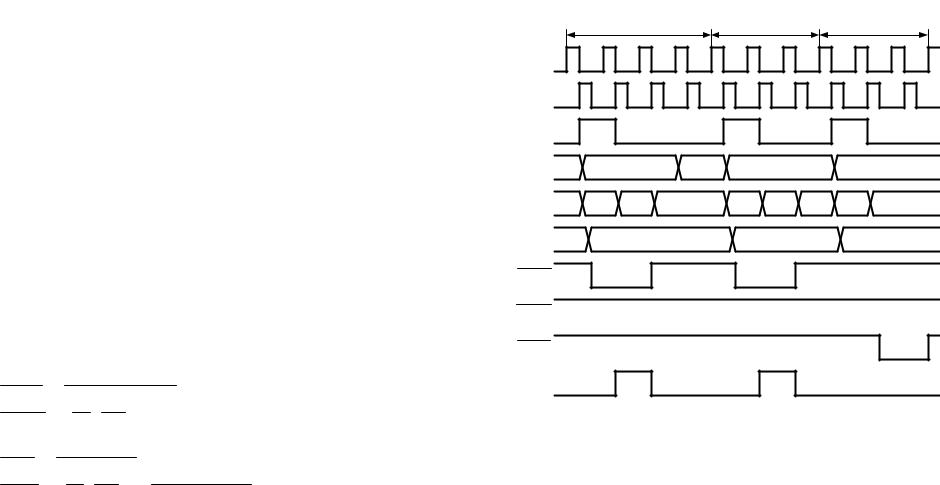

На рис. 9 приведена временная диаграмма сигналов при исполнении команды OUT, где

MRDC = ЧТП(MEMR-ST7) – сигнал чтения из памяти;

MWTC = ЗП ( WR ) ВЫВ(OUT-ST4) – сигнал записи в

память;

IORC = ВВ(INP-ST6) – сигнал ввода из порта;

IOWC = ЗП ( WR ) ВЫВ(OUT-ST4) – сигнал вывода в

порт.

Схемы формирования и использования перечисленных сигналов см. рис. 3, 5.

– 45 –

Рис. 9. Пример временной диаграммы (команда OUT)

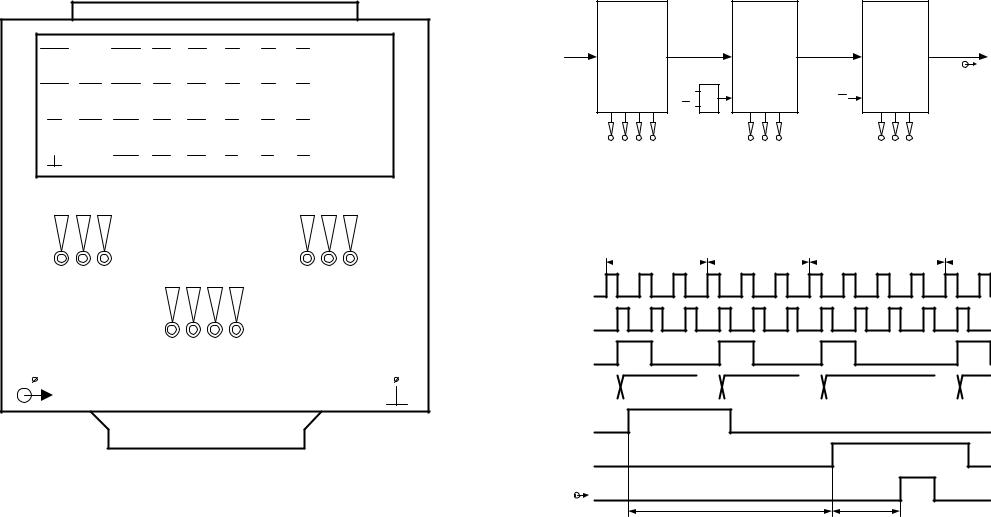

Для снятия осциллограмм сигналов УМК используется сменный блок – модифицированный блок М1, подключаемый к УМК через внешний разъем. Внешний вид блока представлен на рис. 10.

|

– 46 – |

Разъем для подключения осциллографа |

|

STSTB IOWC |

|

циклы |

такты |

|

адрес |

|

Системный разъем |

Рис. 10. Внешний вид сменного блока М1

– 47 –

Рис. 11. Схема получения сигнала синхронизации осциллографа в блоке М1

Машинный цикл (i) Машинный цикл (i+1) |

Машинный цикл (i+2) |

М.ц. (i+3) |

||||

|

|

|

|

|

|

|

Ф1

Ф2 (F2)

SYNC

A[15-0] |

Ai |

|

Ai+1 |

|

Ai+2 |

|

Ai+3 |

|

|

|

|

|

|

|

|

S1

S2

S3

Задержка |

Задержка |

2 цикла |

2 такта |

Рис. 12. Временная диаграмма формирования сигнала синхронизации осциллографа в блоке М1

– 48 –

Блок выполнен в виде двойной печатной платы с двумя разъемами. Системный разъем используется для подключения блока к УМК. Второй (верхний) разъем состоит из контактных гнезд, на которые через буферные схемы выведены шины адреса, данных и управления УМК. Гнезда служат для подключения соответствующих сигналов к осциллографу. Для запуска развертки осциллографа в блоке реализована специальная схема синхронизации, структура которой представлена на рис. 11.

Схема состоит из компаратора адреса, осуществляющего сравнение адреса, выдаваемого из микропроцессора с кодом 080xН, где x – код, набираемый на переключателях «АДРЕС» блока М1. Сигнал совпадения с выхода компаратора (S1) запускает счетчик

циклов, который по каждому сигналу SYNC & F2 подсчитывает количество циклов исполняемой программы. При достижении равенства числа подсчитываемых циклов и числа, набранного на переключателях «ЦИКЛЫ» блока М1, счетчик циклов выдает сигнал (S2) запуска счетчика тактов. Счетчик тактов начинает подсчет числа тактов по заднему фронту синхросигнала F2. При достижении равенства числа подсчитываемых тактов и числа, набранного на переключателях «ТАКТЫ» блока М1, счетчик тактов выдает сигнал S3, который выдается на специальный контакт и может быть использован в качестве сигнала запуска осциллографа. Таким образом, момент запуска развертки осциллографа задается моментом окончания первого такта машинного цикла, в котором на шине A появляется один из 16 адресов ОЗУ, начиная с адреса 0800Н и сдвигом относительно этого момента, заданным количеством циклов и тактов. Сигнал запуска выдается на контакт {Æ блока М1. Работа схемы синхронизации поясняется временной диаграммой на рис. 12. На временной диаграмме приведен вариант,

– 49 –

Рис. 13. Схема проведения эксперимента по снятию временных диаграмм

когда на переключателях «АДРЕС» набран адрес Аi, на переключателях «ЦИКЛЫ» – 2, на переключателях «ТАКТЫ» – 2.

Нужно иметь в виду, что с сигналом F2 и другими сигналами УМК соотнесен лишь передний фронт сигнала запуска синхронизации с платы М1. Задний фронт сигнала возникает в не связанный с сигналами УМК момент времени. Поэтому развертку осциллографа следует запускать по переднему фронту сигнала синхронизации, для чего необходимо соответствующим образом настроить осциллограф.

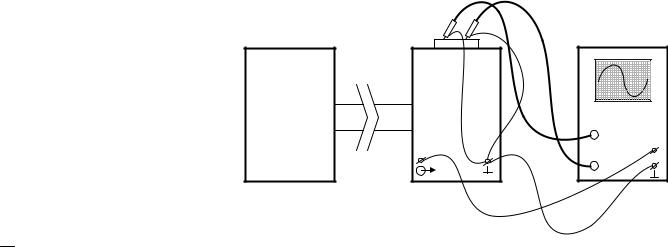

В лабораторной работе используется двухканальный осциллограф. Схема подключения осциллографа к блоку М1 для снятия временных диаграмм сигналов УМК приведена на рис. 13.

При снятии временных диаграмм целесообразно использовать каналы осциллографа следующим образом:

–50 –

−на I (верхний) канал подается сигнал F2;

−на II (нижний) канал подается один из исследуемых сигналов, который при необходимости можно инвертировать.

Такое распределение каналов осциллографа объясняется тем, что во-первых, все сигналы можно точно снять только относительно сигнала F2, во-вторых, многие исследуемые сигналы необходимо инвертировать относительно значения, выведенного на верхний разъем блока М1.

ПОДГОТОВКА К РАБОТЕ 1. Используя настоящее учебное пособие изучить особенно-

сти организации цикла исполнения команд микропроцессора К580ВМ80, устройство и принципы работы УМК и сменного блока для снятия временных диаграмм (блока М1).

2. Составить и закодировать программу из 2–3 команд, реализующую циклическое исполнение исследуемой команды. Варианты команд приведены в табл. 5. Для заданной команды нарисовать ожидаемую временную диаграмму сигналов: Ф1, Ф2,

СИНХР(SYNC), А15 – А0, D7 – D0, ST7 – ST0, MRDC , MWTC ,

ЧТ(DBIN). Сигналы должны быть представлены на временной диаграмме в том виде, как они приведены в табл. 1. Если в табл. 1

приведено обозначение с инверсией (например, MRDC ), то на временной диаграмме сигнал также должен быть с инверсией (с нулевым действующим значением). Если в табл. 1 приведено обозначение без инверсии (например, DBIN), то на временной диаграмме сигнал также должен быть представлен без инверсии (с единичным действующим значением). Сигналы А15 – А0, D7 – D0, ST7 – ST0 следует рисовать так, как они представлены на рис. 9.

–51 –

3.Составить и закодировать программу из 3–4 команд, реализующую цикл, в котором исполняются машинные циклы записи в память и чтения из памяти байта 0FН по адресу 082x, где x

–шестнадцатеричный код номера варианта (взятый по модулю 16). Для машинных циклов чтения и записи по адресу 082x нарисовать ожидаемые временные диаграммы – заготовки для снятия микровременных диаграмм.

РАБОЧЕЕ ЗАДАНИЕ

1.Загрузить подготовленную по п. 2 подготовки к работе программу в УМК и убедиться в правильности ее работы в пошаговом режиме.

2.Перевести УМК в непрерывный режим и запустить исполнение программы. Подключить осциллограф как показано на рис. 13 к блоку М1 и установить переключатели «АДРЕС», «ЦИКЛЫ», «ТАКТЫ» в положение для развертки на экране первого машинного цикла заданной команды. Снять временные диаграммы

сигналов F2, СИНХР(SYNC), А15 – А0, D7 – D0, ST7 – ST0,

MRDC , MWTC , ЧТ(DBIN). Повторить перечисленные действия для остальных машинных циклов заданной команды.

3.Загрузить подготовленную по п. 3 подготовки к работе программу в УМК и убедиться в правильности ее работы в пошаговом режиме.

4.Перевести УМК в непрерывный режим и запустить исполнение программы. Подключить осциллограф к блоку М1 и установить переключатели «АДРЕС», «ЦИКЛЫ», «ТАКТЫ» для развертки от начала цикла чтения из ячейки 082x. Выбрать длительность развертки так, чтобы на экране были размещены сигналы только первого такта цикла. Снять осциллограммы

– 52 –

сигналов СИНХР(SYNC), А15 – А0, D7 – D0, ST7 – ST0, MRDC ,

MWTC , ЧТ(DBIN) и измерить задержки моментов их изменений относительно сигнала F2. Данные действия повторить для всех остальных тактов цикла.

СОДЕРЖАНИЕ ОТЧЕТА

−тексты и коды программ;

−теоретическая и снятая временные диаграммы машинных циклов заданной команды;

−микровременные диаграммы машинных циклов чтения и записи в память.

Таблица 5

Варианты задания к лабораторной работе № 3

Вариант |

Команда |

Вариант |

Команда |

1 |

MOV M, r |

11 |

SUI data |

2 |

MOV r, M |

12 |

SBB M |

3 |

MVI r, data |

13 |

SBI data |

4 |

ADI data |

14 |

INR M |

5 |

ADD M |

15 |

DCR M |

6 |

ADC M |

16 |

MVI M, data |

7 |

ACI data |

17 |

ANA M |

8 |

LDAX rp |

18 |

ANI data |

9 |

STAX rp |

19 |

ORA M |

10 |

SUB M |

20 |

ORI data |

–53 –

5.4.Организация различных режимов работы

ипрерываний в УМК

ЦЕЛЬ РАБОТЫ: изучение различных режимов работы процессора УМК и системы прерываний.

ОСОБЕННОСТИ ОРГАНИЗАЦИИ РАЗЛИЧНЫХ РЕЖИМОВ РАБОТЫ И ПРЕРЫВАНИЙ В ПРОЦЕССОРЕ УМК

В разд. 5.3 настоящего учебного пособия перечислены возможные режимы работы микропроцессора К580ВМ80 и приведены условия перехода к каждому из режимов. В УМК на вход ЗХВ(HOLD), предназначенный для подачи сигнала перехода в режим захвата, подана константа «0», запрещающая такой переход. На вход ГТ(READY) подан сигнал со схемы организации пошаговых режимов. Таким образом, в процессоре УМК возможно исполнение (кроме основного режима) только режимов ожидания и останова. Переход в режим останова может быть выполнен программным путем по команде HLT. Выход из режима останова возможен только путем прерывания или начальной установки микропроцессора. В режим ожидания микропроцессор может войти только при переключении УМК в пошаговый режим.

УМК в целом может функционировать в пошаговых (покомандный и поцикловый) и непрерывном режимах. Выбор режима осуществляется клавишами РБ/ШГ и КМ/ЦК. Управление программным запретом пошаговых режимов осуществляется младшим разрядом порта 0FCH.

Необходимо отметить, что режимы основной, ожидания, захвата и останова относятся к микропроцессору К580ВМ80, а режимы работы пошаговый и непрерывный – к УМК в целом.

– 54 –

Описание системы прерываний УМК приведено в разд. 2.3, организации прерывания в микропроцессоре К580ВМ80 – в разд. 5.3 настоящего учебного пособия. Переход к прерывающей программе

вУМК может быть инициирован программно (когда команда RST 7 находится в тексте программы) и по внешнему запросу (по сигналу от клавиши ПР).

При поступлении запроса на прерывание от клавиши ПР, УМК после исполнения всех машинных циклов текущей команды переходит к машинному циклу «Прерывание (выборка первого байта команды)». В этом случае микропроцессор вместо очередной команды принимает команду RST 7 (код FFH), по которой осуществляется запись текущего состояния программного счетчика

встек и выполняется безусловный переход по адресу 0038Н. Таким образом, команда RST 7 выполняет те же действия, что и команда CALL 0038Н, но команда RST имеет длину 1 байт. С адреса 0038Н начинается прерывающая программа, подробное описание действий которой приведено в разд. 3.3 настоящего учебного пособия. Прерванная программа может быть вновь запущена с адреса, где она была прервана, путем выполнения процедуры монитора «СТ» без первого параметра.

ПОДГОТОВКА К РАБОТЕ

1.Используя настоящее учебное пособие изучить особенности организации пошаговых режимов и прерываний в УМК.

2.Представить в виде машинных кодов программы, приведенные в рабочем задании к настоящей работе.

– 55 –

РАБОЧЕЕ ЗАДАНИЕ 1. Ввести и запустить на исполнение в пошаговом режиме

программу:

MVI A,01H

OUT 0FCH NEХT: NOP

JMP NEХT

Выполнить цикл несколько раз. Заменить первую команду программы на

MVI A,00H

Выполнить те же действия для измененной программы. Пояснить отличия.

2. Ввести и запустить на исполнение в непрерывном режиме программу:

EI NEХT: NOP

JMP NEХT

Прервать исполнение программы нажатием клавиши ПР. Заменить первую команду программы на

DI

Выполнить те же действия для измененной программы. Пояснить отличия.

3. Ввести и запустить на исполнение в непрерывном режиме программу:

EI

HLT

Прервать исполнение программы нажатием клавиши ПР. Заменить первую команду программы на

DI

Выполнить те же действия для измененной программы. Пояснить отличия.

–56 –

4.Ввести и запустить на исполнение в непрерывном режиме программу:

EI NOP

RST 7

Заменить первую команду программы на

DI

Выполнить те же действия для измененной программы. Пояснить результаты.

5. Ввести и запустить на исполнение в непрерывном режиме программу:

NEХT: MVI A,0FFH MVI A,00H JMP NEХT

Прервать исполнение программы нажатием клавиши ПР. Определить, между какими двумя командами произошло прерывание. Прочитать первые две ячейки стека пользователя (адреса 0ВС8Н, 0ВС9Н). Пояснить результат.

6. Ввести и запустить на исполнение в непрерывном режиме программу:

NEXT: NOP EI NOP NOP

JMP NEXT

Не менее 20 раз, прерывая исполнение программы нажатием клавиши ПР, и продолжая исполнение директивой СТ без параметров, фиксировать адреса команд, перед которыми произошло прерывание. Подсчитать, сколько раз произошло прерывание перед каждой из команд. Пояснить результат.

СОДЕРЖАНИЕ ОТЧЕТА

−схема пошаговых режимов и схема прерываний УМК;

−кодированные программы и результаты.

–57 –

6.ОРГАНИЗАЦИЯ ПАРАЛЛЕЛЬНОГО ВВОДА-ВЫВОДА

6.1. БИС программируемого параллельного интерфейса К580ВВ55А

Структурная схема БИС программируемого параллельного интерфейса (ППИ) представлена на рис. 14. В состав ППИ входят:

−два 8-разрядных двунаправленных канала ввода-вывода РА7–РА0 и РВ7–РВ0;

−два 4-разрядных двунаправленных канала РС7–РС4 и РС3–РС0, которые могут быть использованы как один 8-разрядный канал РС7–РС0;

−двунаправленный буфер данных для связи с шиной данных микроЭВМ;

−устройство управления, осуществляющее адресную выборку ППИ и реализацию различных режимов настройки и обмена информацией между каналами ППИ и микроЭВМ.

Все устройства ППИ соединены между собой внутренней 8-разрядной информационной шиной. В состав ППИ включены четыре адресуемых кодом А1–А0 8-разрядных регистра – по одному на каждый из трех каналов A, B, C и регистр управляющего слова, входящий в состав устройства управления. В табл. 6 приведены

значения сигналов CS , RD , WR , А1, А0 для обращения ко всем перечисленным регистрам.

Подключение ППИ к шинам микроЭВМ обычно осуществляется следующим образом:

− входы А1, А0 подключаются к соответствующим разрядам шины адреса. При этом три канала и регистр управляющего слова адресуются как четыре 8-разрядных порта со смежными адресами;

A0

A1

CS

WR

RD

RESET

D7-D0

|

– 58 – |

|

|

PA7-PA0 |

|

Устройство |

Канал А |

|

управления |

|

|

|

PB7-PB0 |

|

|

Канал B |

|

|

PC3-PC0 |

|

|

Канал C [3-0] |

|

|

PC7-PC4 |

|

Буфер |

Канал C [7-4] |

|

данных |

||

|

Рис. 14. Структурная схема ППИ

|

|

|

|

|

|

|

|

|

– 59 – |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 6 |

|

|

|

|

|

|

Операции с ППИ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сигналы управления |

|

|

|

|

|

Операция |

||||

CS |

А1 |

А0 |

|

WR |

RD |

|

|

||||||

1 |

|

~ |

~ |

|

~ |

|

~ |

|

|

|

Отсутствие операции |

||

0 |

|

~ |

~ |

|

1 |

|

1 |

|

|

|

Отсутствие операции |

||

0 |

|

0 |

0 |

|

1 |

|

0 |

|

|

|

Чтение из канала А |

||

0 |

|

0 |

0 |

|

0 |

|

1 |

|

|

|

Запись в канал А |

||

0 |

|

0 |

1 |

|

1 |

|

0 |

|

|

|

Чтение из канала В |

||

0 |

|

0 |

1 |

|

0 |

|

1 |

|

|

|

Запись в канал В |

||

0 |

|

1 |

0 |

|

1 |

|

0 |

|

|

|

Чтение из канала С |

||

0 |

|

1 |

0 |

|

0 |

|

1 |

|

|

|

Запись в канал С |

||

0 |

|

1 |

1 |

|

0 |

|

1 |

|

|

|

Запись управляющего слова |

||

−вход CS подключается к выходу дешифратора старших линий адреса. На вход такого дешифратора могут быть поданы разряды шины адреса А7–А2 (разрядность адреса порта в микропроцессоре К580ВМ80 – 8 бит);

−вход RD подключается к сигналу IORC шины управле-

ния;

−вход WR подключается к сигналу IOWC шины управле-

ния;

−вход RESET подключается к сигналу RESET шины управления;

−двунаправленные выводы D7–D0 подключаются к шине

данных.