- •Розділ VII регістри

- •7.1. Загальне поняття про регістри

- •7.2. Регістри пам’яті

- •7.3. Конвеєрні пристрої

- •7.4. Регістри зсуву

- •7.5. Приклади мікросхем регістрів та особливості їх використання

- •7.5.1. Паралельні регістри

- •7.5.2. Регістрові файли

- •7.5.3. Послідовні регістри

- •7.6. Напрямки (області) використання регістрів

- •7.6.1. Забезпечення обміну інформацією у послідовному форматі

- •7.6.2. Регістрові лічильники імпульсів (розподілювачі)

- •7.6.3. Лічильники Джонсона

- •7.6.4. Поліноміальні пристрої кодування та фільтрації

- •7.6.5. Системи контролю цифрової апаратури

- •7.6.6. Використання регістрів для обчислення контрольної суми

- •Контрольні питання

- •Вправи і завдання

7.5. Приклади мікросхем регістрів та особливості їх використання

7.5.1. Паралельні регістри

Найпростішими регістрами паралельного типу є набори тригерів D-типу – наприклад, мікросхеми КР1533ТМ7 (SN74LS75), що містять чотири D-тригери; ТМ8 (ALS175), що місять чотири D-тригери з прямими та інверсними виходами; ТМ9 (ALS174) з шістьома синхронними D-тригерами.

У групі регістрів паралельного типу близькими структурами до вказаних наборів тригерів є мікросхеми КР1533ИР22, КР1533ИР23, КР1533ИР37. Вони орієнтовані для роботи на низькоомне навантаження або навантаження з великою ємністю.

Функціональна схема мікросхема мікросхеми ИР22 приведена на рис. 7.16.

Рис. 7.16

Регістр призначений для зберігання

восьмирозрядного слова, що записується

та зчитується у паралельному форматі.

Мікросхема регістра містить вісім

статичних синхронних D-тригерах,

запис інформації в які забезпечується

через паралельну шину даних D0…D7

за імпульсом синхросигналу (тобто при

C = 1). При записі коду та його

зберіганні на вході

![]() повинен бути сигнал низького рівня.

Вихідна шина даних Q0…Q7

приєднана до виходів тригерів через

буферні підсилювачі з трьома станами

виходів, що забезпечує високу

навантажувальну здібність. Оскільки

при високому рівні синхросигналу

інформація з D-входів передається

безпосередньо на вихід, то регістр

забезпечує високу швидкодію при записі

інформації та керуванні її передачею.

Тому ці регістри знаходять широке

використання в мікропроцесорних системах

з магістральною організацією. При C = 0

регістр знаходиться у режимі зберігання.

Для переводу виходів мікросхеми у Z-стан

необхідно на вхід

подати високий рівень сигналу, при цьому

стан інших входів байдужий. Система

керування Z-станом побудована так,

що при зниженні напруги живлення до 3 В

вона автоматично переводить мікросхему

у третій стан незалежно від інформації

на вході

.

Така особливість виключає можливість

появи крізних струмів в інформаційних

магістралях. Завдяки такій властивості,

високій швидкодії та навантажувальній

здібності мікросхема, що розглядається,

знаходить широке використання в

мікропроцесорних системах у якості

буферного регістра, магістрального

пристрою для прийому і передачі інформації

та в інших призначеннях.

повинен бути сигнал низького рівня.

Вихідна шина даних Q0…Q7

приєднана до виходів тригерів через

буферні підсилювачі з трьома станами

виходів, що забезпечує високу

навантажувальну здібність. Оскільки

при високому рівні синхросигналу

інформація з D-входів передається

безпосередньо на вихід, то регістр

забезпечує високу швидкодію при записі

інформації та керуванні її передачею.

Тому ці регістри знаходять широке

використання в мікропроцесорних системах

з магістральною організацією. При C = 0

регістр знаходиться у режимі зберігання.

Для переводу виходів мікросхеми у Z-стан

необхідно на вхід

подати високий рівень сигналу, при цьому

стан інших входів байдужий. Система

керування Z-станом побудована так,

що при зниженні напруги живлення до 3 В

вона автоматично переводить мікросхему

у третій стан незалежно від інформації

на вході

.

Така особливість виключає можливість

появи крізних струмів в інформаційних

магістралях. Завдяки такій властивості,

високій швидкодії та навантажувальній

здібності мікросхема, що розглядається,

знаходить широке використання в

мікропроцесорних системах у якості

буферного регістра, магістрального

пристрою для прийому і передачі інформації

та в інших призначеннях.

Особливість регістрів ИР23 та ИР37 полягає

лише в тому, що запис інформації в тригери

забезпечується за фронтом синхросигналу.

Оскільки розрахункова тривалість фронту

синхроімпульсу менша інтервалу часу

передачі інформаційного сигналу з

D-входу тригера на його вихід, то

регістр ИР23 часто використовується в

якості зсувного. Для цього вихід

попереднього розряду елемента пам’яті

(наприклад, Q0 ) до входу

послідуючого (D1). При такому

з’єднанні регістр має можливість

забезпечувати послідовний запис

інформації (через D0) і зчитування

(через Q7). Як послідовний,

регістр ИР23 широко використовується в

апаратно-програмних засобах відображення

інформації (світлодіодних панно, панелях,

біжучих рядках тощо). Завдяки тому, що

струм виходів мікросхеми

![]() мА,

мА,

![]() мА,

світлодіоди можуть бути приєднані

безпосередньо на виходи Q0…Q7 .

мА,

світлодіоди можуть бути приєднані

безпосередньо на виходи Q0…Q7 .

Мікросхема КР1533ИР27 (SN74LS377)

є близьким малопотужним аналогом до

ИР23. Він не має Z-стану, але для

забезпечення запису інформації за

фронтом С-сигналу необхідно на вхід

![]() подати сигнал низького рівня. Він також

може працювати в режимі однонаправленого

зсувного регістра, але малопотужні

виходи Q (струм

подати сигнал низького рівня. Він також

може працювати в режимі однонаправленого

зсувного регістра, але малопотужні

виходи Q (струм

![]() мА)

обмежують його використання.

мА)

обмежують його використання.

Мікросхема КР1533ИР33 (SN74ALS573) є повним аналогом регістра ИР22.

Мікросхема КР1533ИР35 близька до мікросхем

ИР23 та ИР27, але, на відміну від них, має

загальний вхід обнуління

![]() ,

який є асинхронним і пріоритетним перед

іншими входами. Виходи мікросхеми

малопотужні.

,

який є асинхронним і пріоритетним перед

іншими входами. Виходи мікросхеми

малопотужні.

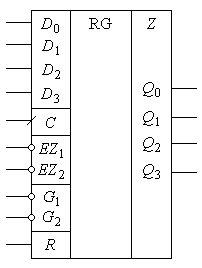

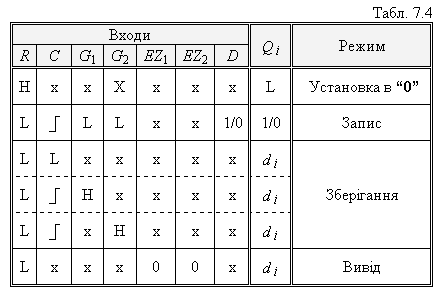

Мікросхема КР1533ИР15 (SN74LS173A) – це чотирьохрозрядний регістр D-типу, який має по виходу три стани, а також прямий вхід обнуління R. Умовне позначення мікросхеми приведено на рис. 7.17, а таблиця станів, що відображає режими його роботи, – у Табл. 7.4.

Рис. 7.17 |

|

Установка тригерів у нуль забезпечується

високим рівнем сигналу R незалежно

від рівнів інших сигналів. Виведення

інформації на шину Q можливе лише

за умови

![]() .

Високий рівень сигналу на будь-якому з

цих входів переводить виходи мікросхеми

у Z-стан, але при цьому режими запису

і обнуління працюють незалежно. Входи

G1 і G2 є входами

дозволу запису. Високий рівень сигналу

на будь-якому з цих входів блокує режим

запису.

.

Високий рівень сигналу на будь-якому з

цих входів переводить виходи мікросхеми

у Z-стан, але при цьому режими запису

і обнуління працюють незалежно. Входи

G1 і G2 є входами

дозволу запису. Високий рівень сигналу

на будь-якому з цих входів блокує режим

запису.

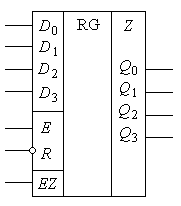

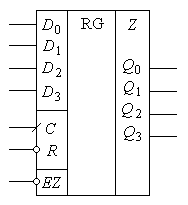

Чотирьохрозрядними є також буферні регістри у мікросхемах КР1533ИР34 (SN74ALS873) та КР1533ИР38 (SN74ALS874). У кожній з мікросхем містяться по 2 регістри, абсолютно незалежні. Умовне позначення регістра першої мікросхеми приведене на рис. 7.18, а ; другої – на рис. 7.18, б.

а |

б |

Рис. 7.18 |

|

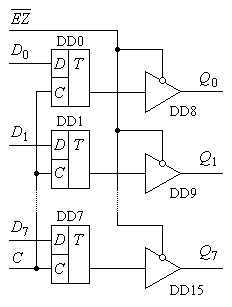

Буферизовані виходи з Z-станом в обох мікросхемах майже ідентичні. Вони мають підвищену навантажувальну здібність ( мА), достатню для роботи в якості магістральних приймачів / передавачів. Єдина різниця полягає в тому, що регістри мікросхеми ИР34 переводяться у Z-стан за високим рівнем сигналу EZ, а ИР38 – за низьким. Регістри обох мікросхем спроектовані так, що при пониженні напруги живлення до 3 В виходи переводяться у Z-стан з метою виключення появи в магістралях наскрізних струмів. Входи регістрів обох мікросхем також близькі за функціональними властивостями. Різниця полягає лише в тому, що в ИР34 вхід дозволу запису інформації статичний і запис інформації забезпечується високим рівнем сигналу, а у мікросхемі ИР38 вхід динамічний, а запис забезпечується за фронтом. Обидві мікросхеми мають можливість шляхом запаралелення їх розрядів створити один регістр на вісім розрядів. У мікросхемі ИР38, за аналогією з раніше описаним способом, можна створити режим послідовного по входу регістра на вісім розрядів, фактично повторюючи описані вище режими регістра ИР23.

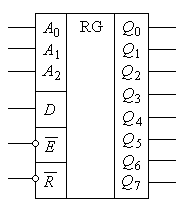

Мікросхема КР1533ИР30 – це восьмирозрядний регістр зберігання з адресацією. Він містить у собі вісім D-тригерів з прямими виходами, але запис інформації в кожен з них відбувається через один D-вхід шляхом адресного звернення по шині А (A2 A1 A0). Умовне позначення регістра приведене на рис. 7.19.

|

|

Рис. 7.19 |

|

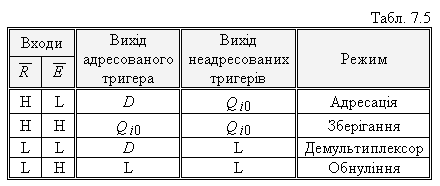

Адресація до кожного з тригерів, що мають виходи Q0…Q7 , відбувається у відповідності до послідовності мінтермів двійкового коду 0…7 на три розряди. Режими роботи регістра пояснюються таблицею станів (Табл. 7.5). Вхід – вхід дозволу запису.

Для виключення похибок у роботі мікросхеми

на вході

![]() необхідно тримати сигнал високого рівня

при зміні адресних сигналів.

необхідно тримати сигнал високого рівня

при зміні адресних сигналів.

У режимі дешифратора / демультиплексора

на адресований вхід поступає інформація

зі входу D-. При цьому решта виходів

знаходиться у стані низького рівня

напруги. Така особливість можлива тому,

що, по-перше, у режимі демультиплексування

одночасно з адресними сигналами і

сигналом дозволу

діє низький рівень сигналу на вході

,

а, по-друге, D-тригери побудовані

так, що вхід

блокується при подачі безпосередньо

на тригер сигналу дозволу завантаження

![]() .

.