- •Розділ VII регістри

- •7.1. Загальне поняття про регістри

- •7.2. Регістри пам’яті

- •7.3. Конвеєрні пристрої

- •7.4. Регістри зсуву

- •7.5. Приклади мікросхем регістрів та особливості їх використання

- •7.5.1. Паралельні регістри

- •7.5.2. Регістрові файли

- •7.5.3. Послідовні регістри

- •7.6. Напрямки (області) використання регістрів

- •7.6.1. Забезпечення обміну інформацією у послідовному форматі

- •7.6.2. Регістрові лічильники імпульсів (розподілювачі)

- •7.6.3. Лічильники Джонсона

- •7.6.4. Поліноміальні пристрої кодування та фільтрації

- •7.6.5. Системи контролю цифрової апаратури

- •7.6.6. Використання регістрів для обчислення контрольної суми

- •Контрольні питання

- •Вправи і завдання

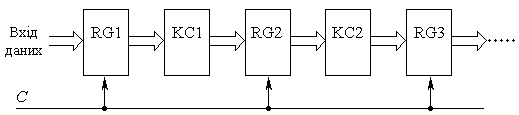

7.3. Конвеєрні пристрої

При реалізації складних логічних задач складність комбінаційної схемотехніки суттєво зростає. Зростають також величини часових затримок у комбінаційних схемах, що, як відмічалося вище (див. Розділ III), може приводити до критичних змагань (“гонок”). Для боротьби з ними використовується синхронізація, яка забезпечується тригерними пристроями. Якщо кількість виходів КС зростає, то зростає і кількість розділюючих синхронних тригерів. У такому випадку замість тригерів можуть бути встановлені паралельні регістри пам’яті, внаслідок чого принцип обробки інформації комбінаційними схемами може бути принципово змінений, оскільки з’являється можливість конвеєрної обробки інформації.

Структурна схема конвеєра для обробки інформації приведена на рис. 7.9.

Рис. 7.9

Конвеєр складається з буферних регістрів RG1, RG2 та послідуючими за ними виконавчими схемами. Виконавчі схеми можуть бути комбінаційними або послідовнісними і разом з вхідними регістрами називаються стадіями. Стадія виконує конкретну операцію і видає проміжний результат на послідуючу за нею стадію. Завершує схему вихідний буферний регістр.

Сигнал таймера подається одночасно на кожен буферний регістр, і за кожним імпульсом таймера кожна стадія передає свої проміжні результати на вхідний регістр наступної стадії. Кінцевий результат отримується після того, як вхідні дані будуть послідовно оброблені в кожній стадії. Період імпульсів таймера повинен бути достатнім для проходження оброблюваними даними найповільнішої стадії, включаючи сюди інтервал часу для запису проміжних результатів у проміжний регістр. Тобто тактовий інтервал часу Tk складається з часу TB – часу виконання операції та TЗ – часу запису та зберігання в буфері, тобто:

Tk = TB + TЗ ≈ TЗ ,

оскільки TЗ >> TB .

Час виконання n задач Tn , які подаються послідовно на вхідну стадію конвеєра, що має m стадій, теоретично знаходиться за формулою:

Tn = m × Tk + (n – 1) × Tk ,

де m × Tk – час, необхідний для виконання першої вхідної задачі;

(n – 1) × Tk – час, необхідний для виконання решти задач.

З формули витікає, що після завантаження конвеєра він оброблятиме кожну задачу протягом одного такту Tk , і тому при розв’язанні типових задач швидкість виконання операцій буде в m разів більшою, порівняно з безконвеєрною обробкою.

Конвеєрна обробка інформації використовується в тих ситуаціях, коли необхідна однотипна обробка вхідної інформації. Конвеєри широко використовуються як у спеціалізованих процесорах (наприклад, сигнальних), так і в процесорах загального призначення.

Сучасні конвеєрні засоби обробки інформації є досить розвиненими. У процесорах часто встановлюється декілька конвеєрів, які можуть гнучко переналагоджуватись у процесі роботи.

7.4. Регістри зсуву

Регістрами зсуву називаються такі регістри, вміст яких при подачі керуючих сигналів може змінюватись у бік старших чи молодших розрядів. Такі пристрої складаються з кола динамічних тригерів, спрацьовування яких виконується за фронтом або спадом синхронізуючого імпульсу C-. У ряді літературних джерел останніх років – наприклад, в [] – активно використовується розподіл тригерів на “прозорі” та “непрозорі”.

Під терміном “прозорість” мається на увазі властивість тригера при активному рівні сигналу на вході D- адекватно з його типом відслідковувати на виході всі перемикання керуючих входів; якщо це D-тригер, то просто повторюється стан D-входу. Іншими словами, цим терміном охоплюються тригери зі статичним входом.

“Непрозорість” тригерів – це їх властивість навіть при активному рівні сигналу на С-вході не передавати на вихід змін керуючих входів, що з’являються вслід за перемикаючим фронтом. Цією властивістю охоплюються всі тригери, які перемикаються за фронтом або зрізом синхроімпульсу, що поступає на вхід С-.

Складність застосування статичних тригерів у зсувних регістрах обумовлена тим, що при активному рівні сигналу на синхронізуючих входах всіх тригерів перемикання одного з них приведе до перемикання послідуючих, а їх кількість визначатиметься тривалістю синхросигналу та швидкодією тригерів. Однак під цим не слід розуміти, що застосування статичних тригерів у схемах з послідовним зсувом принципово неможливе. Така можливість з’являється, наприклад, при використанні двофазної синхронізації, яка дозволяє розділити у часі процеси перемикання на окремих ділянках схеми. Прикладом ефективного застосування двофазної синхронізації може служити мікропроцесорний комплект ВІС серії К580. В інтегральних схемах середнього ступеню інтеграції використовується однофазна синхронізація.

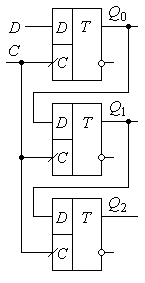

На рис. 7.10 наведена схема зсувного регістра, побудованого на D-тригерах. Інформація, призначена для запису в регістр і представлена у послідовному форматі, поступає на D-вхід першого тригера. Її запис у перший та наступні тригери здійснюється за фронтом синхроімпульсу, що поступає одночасно на входи С- всіх тригерів. Зчитування інформації виконується також у послідовному форматі з виходу Q останнього тригера шляхом подання на синхровходи серії імпульсів. У паралельному форматі вона може бути зчитана з виводів Q тригерів, якщо такі виводи передбачені в мікросхемі регістра. За подібною схемою побудований регістр 564ИР2, що містить два незалежні чотирьохрозрядні однонаправлені регістри.

Рис. 7.10

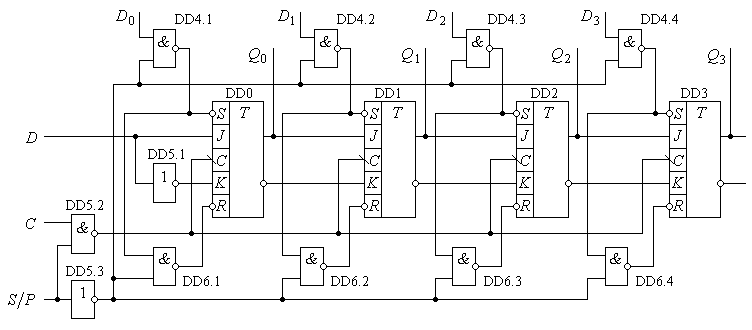

На рис. 7.11 приводиться варіант схеми зсувного регістра на JK-тригерах, кожен з яких працює в режимі D-тригера. Цей режим забезпечується для тригерів DD1…DD3 протифазними виходами попередніх, а D-режим тригера DD0 забезпечується інвертором DD5.1. Доповнений логічними елементами DD4.1…DD4.4, він дозволяє виконувати послідовне та паралельне введення інформації, а також послідовне або паралельне її виведення.

Рис. 7.11

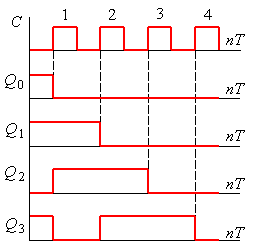

Часова діаграма, яку наведено на рис. 7.12, ілюструє процедуру послідовного введення по входу S- за наявності тактових імпульсів С- та логічної одиниці на вході вибору режимів введення: S / P = 1.

Рис. 7.12

Розглянемо особливості роботи регістра при послідовному введенні інформації. Припустимо, що в регістр послідовно вводиться, починаючи з молодшого розряду, двійковий код 1101, який подається синхронно з тактовими імпульсами С-. Враховуючи, що тригери повинні спрацьовувати за зрізом вхідного сигналу, який подається на їх С-входи, а синхросигнал регістра інвертується елементом DD5.2, запис інформації забезпечуватиметься за фронтом синхросигналу регістра. При цьому записувана у тригери інформація повинна бути підготовленою до подачі синхросигналу (див. Розділ IV). Наприклад, для тригерів серії КР1533 інтервал часу підготовки повинен бути не меншим 20 нс. Оскільки всі тригери регістра сприймають синхросигнал одночасно, то у кожний з них запишеться інформація, що мала місце на інформаційних входах безпосередньо перед зрізом синхросигналу тригера (фронтом синхросигналу регістра). Через час затримки розповсюдження сигналу (для КР1533 вона складає 15 нс) інформаційний сигнал буде записаний і з’явиться на Q-виході тригера.

Виходячи з вищесказаного, за фронтом першого тактового імпульсу С- в DD0 буде записана одиниця молодшого розряду, а у решту тригерів перезапишуться нулі з прямих виходів попередніх тригерів (див. рис. 7.12). Перед приходом другого синхросигналу на входах DD0 і DD1 будуть присутні сигнали високого рівня, а на входах DD2 і DD3 – низького. Тому за фронтом другого синхросигналу в перший тригер DD0 знову перезапишеться “1”, в другий DD1 – також “1” з виходу Q0 , а в DD2 і DD3 будуть записані нулі відповідно з виходів Q1 і Q2 . Аналогічно, за третім синхросигналом “1” з виходів Q0 і Q1 перемістяться на виходи тригерів DD1 і DD2, а в DD0 буде записаний “0” з D-входу регістра. Так за кожним синхросигналом у регістрі матиме місце зсув інформації на один розряд вправо. Після чотирьох тактових імпульсів код на виходах Q0 …Q3 відповідатиме вхідному коду і може бути зчитаний зовнішнім пристроєм. Розрядність регістра може бути підвищена нарощуванням подібних пристроїв. Нарощування здійснюється шляхом під єднання виходу Q3 попереднього регістра з входом D- послідуючого з відповідним об’єднанням синхронізуючих та керуючих входів.

У регістрі, виготовленому відповідно до розглянутої схеми, є можливість перетворювати інформацію, задану в послідовному форматі, у паралельний формат, тобто виконувати функцію демультиплексора. Але перевага регістра при виконанні такої функції полягає в тому, що інформація в паралельному форматі може зчитуватись одночасно в усіх розрядах, а не рознесена у часі, як у демультиплексорах. До того ж, інформація запам’ятовується і може бути зчитана багаторазово.

При наявності в регістрі JK-тригерів з асинхронними R- і S- входами можна забезпечити за допомогою допоміжної логіки (ЛЕ DD4) паралельний запис інформації D0…D3 у кожен з тригерів. Запис забезпечується асинхронно за низьким рівнем керуючого сигналу S / P (Serial / Parallel). Тобто записати інформацію в паралельному форматі можна в інтервалі часу між двома синхроімпульсами.

Зчитування інформації у послідовному форматі забезпечується подачею на С-вхід серії синхросигналів у кількості, що дорівнює розрядності регістра. Зі сказаного витікає, що регістр зсуву може виконувати функцію мультиплексора з запам’ятовуванням.

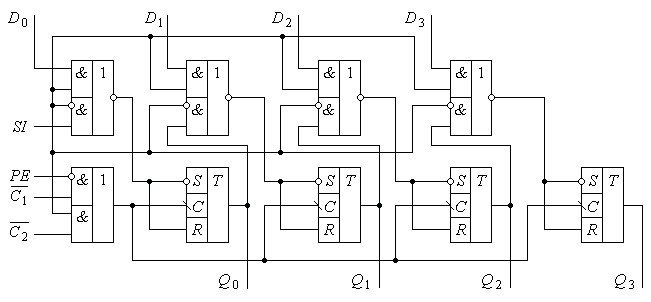

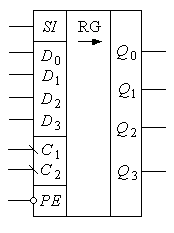

Запис інформації в паралельному форматі може бути забезпеченим не тільки при використанні у регістрах JK-тригерів, а також при використанні RS- та D-тригерів. Прикладом такого регістра може бути мікросхема ИР1, функціональна схема якої приведена на рис. 7.13, а, а умовне зображення – на рис. 7.13, б.

а |

б |

Рис. 7.13

Кожен розряд регістра виготовлений на

основі синхронного RS-тригера

(DD0…DD3), що працює в режимі D-тригера,

зі зворотним динамічним входом

синхронізації С-. Регістр має чотири

входи даних D0…D3 для

завантаження інформації в паралельному

форматі і один SI – для завантаження

у послідовному. Регістр має два синхровходи

–

![]() і

і

![]() .

Синхровхід

працює при PE = 0 і забезпечує

синхронне послідовне завантаження

регістра з входу SI, а також зсув

вправо. При PE = 1 регістр працює

за тактовим сигналом

і за зрізом його завантажує дані з

паралельних входів D0…D3 .

Режими роботи регістра задаються його

таблицею станів. Ступінь деталізації

таблиці може бути різною, але вона

повинна бути достатньою для того, щоб

зрозуміти всі особливості взаємодії

сигналів для кожного з режимів роботи

регістра.

.

Синхровхід

працює при PE = 0 і забезпечує

синхронне послідовне завантаження

регістра з входу SI, а також зсув

вправо. При PE = 1 регістр працює

за тактовим сигналом

і за зрізом його завантажує дані з

паралельних входів D0…D3 .

Режими роботи регістра задаються його

таблицею станів. Ступінь деталізації

таблиці може бути різною, але вона

повинна бути достатньою для того, щоб

зрозуміти всі особливості взаємодії

сигналів для кожного з режимів роботи

регістра.

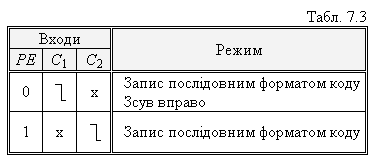

Оскільки в регістрі, що розглядається, є лише три керуючі сигнали, взаємозв’язані між собою, то достатньою є скорочена таблиця станів (Табл. 7.3).

Для забезпечення зсуву інформації вліво необхідно в регістрі створити зв’язки, які могли б дозволити переміщувати інформацію з правого тригера в лівий, а також передбачити два послідовних входи: DR – вхід для прийому інформації, що поступає в регістр зі сторони молодшого розряду та зсувається вправо, та DL – вхід для прийому інформації, що поступає в регістр зі сторони молодшого розряду та зсувається вліво. Ці входи використовуються і при нарощуванні регістрів: DR приєднуються до входу старшого розряду сусідньої молодшої секції загального регістру; DL – приєднується до виходу Q0 молодшого розряду сусідньої старшої секції загального регістра.

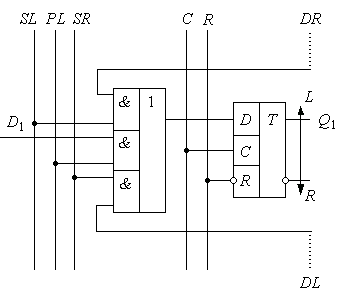

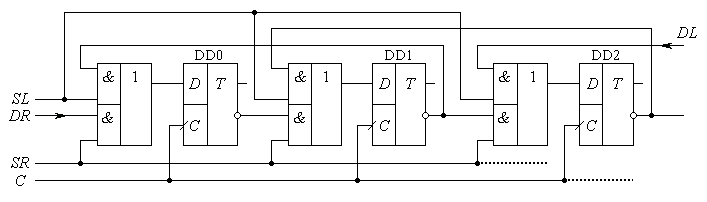

Функціональна схема одного розряду двонаправленого регістра зсуву з можливістю паралельного завантаженні приведена на рис. 7.14.

Рис. 7.14

До D-входу кожного тригера регістра приєднується вихід мультиплексора, який за допомогою керуючих сигналів SL (Shift Left – зсув ліворуч), SR (Shift Right – зсув праворуч) і PL (Parallel Load – паралельне завантаження) приєднує вхід i-го тригера відповідно до виходу послідуючого тригера, до виходу попереднього тригера або до i-го розряду паралельного завантаження. За сигналом синхронізації у тригер завантажуються відповідні дані. Вихід i-го тригера приєднується до відповідних входів мультиплексорів сусідніх розрядів (напрямки L, R). У мікросхемах регістрів входи SL, PL, SR не виводяться з корпусу мікросхеми, а керування ними здійснюється через дешифратор режимів.

На рис. 7.15 приводиться спрощений приклад з’єднання трьох тригерів для забезпечення зсуву вліво та вправо відповідно до керуючих сигналів SL та SR.

Рис. 7.15

З’єднання виходу послідуючого тригера з входом попереднього може бути виконано і за допомогою зовнішнього монтажу виводів у мікросхемах зсувних регістрів з паралельним введенням і виведенням інформації. Наприклад, у розглянутому регістрі ИР1 для забезпечення зсуву вліво необхідно зробити такі зовнішні зв’язки: Q3 з’єднати з D2 ; Q2 з D1 ; Q1 з D0 . Вхід D3 необхідно використовувати як вхід DL для введення інформації з старшого розряду зі зсувом вліво. Зсув вліво забезпечуватиметься за синхросигналом С-.

Забезпечення можливості зсувати записані дані вліво-вправо відкриває простий спосіб ділення та множення даних на коефіцієнт (дільник / множник), кратний 2. Дійсно, зміщення числа на один розряд вліво у межах розрядної сітки еквівалентно множенню на 2, а зміщення на один розряд вправо – діленню на 2 (наприклад, 1010 ↔ 0101).