- •Розділ VIII запам’ятовуючі пристрої

- •8.1. Постійні запам’ятовуючі пристрої (принципи побудови, типи, характеристики)

- •8.1.1. Одновимірні пзп

- •8.1.2. Двовимірне декодування в пзп

- •8.1.3. Мікросхеми пзп

- •8.2. Репрограмовані пзп

- •8.2.1. Принципи побудови репрограмованих пзп

- •8.2.2. Мікросхеми рпзп

- •8.2.2.1. Паралельні еерrom

- •8.2.2.2. Послідовні eeprom

- •8.2.2.3. Eeprom з трьохпровідною послідовною шиною

- •8.2.3. Флеш-пам’ять

- •8.2.3.1. Основи побудови флеш пам’яті

- •8.2.3.2. Мікросхеми флеш-пам’яті

- •8.3. Використання пзп

- •8.3.1. Використання пзп як універсальних комбінаційних схем

- •8.3.2. Пзп як нелінійні функціональні перетворювачі

- •8.3.3. Перетворювачі кодів для матричних індикаторів

- •8.3.4. Використання пзп для реалізації складних способів модуляції

- •8.3.5. Використання пзп у генераторах періодичних послідовностей

- •8.3.6. Використання пзп у скінченних мікропрограмних автоматах

- •8.4. Оперативні запам’ятовуючі пристрої

- •8.4.1. Статичні озп

- •8.4.2. Динамічні озп (dram)

- •8.4.3. Використання озп

- •8.4.3.1. Використання озп як інформаційного буфера

- •Контрольні питання

- •Вправи і завдання

Розділ VIII запам’ятовуючі пристрої

У попередніх розділах уже розглядалися пристрої для тимчасового запам’ятовування невеликих обсягів інформації (тригери, регістри, регістрові файли). Але сучасні інформаційні технології вимагають оперативної роботи із значно більшими об’ємами інформації, яка може досить швидко змінюватись.

З великого обсягу різноманітних пристроїв запам’ятовування і зберігання інформації у цьому розділі розглянемо лише напівпровідникові, які широко використовуються як у мікропроцесорних системах, так і в якості самостійних виробів у різноманітних системах автоматики.

Використання напівпровідникових пристроїв пам’яті широке та різноманітне. Тому різноманітними є і типи використовуваних запам’ятовуючих пристроїв (ЗП). У літературі використовуються різні способи їх класифікації, але в цілому вони можуть розглядатись як дві великі групи – енергозалежні та енергонезалежні ЗП, тобто визначальним фактором виступає те, зберігається записана в них інформація при відключенні живлення чи ні.

8.1. Постійні запам’ятовуючі пристрої (принципи побудови, типи, характеристики)

Розглянемо спочатку енергонезалежну пам’ять, яка здебільшого в найбільш загальній формі називається ПЗП – постійні запам’ятовуючі пристрої (ROM – Read Only Memory).

8.1.1. Одновимірні пзп

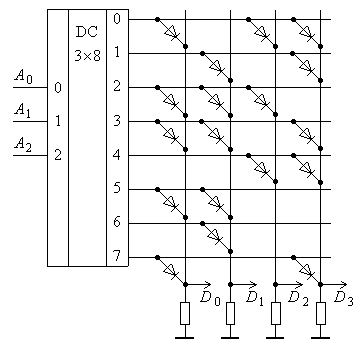

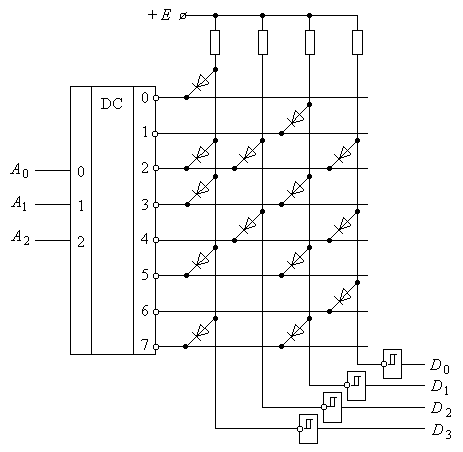

ПЗП – це пристрої пам’яті, вміст яких не може бути змінений процесором під час виконання програми і зберігається при відсутності живлення. Приклад структури ПЗП приводиться на рис. 8.1. Вона складається з дешифратора адреси A2 A1 A0 і діодної матриці. У відповідності до значень сигналів на адресних входах, один з виходів дешифратора активізується (у даному випадку – на одному з виходів 0…7 з’являється сигнал високого рівня, який через відповідні діоди передається на виходи D0 …D3 , фактично відображаючи у двійковому коді значення слова, що створене в матриці за допомогою приєднаних діодів).

Рис. 8.1

Приклад 8.1. Пояснити, який код з’явиться на виході ПЗП (рис. 8.1), якщо на його вхід подається двійковий код A2 A1 A0 = 011.

Розв’язання. Приведеному двійковому коду на адресних входах відповідає вихід дешифратора з номером 3. Високий рівень сигналу з виходу 3 буде переданий на виходи D0 , D1 і D3 . Вихід D2 матиме низький рівень вихідного сигналу, оскільки він через резистор приєднаний до загальної шини. Звідси знаходимо записане слово:

D3 D2 D1 D0 = 1011.

Виходячи з цього прикладу, можна скласти таблицю станів для кожного з виходів як функцію адресних входів. Для приведеної на рис. 8.1 схеми таблиця станів приводиться у Табл. 8.1.

Табл. 8.1

N |

Входи |

Виходи |

|||||

A2 |

A1 |

A0 |

D3 |

D2 |

D1 |

D0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

2 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

3 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

4 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

5 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

6 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

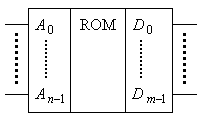

З Табл. 8.1 витікає, що ПЗП є комбінаційною схемою з n входами, які називаються адресними. Виходи комбінаційної схеми D0 …D3 є виходами даних. Іншими словами, ПЗП зберігає в матричному пристрої пам’яті таблицю станів n-входової і m-виходової комбінаційної функції. Виходячи з даних таблиці, можемо стверджувати, що в ПЗП зберігається 2n слів, кожне з яких має розмірність m = 4 розряди. Інформаційна ємність його складає 23 × 4 = 32 біти.

Нехтуючи прогнозованою затримкою, дані ПЗП визначаються бітами вихідного слова D0 …Dm , що зберігається у відповідному рядку таблиці станів, який задається адресними входами A0 …An . Умовне позначення ПЗП приводиться на рис. 8.2.

Рис. 8.2

Оскільки ПЗП є комбінаційною схемою, то буде правильним сказати, що це взагалі не пам’ять, а група комбінаційних логічних елементів. Але, у той же час, якщо у ПЗП записується інформація, то зрозуміло, що вона звідти зчитуватиметься неодноразово і зберігатиметься навіть при відсутності живлення. Це і мається на увазі, коли говорять, що ПЗП є енергонезалежною пам’яттю.

Аналізуючи стани Табл. 8.1, можемо її розглядати як таблицю чотирьох функцій трьох змінних, тобто:

![]()

Як витікає з Розділу ІІІ, така система функцій може бути реалізована на основі дешифратора 3 × 8 і чотирьох логічних елементів АБО, кількість входів кожного з яких відповідає кількості мінтермів відповідної логічної функції:

Таке представлення записаної у ПЗП інформації і забезпечує спосіб їх побудови на основі дешифраторів та багатовходових логічних елементів АБО.

З іншого боку, за кожною з адрес A2 … A0 маємо чотири біти даних, які можуть зчитуватись як окремі записані слова. Представивши їх у шістнадцятковій системі числення, Табл. 8.1 можемо зобразити в іншій формі (див. Табл. 8.2), тобто кожному значенню адреси, яка зображена у вигляді впорядкованого ряду мінтермів, відповідає конкретне значення вихідного слова, що записане в структурі пам’яті.

Табл. 8.2

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

D |

A |

7 |

B |

C |

3 |

2 |

9 |

У практиці електронної техніки Табл. 8.2 називається таблицею (картою) прошивок або гексадецимальним лістінгом.

Таблиця станів (Табл. 8.1) може мати будь-які значення двійкового коду, тому вона може розглядатися ще з однієї позиції. Позначимо, наприклад, входи A1 A0 як входи одного слова, а A2 = B0 – вхід іншого слова. Враховуючи, що у таблицю станів можна записати будь-які значення, котрі відповідають взаємодії цих двох слів, створимо таблицю, яка відповідає арифметичній дії додавання дворозрядного слова А і однорозрядного слова В. Тоді значення виходів можемо позначити як P2 , S1 , S0 , де P2 – значення переносу в третій розряд; S1 S0 – розряди суми. Отримуємо відповідну таблицю (Табл. 8.3).

Табл. 8.3

B0 |

A1 |

A0 |

P2 |

S1 |

S0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

Приклад 8.2. Використовуючи ПЗП формату 256 × 8, розробити таблицю прошивок для виконання операції перемноження двох чотирьохрозрядних слів.

Рис. 8.3

Розв’язання. На рис. 8.3 приведена схема, яка пояснює особливості використання виводів мікросхеми при побудові перемножувача.

Таблиця прошивок мікросхеми приведена у Табл. 8.4.

У ній крайній зліва стовпець (ліві знаки) відображає адресний простір старших розрядів (A4 …A7), що відображений у шістнадцятковій системі числення. Решта стовпців визначається молодшими розрядами адресного простору. На перетині відповідного стовпця та рядка у відповідній клітині записується двійкове значення добутку.

Табл. 8.4

|

00 |

01 |

02 |

03 |

04 |

05 |

06 |

07 |

08 |

09 |

0A |

0B |

0C |

0D |

0E |

0F |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

00 |

10 |

00 |

01 |

02 |

03 |

04 |

05 |

06 |

07 |

08 |

09 |

0A |

0B |

0C |

0D |

0E |

0F |

20 |

00 |

02 |

04 |

06 |

08 |

0A |

0C |

0E |

10 |

12 |

14 |

16 |

18 |

1A |

1C |

1E |

30 |

00 |

03 |

06 |

09 |

0C |

0F |

12 |

15 |

18 |

1B |

1E |

21 |

24 |

27 |

2A |

2D |

40 |

00 |

04 |

08 |

0C |

10 |

14 |

18 |

1C |

20 |

24 |

28 |

2C |

30 |

34 |

38 |

3C |

50 |

00 |

05 |

0A |

0F |

14 |

19 |

1E |

23 |

28 |

2D |

32 |

37 |

3C |

41 |

46 |

4B |

60 |

00 |

06 |

0C |

12 |

18 |

1E |

24 |

2A |

30 |

36 |

3C |

42 |

48 |

4E |

54 |

5A |

70 |

00 |

07 |

0E |

15 |

1C |

23 |

2A |

31 |

38 |

3F |

46 |

4D |

54 |

5B |

62 |

69 |

80 |

00 |

08 |

10 |

18 |

20 |

28 |

30 |

38 |

40 |

48 |

50 |

58 |

60 |

68 |

70 |

78 |

90 |

00 |

08 |

12 |

1B |

24 |

2D |

36 |

3F |

48 |

51 |

5A |

63 |

6C |

75 |

7E |

87 |

A0 |

00 |

0A |

14 |

1E |

28 |

32 |

3C |

46 |

50 |

5A |

64 |

6E |

78 |

82 |

8C |

96 |

B0 |

00 |

0B |

16 |

21 |

2C |

37 |

42 |

4D |

58 |

63 |

6E |

79 |

84 |

8F |

9A |

A5 |

C0 |

00 |

0C |

18 |

24 |

30 |

3C |

48 |

54 |

60 |

6C |

78 |

84 |

90 |

9C |

A8 |

B4 |

D0 |

00 |

0D |

1A |

27 |

34 |

41 |

4E |

5B |

68 |

75 |

82 |

8F |

9C |

A9 |

B6 |

C3 |

E0 |

00 |

0E |

1C |

2A |

38 |

46 |

54 |

62 |

70 |

7E |

8C |

9A |

A8 |

B6 |

C4 |

D2 |

F0 |

00 |

0F |

1E |

2D |

3C |

4B |

5A |

69 |

78 |

87 |

96 |

A5 |

B4 |

C3 |

D2 |

E1 |

Якщо, наприклад, задамо множник 710 = 716 , а множене 810 = 816 , то на перетині рядка 70 і стовпця 08 маємо результат 3816 = 5610 . Це означає, що з шини D0 ÷ D7 повинно бути зчитане число 3816 . Запис такого числа в пам’ять забезпечується в такій послідовності. Оскільки вибрана адреса визначається кодом 7816 = 011110002 , то це означає, що в мікросхемі пам’яті вибраний 011110002 = 12010 рядок. В цей рядок необхідно записати слово 3816 = 5610 = 001110002 .

Внутрішня структура ПЗП реально дещо відрізняється від приведеної на рис. 6.1 – перш за все, тим, що внутрішній дешифратор має інверсні виходи, а тому при активізації відповідного рядка його потенціал стає близьким до нуля (рис. 8.4). Кожен з виходів дешифратора називається рядком слова, оскільки вибирається слово з матриці діодів. Вертикальні шини через резистори приєднані до джерела живлення. Вертикальні лінії називаються бітовими стовпцями, оскільки відповідають значенню одного біта записаного слова.

Рис. 8.4

У схемі, що розглядається, з’єднання через діод відповідних лінії слова і лінії біта забезпечує запис логічної одиниці.

Наявність інверторів з тригерами Шмідта покращує рівень захисту від перешкод, оскільки падіння напруги на діоді складає приблизно 0,5…0,6 В, і падіння напруги на відкритому виході дешифратора підвищують нульовий рівень перешкод.

Мікросхеми ПЗП виготовляються також із використанням МДН-технології, де в якості елементів пам’яті використовуються транзистори з n- або p- каналами, а також комплементарні ключі. При використанні МДН-транзисторів під час виготовлення ПЗП запис логічних одиниць або нулів забезпечується за рахунок величини порогової напруги стокозатворної характеристики транзистора. Збільшення або зменшення величини порогової напруги встановлюється товщиною ізоляційного прошарку між затвором та напівпровідником. У матрицях з такими транзисторами всі транзистори, що відносяться до одного записаного слова, приєднуються затворами до вибраного рядка, а стоки кожного транзистора з’єднуються з відповідним розрядним стовпцем матриці. Витоки всіх транзисторів об’єднані і приєднуються до джерела живлення. При виборі відповідного рядка транзистори з низьким пороговим рівнем напруги відкриваються, і на відповідних стовпцях матриці отримується сигнал логічної одиниці. У транзисторах з високою порогової напругою буде записаний логічний нуль.