- •Розділ VII регістри

- •7.1. Загальне поняття про регістри

- •7.2. Регістри пам’яті

- •7.3. Конвеєрні пристрої

- •7.4. Регістри зсуву

- •7.5. Приклади мікросхем регістрів та особливості їх використання

- •7.5.1. Паралельні регістри

- •7.5.2. Регістрові файли

- •7.5.3. Послідовні регістри

- •7.6. Напрямки (області) використання регістрів

- •7.6.1. Забезпечення обміну інформацією у послідовному форматі

- •7.6.2. Регістрові лічильники імпульсів (розподілювачі)

- •7.6.3. Лічильники Джонсона

- •7.6.4. Поліноміальні пристрої кодування та фільтрації

- •7.6.5. Системи контролю цифрової апаратури

- •7.6.6. Використання регістрів для обчислення контрольної суми

- •Контрольні питання

- •Вправи і завдання

Розділ VII регістри

7.1. Загальне поняття про регістри

Регістрами називають цифрові пристрої, призначені для тимчасового зберігання та перетворення інформації, що подається на них у вигляді багаторозрядних двійкових чисел. Основою будь-якого регістра є елемент пам’яті – тригер. Кількість тригерів, розміщених паралельно або з’єднаних послідовно, визначає розрядність регістрів. Але, на відміну від лічильників, до розрядів регістрів поняття “ваговий коефіцієнт” не застосовується, оскільки кожен з них незалежний.

У регістрах використовуються RS-, D-, JK-тригери. Для забезпечення керування записом інформації у тригери та її зчитуванням використовуються комбінаційні пристрої, які закладають алгоритми керування регістрами.

Регістри можуть класифікуватися за різними ознаками, але основними є способи введення та виведення інформації. Виходячи з цього, вони розділяються на дві групи: накопичувальні (або регістри пам’яті) та послідовні (або регістри зсуву). У свою чергу, послідовні регістри можуть забезпечувати послідовний, паралельний та комбінований способи введення та виведення інформації.

Записана у тригери інформація може виводитись у прямому коді, зворотному або одночасно в прямому та зворотному.

Регістри зсуву можуть бути однонаправленими, тобто забезпечувати зсув лише в одному напрямку, або реверсивними (двонаправленими).

У мікропроцесорній техніці широко використовуються регістри, в яких вхідні та вихідні лінії даних об’єднані в одну групу (порт даних). У залежності від керуючого сигналу, такий порт може налаштовуватись на введення інформації або на її виведення.

7.2. Регістри пам’яті

Регістри пам’яті є порівняно простими структурами, призначеними для запису, тимчасового зберігання та передачі невеликих обсягів інформації, представленої у двійковому коді.

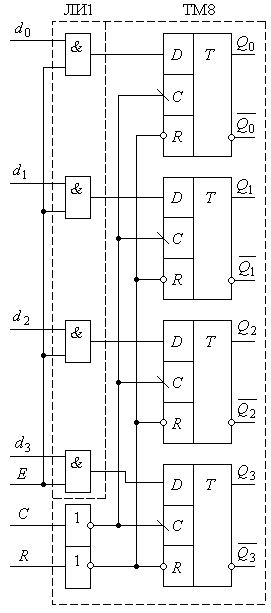

Рис. 7.1

Елементами пам’яті в них виступають здебільшого D-тригери, тому регістри подібного типу можуть виготовлятись з використанням мікросхем, що містять набори синхронних тригерів, – наприклад, мікросхеми КР1533ТМ2 (SN74ALS74A), ТМ7, ТМ8, ТМ9. Керування режимами запису / зчитування може бути забезпечено вхідною та вихідною логікою, побудованою, наприклад, з використанням ЛЕ 2І (ЛИ1 (ALS08)).

На рис. 7.1 приводиться приклад

реалізації функціональної схеми регістра

з дозволяючим входом запису Е,

прямими та інверсними виходами. Запис

інформації в D-тригери може виконуватись

при високому рівні сигналу на вході Е

за фронтом синхросигналу С. Зчитування

інформації в прямому або зворотному

кодах виконується безпосередньо з

виходів тригерів Qi та

![]() .

Для забезпечення керування процесом

зчитування може бути використана та ж

мікросхема або створений режим

мультиплексування виходів тригера на

один вихід регістра. При використанні

такого пристрою у структурах з великою

кількістю регістрів вхід Е може

використовуватись для адресного

звернення до одного з них через відповідні

дешифратори адреси.

.

Для забезпечення керування процесом

зчитування може бути використана та ж

мікросхема або створений режим

мультиплексування виходів тригера на

один вихід регістра. При використанні

такого пристрою у структурах з великою

кількістю регістрів вхід Е може

використовуватись для адресного

звернення до одного з них через відповідні

дешифратори адреси.

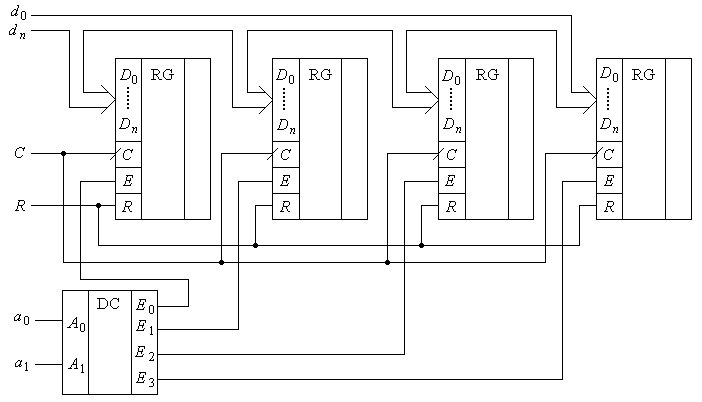

Прикладом такої структури є схема, приведена на рис. 7.2.

Рис. 7.2

За допомогою адресних сигналів a0 a1 вибирається один із регістрів, на який подається високий рівень дозволяючого сигналу. Внаслідок цього дані з шини d0…dn за фронтом синхросигналу С будуть записані у вибраний регістр. Така структура дозволяє демультиплексувати потік даних по декількох окремих шинах.

Подібним шляхом може бути розв’язана зворотна задача, коли необхідно з різних шин подавати інформацію на одну – режим мультиплексування потоків даних, їх ущільнення. Читачам пропонується самостійно розробити таку схему.

Реальним прикладом є мікросхема ИР5. Це чотирьохрозрядний паралельний регістр даних, умовне зображення якого приведене на рис. 7.3.

|

|

Він має по два входи DiA та DiB для одного запам’ятовуючого елемента. Вибір входу забезпечується рівнем сигналу, що подається на вхід S, а запис – за зрізом синхросигналу. Враховуючи наявність логіки на входах та виходах тригерів, режими роботи регістрів описуються таблицями станів. Приклад таблиці станів для регістра ИР5 приводиться у Табл. 7.1. Таблиці станів повинні відображати всі режими роботи регістра, і для кожного з них вказують на однозначну відповідність між рівнями логічних сигналів на його вході та виході.

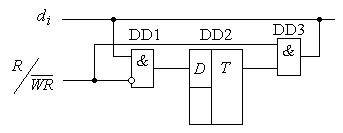

Для забезпечення запису та зчитування інформації по одній шині даних може бути запропонована схема, приведена на рис. 7.4 для одного розряду.

При високому рівні сигналу на вході

![]() інформація з виходу D-тригера

(мікросхема DD2) зчитується через елемент

DD3 на шину даних di . При

низькому рівні сигналу

інформація з шини даних записуватиметься

в тригери регістра.

інформація з виходу D-тригера

(мікросхема DD2) зчитується через елемент

DD3 на шину даних di . При

низькому рівні сигналу

інформація з шини даних записуватиметься

в тригери регістра.

Рис. 7.4

Звичайно, це досить спрощена структура портів вводу / виводу інформації у паралельному форматі. Реальні порти значно складніші апаратно і вимагають відповідної ініціалізації. Але подібна схемотехніка використовується у багаторегістрових структурах для забезпечення міжрегістрових пересилок.

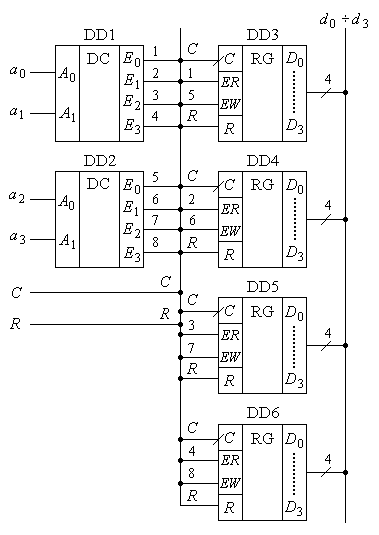

На рис. 7.5 приводиться функціональна схема, що містить чотири регістри, які об’єднані єдиною шиною даних (d0…d3). Дешифратори DD1 і DD2 на основі адресних сигналів (a0…a3) генерують сигнали дозволу на читання інформації з регістра ER та запису EW. При виборі двох регістрів по їх адресах на відповідних входах ER і EW встановлюються сигнали високого рівня, що дозволяє за фронтом синхросигналу С зчитати інформацію з одного регістра та записати в інший.

Рис. 7.5

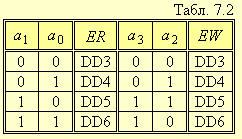

Приклад 7.1. Сформувати код двійкової команди для перезапису інформації з регістра DD4 в регістр DD6.

Р озв’язання.

Створимо таблицю адресації до регістрів

при зчитуванні та записі (Табл. 7.2).

озв’язання.

Створимо таблицю адресації до регістрів

при зчитуванні та записі (Табл. 7.2).

Зрозуміло, що для перезапису інформації з регістра DD4 у регістр DD6 її необхідно спочатку зчитати з регістра DD4, а потім записати в регістр DD6. Виходячи з даних таблиці, двійковий код команди матиме вигляд:

EW ∙ ER = a3 a2 a1 a0 = 1001.

Міжрегістрові пересилки досить широко використовуються у мікропроцесорній техніці.

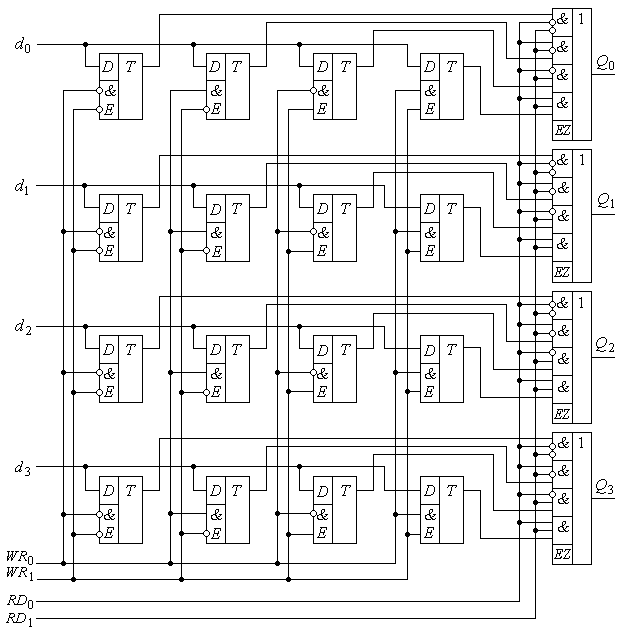

Своєрідними запам’ятовуючими пристроями є регістрові файли. Вони призначені для зберігання декількох слів, причому процеси запису одного слова та зчитування іншого відбуваються одночасно і незалежно.

На рис. 7.6 приводиться функціональна схема регістрового файлу на чотири чотирьохрозрядні слова. Файл побудований у вигляді матриці 4 × 4, де кожен стовпець тригерів призначений для запам’ятовування одного слова, а кожен рядок – відповідно, розряди кожного з слів.

Рис. 7.6

Запис у будь-який стовпець забезпечується набором адреси стовпця на входах WR1 WR0 . При цьому на кожному з тригерів стовпця з’явиться сигнал дозволу запису Е, за яким в асинхронному режимі слово з шини даних d0…d3 запишеться у тригери стовпця.

Зчитування інформації забезпечується незалежно за допомогою ЛЕ 4(3І-АБО). Вибір будь-якого стовпця забезпечується вхідною логікою елементів 3І, оскільки два входи кожного з них – адресні і приєднані до входів RD1 RD0 , які задають адресу слова, що зчитується.

Виходи регістрового файлу мають Z-стан, що дає можливість з’єднувати їх в одній точці. Для мікросхем КР1533 допускається з’єднання до 128 виходів, що дозволяє створювати запам’ятовуючі пристрої до 512 слів. Збільшення ємності такої пам’яті можливе з використанням допоміжних елементів. Регістрові файли дозволяють також збільшувати розмір слова до 8, 12, 16 розрядів шляхом паралельного з’єднання входів дозволу.

Регістрові файли часто використовуються для створення швидкодіючих запам’ятовуючих пристроїв малої ємності.

Окрім адресованих регістрів загального призначення, у цифровій апаратурі використовуються допоміжні запам’ятовуючі пристрої з “неявно” вираженою адресацією, які служать для зберігання черг і називаються іноді “буферами даних”. Ці пристрої часто будують на основі регістрової пам’яті.

Необхідність у такому буфері виникає тоді, коли джерело даних постачає приймачу слова, що розподілені у часі нерівномірно, причому інтервали часу між двома словами можуть іноді бути меншими, ніж час, необхідний приймачу для обробки одного слова. Подібна ситуація може приводити до того, що частина даних втрачатиметься. Якщо такі втрати недопустимі, то між джерелом та приймачем включається буфер “черги” для створення і зберігання черги слів для їх послідуючої обробки, або буфер типу FIFO (First In - First Out – перший ввійшов - перший вийшов).

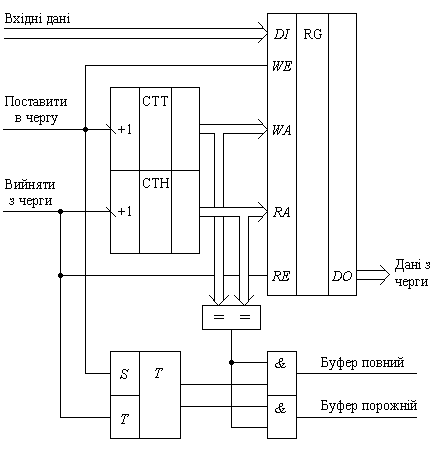

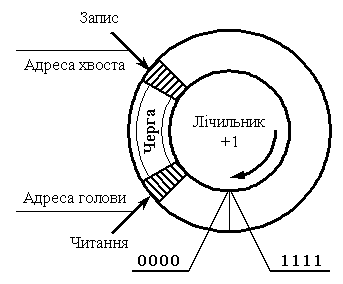

а |

б |

Рис. 7.7 |

Функціональна схема буфера, побудованого на основі регістрової пам’яті, зображена на рис. 7.7, а. На рис. 7.7, б набір регістрів пам’яті, тобто адреси регістрів пам’яті, зображені у вигляді кільця. Частина регістрів заповнена словами черги – решта вільні. Адреса запису при постановці в чергу задається лічильником хвоста черги (СТТ). Сигнал “Поставити в чергу” подається на вхід WE дозволу запису і забезпечує запис слова даних, що поступили по вхідній шини DI (Data In) у той регістр пам’яті, номер якого зберігається в СТТ. За зрізом сигналу “Поставити в чергу” вихідний код СТТ збільшується на 1, підготовляючи адресу запису для чергового слова. При появі сигналу “Вийняти з черги” на вихідній шині DO (Data Out) з’явиться слово, яке зберігалося в тому регістрі пам’яті, номер якого задається кодом лічильника голови СТН. За зрізом сигналу вихідний код лічильника збільшується на 1, підготовлюючи тим самим до видачі наступне слово, яке стало першим у черзі. Переповнення лічильника СТТ не призводить до ускладнення ситуації, оскільки після максимально можливого коду 1111…11 у ньому автоматично з’явиться код 0000…00. Черга в кільці просто переміститься хвостом через нульову відмітку лічильника. Так само з часом матиме місце переміщення голови. В процесі нормальної роботи черга рухатиметься по кільцю значень адрес за часовою стрілкою хвостом вперед, зростаючи чи скорочуючись у відповідності до швидкості передавача. Схема буфера FIFO повинна сигналізувати про появу двох особливих ситуацій. Перша – “буфер повний”. Це означає, що в нього неможливо більше записувати і необхідно зупинити передачу даних. Друга – “буфер порожній”. Це означає, що з нього неможливо брати дані і необхідно зупинити приймач. Обидві ситуації мають спільну ознаку: рівність кодів обох лічильників після зникнення вхідного сигналу. Така ознака виявляється компаратором. Якщо коди лічильників стали рівними після чергової вибірки з черги, то це означає, що черги немає і буфер порожній. Якщо ж коди лічильників стали рівними після чергового запису в чергу, то буфер повний. Характер останнього звернення до буфера запам’ятовується в RS-тригері, який при появі особливих ситуацій через елементи 2І видає відповідні інформаційні сигнали, призначені для подальшого прийняття рішень.

Іншим широко використовуваним буфером є буфер типу “магазин”, або “стек” (Stack), або буфер типу LIFO (Last In - First Out – останній ввійшов - перший вийшов).

Стекові структури даних використовуються у цифрових пристроях, в яких процес виконання завдання переривається більш терміновим, тому всі дані, що були пов’язані з перерваним завданням, розміщуються у буфері типу “магазин” для тимчасового зберігання. Виконання термінового завдання також може бути перервано появою більш термінового, і т. д. Внаслідок таких переривань у буфері накопичуватимуться нові й нові дані, створюючи чергу слів, очікуючих обробки. Вибірка з буфера слів відбувається у відповідності до вимог їх черговості, внаслідок чого першими виймаються слова, які були занесені в буфер останніми.

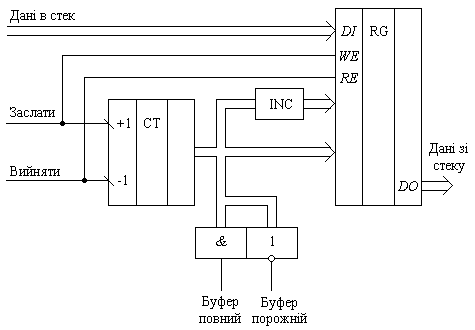

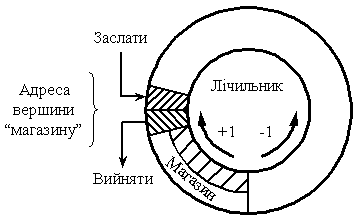

а |

б |

Рис. 7.8 |

На рис. 7.8, а приведена функціональна схема буфера типу “магазин”. Основою його є регістрова пам’ять, а також реверсивний лічильник адреси, в якому зберігається номер регістра вершини стеку (рис. 7.8, б). Коли подається команда “Заслати у стек” (Push), то вміст лічильника інкрементується на 1; при команді “Вийняти зі стеку” (Pop) його вміст декрементується. Як видно з діаграми, адреса, за якою засилається слово у стек, завжди на 1 більше адреси, за якою слово зчитується зі стеку. Постійну різницю на 1 між адресами запису та зчитування підтримує пристрій, який називається інкременатором (INC). Два особливі стани – “буфер повний” та “буфер порожній” – визначаються за максимально можливим і нульовим значенням вмісту лічильника.

Інші варіанти побудови стеку будуть розглянуті пізніше.