- •10.1.1. Пристрої часових перетворень на основі логічних елементів

- •10.1.2. Використання зовнішніх rc-ланок

- •10.1.3. Пристрої перетворення форми імпульсів

- •10.2. Одновібратори

- •10.2.1. Одновібратори на основі логічних елементів

- •10.2.2. Одновібратори на спеціалізованих мікросхемах

- •10.2.3. Одновібратори на основі таймера кр1006ви1

- •10.2.4. Одновібратори на основі тригерів

- •10.3. Генератори прямокутних імпульсів

- •10.3.1. Мультивібратор на основі логічних елементів

- •10.3.2. Мультивібратори на основі тригерів

- •10.3.3. Мультивібратори на основі мікросхем одновібраторів

- •10.3.4. Мультивібратори на основі таймера кр1006ви1

- •10.3.5. Кварцові генератори

- •10.4. Універсальні генераторні мікросхеми

- •10.4.1. Мікросхема к1108пп1

- •10.4.2. Генератор з системою фапч к564гг1

- •Контрольні питання

- •Вправи і завдання

Розділ X

ІМПУЛЬСНІ ПРИСТРОЇ

НА БАЗІ ЦИФРОВИХ ІНТЕГРАЛЬНИХ СХЕМ

10.1. Пристрої формування імпульсів

Під терміном “формування імпульсів” мається на увазі перетворення аналогових або цифрових сигналів з метою отримання їх часових характеристик відповідно до поставлених вимог.

Оскільки основними часовими параметрами імпульсів, що описані в Розділі ІІ, є тривалості фронту та зрізу, тривалості імпульсу та паузи, то в цілому пристрої формування імпульсів розв’язують такі задачі:

формування меандру з синусоїдального або іншого типу аналогового сигналу;

формування імпульсів з короткими фронтами та зрізами (спадами);

скорочення та розширення тривалості імпульсів;

організація часової затримки імпульсів;

формування короткочасних імпульсів з тривалістю фронту (спаду) імпульсу.

Затримки цифрових сигналів вимагаються перш за все для часового узгодження в розповсюдженні сигналів по різних шляхах в цифровому пристрої з метою боротьби з критичними змаганнями, які порушують працездатність пристроїв (наприклад, автоматів з пам’яттю).

Часові перетворення імпульсів можуть виконуватись як з використанням лише логічних елементів, так і з використанням інтегруючих та диференціюючих RC-ланок.

10.1.1. Пристрої часових перетворень на основі логічних елементів

У цьому випадку часові перетворення забезпечуються за рахунок внутрішніх затримок логічних елементів. Оскільки ці затримки для сучасної елементної бази визначаються одиницями-десятками наносекунд, то такі пристрої забезпечують формування досить коротких імпульсів, які можуть бути зафіксовані далеко не кожним осцилографом.

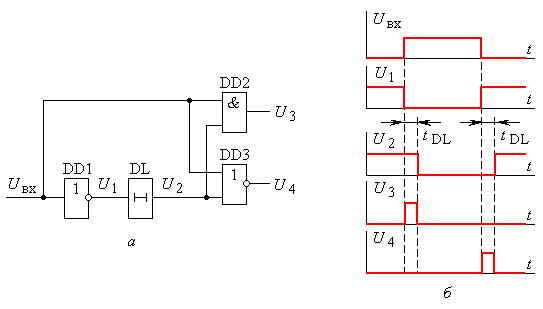

На рис. 10.1, а приведена узагальнена схема пристрою, за допомогою якої можна пояснити різні можливості формування імпульсів та організації їх затримок. Часові діаграми, що пояснюють роботу пристрою, приведені на рис. 10.1, б.

Рис. 10.1

Вхідний сигнал Uвх інвертується інвертором DD1 і подається на вхід пристрою затримки DL. В якості елемента затримки може використовуватись будь-яка парна кількість типових логічних елементів, кожен з яких має час затримки tЗ , тобто:

![]() ,

,

де k – кількість пар логічних елементів.

Оскільки елемент Ι забезпечує формування вихідного імпульсу при співпаданні високих рівнів вхідних сигналів, то він фіксує інтервал часу затримки за фронтом вхідного імпульсу. Елемент АБО-HI фіксує співпадання низьких рівнів вхідних сигналів, тобто інтервал часу затримки за спадом вхідного сигналу. В обох випадках отримання вихідного імпульсу базується на співпаданні вхідного сигналу і сигналу з виходу лінії затримки.

Слід пам’ятати, що величина часу затримки для кожної з серій мікросхем має свої значення, які приводяться у довідковій літературі, і вони мають значний розкид, а тому точність затримки низька. Для мікросхем КМОН, які можуть працювати в широкому діапазоні напруг живлення, величина tЗ змінюється залежно від напруги живлення, причому чим менша напруга, тим більша величина затримки. Така властивість КMOH IC іноді використовується для зміни величини tЗ або зменшення кількості логічних елементів, що використовуються в лініях затримки.

Подібним шляхом можна збільшувати тривалості імпульсів, використовуючи схему (рис. 10.2) без інвертора.

Рис. 10.2

Враховуючи той факт, що розкиди фронтів, спадів та інтервалів часу затримок досить значні, очікувати високої точності формування імпульсів не слід.

10.1.2. Використання зовнішніх rc-ланок

Зовнішні RC-ланки можуть мати постійні часу, величини яких на декілька порядків перевищують внутрішні затримки логічних елементів. Інтегруючі ланки, встановлені між логічними елементами, можуть задавати часові затримки значних розмірів, суттєво змінювати тривалості імпульсів, а також створювати принципово нові пристрої. Диференціюючі ланки, встановлені між ЛЕ, дають можливість створювати короткі імпульси.

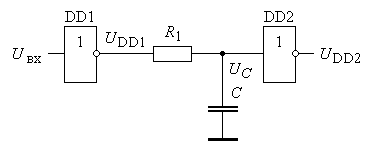

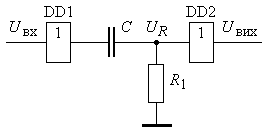

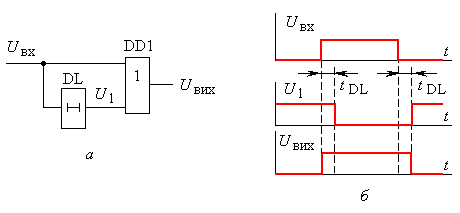

Використання інтегруючих RC-ланок. Прикладом використання інтегруючої ланки є пристрій, схема якого приведена на рис. 10.3.

|

|

Рис. 10.3 |

Рис. 10.4 |

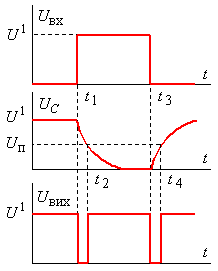

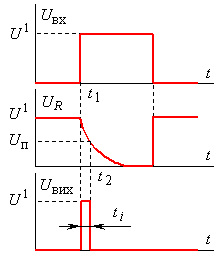

Робота пристрою основана на використанні часової зміни напруги на конденсаторі при його заряді або розряді і фіксації конкретних значень напруги UC за допомогою порогових пристроїв. Тому ЛЕ DD2 використовується як пороговий пристрій, напруга перемикання якого UП і є тією пороговою величиною, яка змінює його стан.

Якщо виходити з умови ідеальності ЛЕ DD1 і DD2, тобто вихідний опір DD1 при UDD1 = U1 дорівнює нулю, вхідний опір DD2 сягає до нескінченності, а внутрішня затримка на перемикання обох елементів tЗ = 0, то робота пристрою може бути зрозумілою з часових діаграм, приведених на рис. 10.4.

При високому рівні вхідного сигналу Uвх на виході DD1 маємо напругу низького рівня, і конденсатор С розряджений. При зміні вхідного сигналу з одиничного до нульового рівня в момент часу t1 на його виході виникне напруга високого рівня U1. Тому з моменту t1 почнеться процес зарядження конденсатора з постійною часу τRC = R1 C.

У момент часу t2 , коли напруга на конденсаторі UC досягне рівня порогової напруги UП , він змінить свій стан, і на його виході рівень U1 зміниться на нульовий.

До моменту часу t3 конденсатор С повністю зарядиться, а з моменту t3 зміни стану виходу DD1 він почне розряджатися з тією ж постійною часу, поки не досягне порогового рівня.

Величина затримки

tЗ = t2 – t1 = t4 – t3

при вказаних вище умовах розраховується за відомою формулою:

|

(10.1) |

При використанні КMOH IC описані умови роботи пристрою майже повністю співпадають при умові, що внутрішні опори каналів транзисторів DD1 у відкритому стані набагато менші величини опору резистора R1 . Оскільки напруга нульового рівня на виході КМОН досить незначна U0 ≈ 0, UП = 0,5 U1, то для практичних розрахунків справедливою буде формула:

|

(10.2) |

При використанні ТТЛ IС реальні умови роботи пристрою суттєво змінюються, оскільки технічні характеристики мікросхем цих серій далекі від ідеальних. Перш за все, через вхід мікросхеми DD2 при UC < UП протікатиме струм I0вх , який задається базовим опором RБ багатоемітерного транзистора (рис. 10.5). Цей струм допоміжно заряджатиме конденсатор С.

Рис. 10.5

Оскільки вхід ЛЕ DD2 (рис. 10.3) перебуватиме під дією напруги конденсатора, що змінюється, то величина його вхідного струму також змінюватиметься.

З моменту часу, коли UC > UП , емітерний перехід багатоемітерного транзистора ЛЕ DD2 зміститься в зворотному напрямку, а конденсатор продовжуватиме заряджатись за рахунок струму через R1 .

При зміні стану виходу ЛЕ DD1 конденсатор С розряджатиметься з постійною часу R1 C в інтервалі часу t3 ÷ t4 . Як тільки напруга UC зменшиться до порогового рівня, то між обома логічними елементами утвориться електричне коло від напруги живлення DD2 через базовий резистор багатоемітерного транзистора, перехід база – емітер, резистор R1 та відкритий нижній транзистор ЛЕ DD1. Наявність такого кола призведе до того, що напруга на конденсаторі не зменшиться до нуля, а тримається на рівні

![]() .

.

Схема буде працездатною, якщо виконуватиметься умова:

UC < UП ,

з якої знаходиться обмеження на вибір резистора R1 [Зельд.]:

|

(10.3) |

З метою забезпечення стійкої роботи пристрою і через необхідність врахування розкидів порогових рівнів величину R1 вибирають приблизно на порядок меншою, ніж розрахована за формулою (10.3). Ємність конденсатора С не повинна перевищувати 2000 пФ [Зельд.].

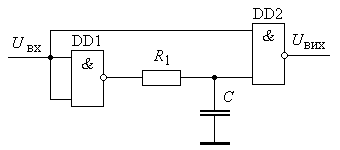

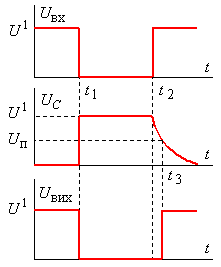

У практичній схемотехніці інтегруюча ланка знаходить досить широке використання. На рис. 10.6 приводиться схема пристрою, призначеного для скорочення тривалості імпульсу. Його роботу пояснюють часові діаграми, приведені на рис. 10.7.

|

|

Рис. 10.6 |

Рис. 10.7 |

При відсутності вхідного імпульсу (Uвх = 0) на виході DD1 маємо високий рівень напруги, і конденсатор знаходиться в зарядженому стані. На входах DD2 маємо різні рівні сигналів, внаслідок чого на його виході забезпечується також високий рівень напруги (Uвих = U1). Після появи вхідного імпульсу в момент t1 протягом часового інтервалу t1 ÷ t2 на входах DD2 діятимуть високі рівні сигналів, що забезпечить Uвих = U0 ≈ 0. Як тільки в момент часу t2 виконується умова:

![]() ,

,

на входах DD2 знову будуть сигнали різного рівня, а на виході матимемо високий рівень (Uвих = U1).

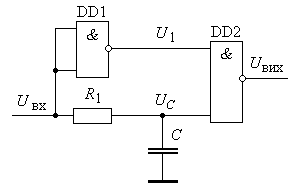

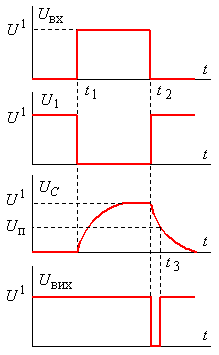

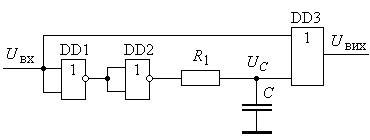

Приклад 10.1. Побудувати часові діаграми і пояснити роботу пристрою, схема якого приведена на рис. 10.8.

Рис. 10.8 |

Рис. 10.9 |

Розв’язання. Зобразимо вхідний імпульс у вигляді сигналу U1 в інтервалі t1…t2 . Тоді на виході DD1 матимемо інвертований сигнал в тому ж часовому інтервалі. Будуємо часову діаграму зміни напруги UC на конденсаторі С. З моменту t1 конденсатор заряджається від джерела вхідного сигналу, а з моменту t2 він розряджається до нуля через джерело вхідного сигналу, переходячи кожного разу через пороговий рівень UП (рис. 10.9).

Отримавши часові діаграми сигналів на обох входах ЛЕ DD2, далі аналізуємо його роботу. Логічна одиниця на виході DD2 буде в будь-який інтервал часу, в якому вхідні сигнали різні, а логічний нуль – лише в тому випадку, коли обидва сигнали мають високий рівень. Внаслідок такого аналізу находимо, що в інтервалі часу t2…t3 на його виході буде низький рівень сигналу, який забезпечує інвертовану затримку за спадом імпульсу.

З приведеного прикладу витікає важлива особливість використання RC-ланок для створення часових затримок. Вона полягає в тому, що розряд конденсатора відбувається через джерело вхідного сигналу, величина вихідного опору якого буде суттєво впливати на час розряду і, відповідно, на величину затримки.

Приклад 10.2. Вважаючи в попередньому прикладі, що використовуються КMOH IC, обчислити параметри R і C для забезпечення часової затримки tЗ = 10–3 с.

Розв’язання. Для КMOH IC є справедливою формула (10.2), з якої знаходимо:

![]() .

.

Задавши величину опору R = 10 кОм, знаходимо:

![]()

Приклад 10.3. Запропонувати схему пристрою розширювача імпульсів. Пристрій повинен розширювати імпульси тривалістю 2 мкс до 3 мкс за спадом.

Розв’язання. Оскільки пристрій повинен розширювати імпульси за спадом, то на виході необхідно мати ЛЕ, що реалізує функцію АБО, який би об’єднував вхідний імпульс та імпульс з інтегруючої ланки.

Схема пристрою приводиться на рис. 10.10.

Рис. 10.10

Розрахунок параметрів інтегруючої ланки виконується аналогічно попередньому прикладу.

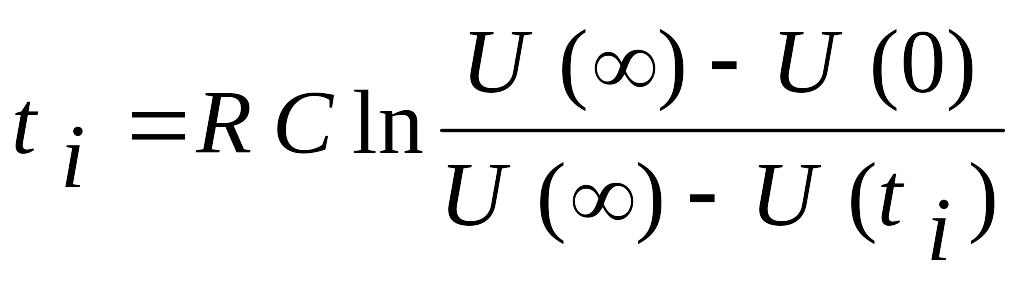

При визначенні параметрів RC-ланок здебільшого виходять з умови експоненціального характеру процесу заряду-розряду конденсатора. Тривалість будь-якого інтервалу t такого процесу може бути визначена з використанням формули:

,

,

де

![]() – розмах експоненти;

– розмах експоненти;

![]() – частина експоненти, що залишається

після інтервалу часу ti .

– частина експоненти, що залишається

після інтервалу часу ti .

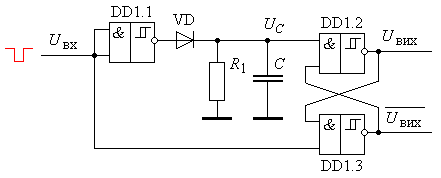

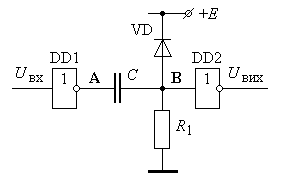

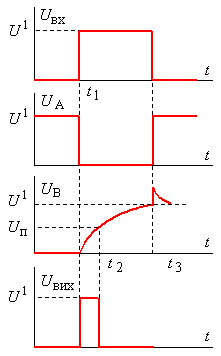

Інший варіант розширювача імпульсу за заднім фронтом реалізується з використанням елемента 2I (рис. 10.11).

|

|

а |

б |

Рис. 10.11

При відсутності вхідного імпульсу вихідний сигнал UDD1 ЛЕ DD1 має високий рівень. Внаслідок цього струм від джерела +Е через коло R, VD і вихід DD1 не протікає. Конденсатор заряджений, і напруга UC на ньому відповідає напрузі високого рівня U1. Внаслідок цього на вході DD2 діють два сигнали високого рівня, а на його виході маємо U0. При появі вхідного імпульсу напруга на виході DD1 приймає значення, близьке до нуля, і конденсатор С через діод VD миттєво розряджається. Напруга UC стає близькою до нуля, і стан DD2 змінюється на протилежний. В інтервалі часу t1…t2 дії вхідного імпульсу ЛЕ DD2 підтримується у такому ж стані.

У момент t2 рівень вхідного сигналу змінюється до нуля UDD1 = U1. Внаслідок цього починає заряджатись конденсатор С з постійною часу R1 C.

У момент t3 напруга на ньому досягає порогової величини UC = UП = U1, і стан ЛЕ DD2 змінюється на протилежний.

Величина затримки тривалості імпульсу обчислюється за формулою:

|

(10.4) |

де UVD – падіння напруги на діоді у відкритому стані.

У розглянутому розширювачі використовуються КМОН IC. В якості DD2 може використовуватись тригер Шмідта.

Більш точна фіксація порогових рівнів забезпечується при використанні в якості елементів DD1 і DD2 тригерів Шмідта.

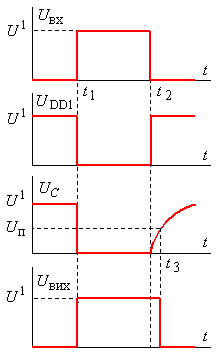

Ще більше підвищення точності роботи може бути досягнуто, коли в якості DD2 використовується регенеративні порогові схеми – наприклад, RS-тригер (рис. 10.12). У цій схемі в якості порового елемента використовується RS-тригер на основі тригерів Шмідта (наприклад, мікросхема КР1533ТЛ3).

|

Рис. 10.12 |

Часові діаграми, що пояснюють роботу пристрою, зображені на рис. 10.13.

При відсутності вхідного імпульсу низького рівня на виході DD1.1 маємо низький рівень напруги, і конденсатор С розряджений, оскільки він запаралелений опором R1. Відомо (див. Розділ IV), що при такій комбінації сигналів на вході RS-тригера на виходах його маємо:

![]() ;

;

![]() .

.

|

Рис. 10.13 |

Поява

вхідного імпульсу низького рівня в

момент t1

(рис. 10.13, б),

який одночасно подається на вхід DD1.1 і

на вхід DD1.3, приводить до зміни стану

RS-тригера:

напруга на виходах стає

![]() ,

а

,

а

![]() .

Конденсатор С

зарядиться завдяки високому рівню

напруги на виході DD1.1.

.

Конденсатор С

зарядиться завдяки високому рівню

напруги на виході DD1.1.

У

момент часу t2

вхідний імпульс низького рівня зникне,

але напруга на конденсаторі в інтервалі

часу t2…t3

підтримуватиметься на рівні вище

порогового, тобто

![]() ,

тому на обох входах DD1.2 буде високий

рівень сигналу і стан RS-тригера

не змінюватиметься. Але в момент часу

,

тому на обох входах DD1.2 буде високий

рівень сигналу і стан RS-тригера

не змінюватиметься. Але в момент часу

![]() ,

коли стане

,

коли стане

![]() ,

тригер змінить свій стан на попередній,

і на його прямому виході установиться

знову високий рівень напруги. Величина

часової затримки tЗ = t3 – t2

обчислюється аналогічно попередній

схемі.

,

тригер змінить свій стан на попередній,

і на його прямому виході установиться

знову високий рівень напруги. Величина

часової затримки tЗ = t3 – t2

обчислюється аналогічно попередній

схемі.

Використання диференціюючих RC-ланок. Головна особливість диференціюючих ланок полягає в тому, що при дії однополярного позитивного імпульсу на їх виході створюються два різнополярні імпульси, причому негативний може пошкодити вхідні кола наступної мікросхеми. Тому при використанні мікросхем, в яких відсутні вхідні антидзвонові діоди, паралельно резисторові необхідно передбачити включення в зворотному напрямку діода.

При використанні КMOH IC робота ланки мало чим відрізняється від вище описаних схем з інтегруючими ланками.

На рис. 10.14 приводиться схема пристрою, призначеного для скорочення тривалості імпульсу, а на рис. 10.15 – часові діаграми, пояснюючі його роботу. Приймемо мікросхеми DD1 і DD2 як ключові повторювачі, в якості який можуть використовуватись ЛЕ 2І, 2АБО.

|

|

Рис. 10.14 |

Рис. 10.15 |

При появі високого рівня напруги U1 на виході DD1 і розрядженому конденсаторі С через елементи С і R починає протікати струм, який в момент t1 обмежується лише опором R1 . Вся напруга імпульсу прикладається до резистора. З часом конденсатор заряджається, і струм, що протікає через елементи, зменшується відповідно до експоненціального закону. В інтервалі часу t1 ÷ t2 напруга UR перевищує пороговий рівень UП , тому вихідний стан відповідає рівню U1. В момент t2 нерівність UR > UП порушується, і сигнал на виході приймає рівень UП .

Для пристроїв, в яких використовуються ЛЕ КМОН:

.

.

При використанні ТТЛ ІС з диференціюючими ланками існують деякі особливості. Вони полягають в тому, що при високому рівні сигналу на виході DD1 величина струму через елементи R і С ланки обмежується не лише опором R1 , а й опором R4 вихідного каскаду ТТЛ ІС, що розміщений у колекторному колі верхнього транзистора (див. Розділ ІІ). У такому випадку максимальна величина падіння напруги на R1 обмежується значенням:

|

(10.5) |

де R4 – колекторний опір виходу ЛЕ DD1. Виходячи з (10.5), бажано, щоб виконувалася нерівність:

R1 >> R4 .

При низькому рівні напруги на виході DD1 через R1 протікає вхідний струм мікросхеми DD2 і створює падіння напруги

![]() .

.

При цьому можливі два режими роботи.

При малій величині опору R1 падіння напруги на ньому:

![]() .

.

Тому на виході DD2 маємо також низький рівень напруги. В цьому випадку при появі вхідного імпульсу інтервал затримки:

.

.

Якщо

ж величину опору R1

вибрати великою, то падіння напруги на

ньому

![]() ,

а на виході незмінно утримуватиметься

високий рівень

.

Тому величина опору R1

має верхню межу, яка залежить від величини

вхідного струму ТТЛ ІС. Як приклад, для

ІС серії КР1533 величина вхідного струму

низького рівня

,

а на виході незмінно утримуватиметься

високий рівень

.

Тому величина опору R1

має верхню межу, яка залежить від величини

вхідного струму ТТЛ ІС. Як приклад, для

ІС серії КР1533 величина вхідного струму

низького рівня

![]() ,

а порогова напруга високого рівня 2 В.

Тому

,

а порогова напруга високого рівня 2 В.

Тому

![]() .

.

Як висновок проведеного аналізу, можемо стверджувати:

скорочення тривалості імпульсу високого рівня досягається використанням диференціюючої ланки з невисоким значенням активного опору;

величина опору диференціюючої ланки залежить від типу використовуваних ТТЛ мікросхем і їх порогу перемикання;

тривалість скороченого імпульсу характеризується невисокою точністю, оскільки невисока напруга порогового рівня співпадає з пологою областю напруги заряду конденсатора.

Розглянемо тепер приклад роботи пристрою з інвертуючими ЛЕ (рис. 10.16, а), часові діаграми якої приведені на рис. 10.16, б.

|

|

а |

б |

Рис. 10.16

Особливість

роботи RС-ланки

полягає в тому, що при відсутності

вхідного імпульсу напруга на виході

DD1 (точка А)

має високий рівень. В той же час, при

значній величині опору

![]() вхідний струм ЛЕ DD2 створюватиме на

ньому падіння напруги:

вхідний струм ЛЕ DD2 створюватиме на

ньому падіння напруги:

|

(10.6) |

внаслідок

чого в точці В

також підтримуватиметься висока напруга

і конденсатор перебуватиме в розрядженому

стані. При появі в момент

![]() вхідного імпульсу напруга в точці А

стає близькою до нуля, і при розрядженому

конденсаторі напруга в точці В

також матиме низький рівень. Внаслідок

цього на виході DD2 виникає імпульс

високого рівня.

вхідного імпульсу напруга в точці А

стає близькою до нуля, і при розрядженому

конденсаторі напруга в точці В

також матиме низький рівень. Внаслідок

цього на виході DD2 виникає імпульс

високого рівня.

З

моменту

конденсатор С

починає заряджатись через вхід DD2 і при

досягнення порогової напруги низького

рівня (момент

![]() )

ЛЕ DD2 змінює свій стан на попередній.

)

ЛЕ DD2 змінює свій стан на попередній.

В результаті маємо наступні особливості роботи пристрою:

скорочення тривалості імпульсу досягається при порівняно високому значені опору диференціюючої ланки;

точність визначення заданої тривалості імпульсу досить низька по причинах, аналогічних попередній схемі;

підвищення точності пристроїв, призначених для скорочення тривалості вхідних імпульсів, може бути досягнуто шляхом використання в якості порогових елементів тригерів Шмідта та інших регенеративних схем.