- •Основные термины и определения

- •Введение (типы микропроцессорных систем)

- •1. Организация микропроцессорных систем

- •1.2 Архитектура микропроцессорных систем с 3-мя шинами.

- •1.3.1 Шины микропроцессорной системы

- •2.2 Адресация операндов

- •2.3 Методы адресации

- •2.4 Система команд процессора

- •2.4.1. Команды пересылки данных

- •3.4.2. Арифметические команды

- •2.4.3. Логические команды

- •2.4.4. Команды переходов

- •3.1 Функции микропроцессора.

- •3.2.1. Назначение выводов микропроцессора

- •3.2.2. Сегментирование памяти

- •3.2.3. Адресация байтов и слов

- •3.2.4. Регистры процессора

- •3.4. Быстродействие микропроцессора

- •5. Подсистема ввода-вывода мпс

- •5.1. Функции устройств ввода-вывода

- •5.2 Организация интерфейса ввода-вывода мпс. Интерфейсные бис.

- •5.2.1. Способы организации передачи информации между устройствами мпс.

- •Синхронный обмен данными

- •5.2.3 Многорежимный буферный регистр к589ир12 (i8212)

- •5.2.4 Программируемый параллельный интерфейс (ппи) - кр580вв55а.

- •5.3 Подсистема аналогового ввода-вывода.

- •Типовая схема ввода в мпс аналогового сигнала

- •6. Организация микроконтроллеров

- •6.1. Классификация и структура микроконтроллеров

- •6.2. Процессорное ядро микроконтроллера

- •6.2.1. Структура процессорного ядра мк

- •6.2.2. Система команд процессора мк

- •6.3. Память программ и данных мк

- •6.3.1. Память программ

- •6.3.2. Память данных

- •6.3.3. Регистры мк

- •6.3.4. Стек мк

- •6.3.5. Внешняя память

- •6.4 Однокристальные микроЭвм семейства мк51 (mcs-51)

5.2.3 Многорежимный буферный регистр к589ир12 (i8212)

Многорежимный буферный регистр (МБР) является 8-разрядным устройством с выходными вентилями, имеющими три устойчивых состояния, и логикой для управления и выборки кристалла. В состав МБР входит также триггер прерываний, предназначенный для выработки сигнала запроса прерывания в МП. Выборка кристалла производится при нулевом сигнале на входе ВК1 и единичном на входе ВК2. Вход ВР (выбор режима) задает режим работы схемы.

Режим ввода: ВР=0.

Прием информации производится по единичному стробу на входе С, а выдача информации – при выборке МБР по входам ВК1 и ВК2 (в противном случае выходы схемы находятся в состоянии высокого сопротивления). Сигнал на входе С осуществляет сброс триггера прерываний и формирует сигнал «запрос на прерывание» (ЗПР).

Режим вывода: ВР=1.

Выходные вентили открыты. Прием информации осуществляется при выборке данного МБР по входам ВК1 и ВК2.

При организации МП-системы МБР может использоваться в качестве буферного регистра с повышенной нагрузочной способностью по току и ёмкости нагрузки, порта ввода и порта вывода, драйвера двунаправленной шины.

При коммутации входов С, ВР и R, указанной на рис.5.2,а, обеспечивается режим работы, в котором происходит постоянная запись в МБР информации со входной шины. Выдача информации осуществляется при выборе кристалла. Применение МБР в качестве буфера значительно увеличивает нагрузочную способность шины данных.

МБР

может использоваться в качестве

интерфейсного устройства ввода (порта

ввода), если осуществить подключение

его выводов, как показано на рис.5.2,б.

МБР

может использоваться в качестве

интерфейсного устройства ввода (порта

ввода), если осуществить подключение

его выводов, как показано на рис.5.2,б.

Устройство ввода взаимодействует с МП в режиме прерывания. Когда устройство ввода готово к выдаче информации в МП, оно посылает строб на вход С МБР. При этом сбрасывается в ноль триггер прерывания и на выходе МБР формируется сигнал запроса на прерывание в МП. МП переходит на соответствующую прерывающую программу, в начале исполнения которой определяет устройство, запросившее прерывание. МП посылает сигналы на входы выборки кристалла и принимает данные от устройства ввода с шины данных.

Применение МБР в качестве интерфейсного устройства вывода показано на рис.5.2,в. Принцип работы порта вывода подобен работе порта ввода.

Два МБР могут управлять направлением передачи информации по двунаправленной шине (рис.5.2,г). Сигнал выбора направления (ВН) определяет, какой из двух МБР будет открыт, а какой будет находиться в состоянии высокого сопротивления. Например, при ВН=0 выбирается МБР1, направление передачи информации – слева направо по шине данных.

5.2.4 Программируемый параллельный интерфейс (ппи) - кр580вв55а.

К числу ППИ следует отнести следующие БИС:

КР580ВВ55 (8255-базовый вариант фирмы INTEL)

8255A -улучшенный вариант

МС6820 -базовый вариант(MOTOROLА)

МС6821 -улучшенный вариант.

В состав этих БИС входят программно-доступные регистры управляющих слов (РУС), содержимое которых и определяет режим работы этих м/с. Программный доступ к РУС со стороны МП дает возможность управлять работой ППИ и изменять характеристики интерфейса. Для программирования работы ППИ МП выдает в ППИ управляющее слово, используя для этой цели команду OUT с адресом РУС ППИ.

Микросхема КР580ВВ55А - программируемое устройство ввода-вывода параллельной информации, применяется в качестве программируемых портов ввода-вывода, позволяет сопрягать различные типы периферийных устройств с магистралью данных МПС.

Условное графическое обозначение микросхемы приведено на. рис. 3.18, назначение выводов — в табл. 3.19, структурная схема показана на рис. 3.19,

Обмен информацией между магистралью данных систем и микросхемой КР580ВВ55А осуществляется через 8-разрядный двунаправленный трехстабильный канал данных (D). Для связи с периферийными устройствами используются 24 линии ввода/вывода, сгруппированные в три 8-разрядых канала ВА, ВВ. ВС, направление передачи информации и режимы работы которых определяются программным способом.

Микросхема может функционировать в трех основных режимах. В режиме 0 обеспечивается возможность синхронной программно управляемой передачи данных через два независимых 8-разрядных канала ВА и ВВ и два 4-разрядных канала ВС.

В режиме 1 обеспечивается возможность ввода или вывода .информации в/или из периферийного устройства через два независимых 8-разрядных канала ВА и ВВ по сигналам квантирования. При этом линии канала С используются для приема и выдачи сигналов управления обменом.

В режиме 2 обеспечивается возможность обмена информацией с периферийными устройствами через двунаправленный 8-разрядный канал ВА по сигналам квитирования. Для передачи и приема сигналов управления обменам используются пять линий канала ВС. Выбор соответствующего канала и направление передачи информации через канал определяются сигналами АО, А1 (соединяемые обычно с младшими разрядами канала адреса системы) и сигналами RD#, WR#, CS# в соответствии с табл. 3.20.

Режим работы каждого из каналов ВА, ВВ, ВС определяется содержимым регистра управляющего слова (РУС). Произведя запись управляющего слова в РУС, можно перевести микросхему в один из трех режимов работы: режим 0 - простой ввод-вывод; режим1 - cтробируемый ввод-вывод; режим2- двунаправленный канал.

При подаче сигнала SR РУС устанавливается в состояние, при котором все каналы настраиваются на работу в режиме 0 для ввода информации. Режим работы каналов можно изменять как в начале, так и в процесс выполнения программы, что позволяет обслуживать различные периферийные устройства в определенном порядке одной микросхемой. При изменении режима работы любого канала все выходные и выходные регистры каналов и триггеры состояния сбрасываются. Формат управляющего слова, определяющего режимы работы каналов приведен на рис. 3.21.

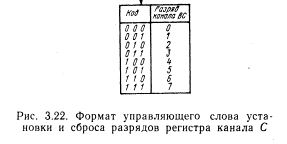

В дополнение к основным режимам работы микросхема обеспечивает возможность программной независимой установки в 1 и сброса в 0 любого из разрядов регистра канала ВС. Формат управляющего слова установки-сброса разрядов регистра канала ВС показан на рис. 3.22.

Временные диаграммы работы ППИ в режимах 0,1,2, а также примеры программирования ППИ показаны в Приложении к «Методические указания по курсовому проектированию». Примеры применения ППИ даны в разделе «Разработка интерфейса многоразрядного индикатора».

5.2.5 Шинный формирователь КР580ВА86 (i8286)

Микросхема КР580ВА86 предназначена для реализации 8-разрядных однонаправленных и двунаправленных буферных схем с тремя состояниями на выходе. На рис.5.3 приведены структурная схема и условное графическое обозначение БИС КР580ВА86. Формирователь КР580ВА87 отличается тем, что имеет инвертирующие буферы.

Т

а

– структурная схема; б – условное

графическое обозначение

Рис.5.3

Шинный формирователь КР580ВА86:

Рис.5.3

Шинный формирователь КР580ВА86:

8

Рис.

5.4 Временные диаграммы работы

формирователей КР570ВА86/ВА87

Рис.

5.4 Временные диаграммы работы

формирователей КР570ВА86/ВА87

5.2.6 Буферный регистр КР580ИР82 (i8282)

В

а

– структурная схема; б – условное

графическое обозначение

Рис.5.5

Буферный регистр КР580ИР82:

Рис.5.5

Буферный регистр КР580ИР82:

О

Рис.5.6.

Временные диаграммы работы регистров

КР580ИР82/ИР83

Рис.5.6.

Временные диаграммы работы регистров

КР580ИР82/ИР83