- •Розділ IX основи проектування цифрових пристроїв на базі програмованих логічних матриць (пліс)

- •9.1. Основи побудови структур простих пліс

- •9.1.1. Плм (програмовані логічні матриці)

- •9.1.2. Пмл (програмована матрична логіка)

- •9.1.3. Мікросхеми програмованої макрологіки

- •9.1.4. Бмк (базові матричні кристали)

- •9.2. Сучасні пліс

- •9.3. Основні параметри пліс

- •9.4. Основи проектування цифрових пристроїв

- •9.4.3. Реалізація простих логічних пристроїв на базі пліс

- •Контрольні питання

9.3. Основні параметри пліс

При виборі фірми-виробника ПЛІС, сімейства і типу розробник цифрових систем повинен користуватися такими критеріями:

логічна ємність, достатня для реалізації проекту, з можливістю майбутнього оновлення;

швидкодія ПЛІС;

схемотехнічні та конструктивні параметри;

наявність або вартість засобів розробки, що включає в себе апаратні та програмні засоби;

наявність технічної та методичної підтримки;

вартість мікросхем та надійність каналів їх придбання.

Виходячи з цих критеріїв, для фахівців, які не мають достатнього досвіду роботи з ПЛІС, рекомендуємо розпочинати роботу з мікросхемами фірми ALTERA (www.altera.com). Ця фірма виготовляє широкий ряд ПЛІС CPLD сімейств MAX3000, MAX7000, MAX9000, а також ПЛІС FPGA сімейств FLEX10K, FLEX6000, FLEX8000. Важливою перевагою є те, що фірма ALTERA забезпечує користувачів безкоштовною версією програмного забезпечення – базовий пакет MAX+plus II BASELINE можна отримати на CD “ALTERA Digital Library” або на офіційному Інтернет-сайті компанії.

ПЛІС фірми ALTERA виготовлені з можливістю програмування безпосередньо на платі. Для програмування та завантаження конфігурації пристрою опубліковані схеми кабелю для завантаження – ByteBlaster та ByteBlasterMV.

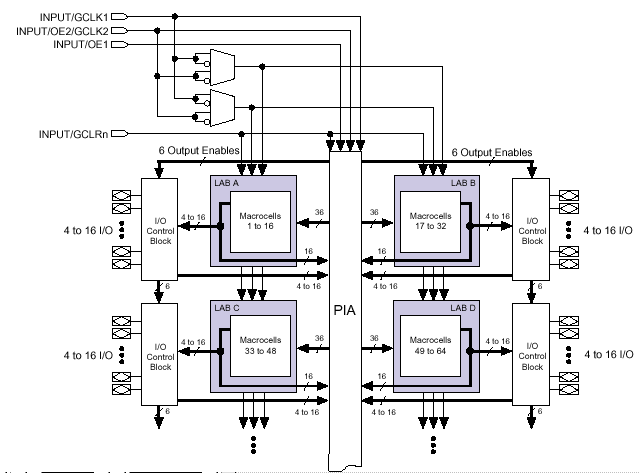

Для пояснення параметрів ПЛІС, з якими користувачу доводиться мати справу при проектуванні цифрових пристроїв, розглянемо особливості функціональної схеми широко використовуваних ІС сімейства МАХ3000 (рис. 9.8).

Рис. 9.8

Основними елементами функціональної схеми є:

логічні блоки (ЛБ) (Logic Array Blocks (LAB));

макроелементи МЕ (Macrocells);

логічні розширювачі (Expanders): паралельний (Parallel) та розподілюваний (Shareble);

програмована матриця з’єднань (ПМЗ) (Programmable Interconnected Array (PIA));

елементи вводу-виводу (ЕВВ) (I/O Control Block).

Велика складність матриці обумовлює виділення групи електричних кіл, які охоплюють всі схеми. Такі електричні кола називаються глобальними. За глобальними колами закріплюється частина виводів (Dedicated Inputs). Це глобальні кола синхронізації, обнуління, установки в Z-стан кожного макроелементу. Разом з цим, ці виводи можуть бути використані як входи або виходи користувача для “швидких “ сигналів, що обробляються ПЛІС.

Як видно з рис. 9.8, в основу архітектури ПЛІС сімейства, що розглядається, покладені логічні блоки, які містять у собі по 16 макроелементів кожний. Логічні блоки з’єднуються за допомогою програмованої матриці з’єднань. Кожен логічний блок має 36 входів з ПМЗ.

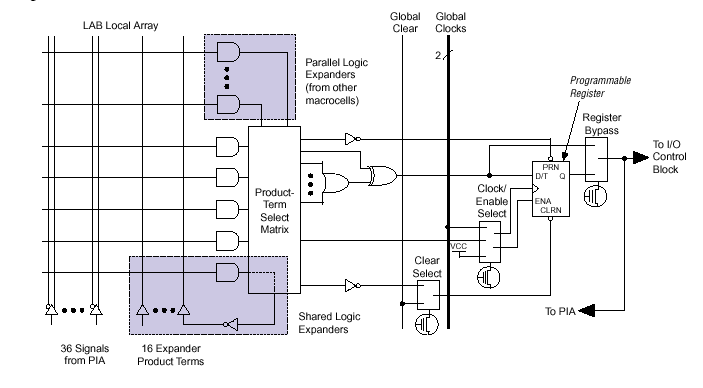

Рис. 9.9

На рис. 9.9 приводиться структурна схема макроелементу ПЛІС сімейства МАХ3000. Вона складається з трьох головних вузлів:

локальної програмованої матриці (ЛПМ) (LAB Local Array);

матриці розподілення термів (МРТ) (Product-Term Select Matrix);

програмованого регістра (ПР) (Programmable Register).

Комбінаційні функції реалізуються на локальній програмованій матриці і матриці розподілення термів, що дозволяє об’єднувати логічні добутки по АБО (OR) або по ВИКЛ. АБО (XOR). Крім цього, матриця розподілення термів дозволяє забезпечити комутацію кола керування тригером макроелементу.

У ПЛІС сімейства МАХ3000 доступні 2 глобальні тактові сигнали, що дозволяє проектувати схеми з двофазною синхронізацією.

З точки зору ємності ПЛІС, вони характеризуються такими параметрами:

логічною ємністю, тобто кількістю еквівалентних логічних елементів типу 2І-НІ;

кількістю макроелементів;

кількістю логічних блоків;

кількістю програмованих користувачем виводів.

У Табл. 9.1 приводяться довідкові дані по ПЛІС фірми ALTERA різних сімейств.

Табл. 9.1

Сімейство

Параметр |

MAX3000 EPM3256A |

FLEX600 EPF6024A |

MAX9000 EPM9560 |

FLEX10K EPF10K250 |

APEX20K EP20K1000 |

Логічна ємність |

5000 |

24000 |

5000 |

250000 |

2670000 |

Кількість макроелементів |

256 |

1960 |

560 |

12160 |

4224 |

Кількість логічних блоків |

16 |

196 |

772 |

20 |

264 |

Кількість виводів для користування |

158 |

45 |

46 |

470 |

780 |

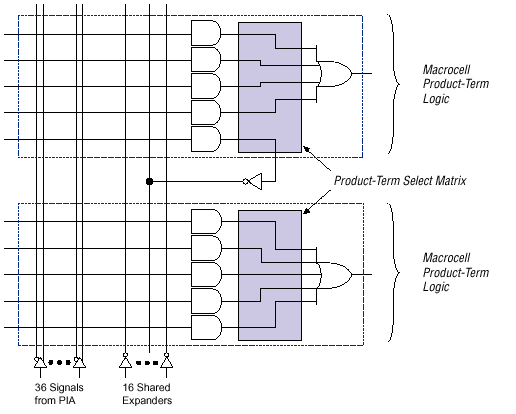

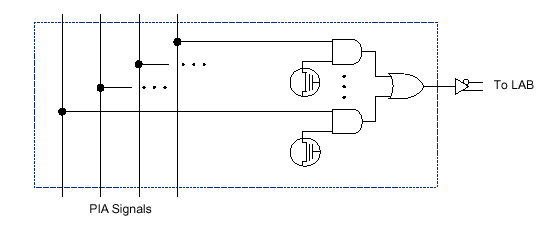

Для реалізації логічних функцій з великою кількістю змінних використовуються логічні розширювачі (див. рис. 9.10, рис. 9.11).

Рис. 9.10

Розподілюваний логічний розширювач (рис. 9.10) дозволяє реалізовувати логічні функції з великою кількістю входів, забезпечуючи можливості об’єднувати МЕ, що входять до складу одного ЛБ. У такий спосіб розподілюваний розширювач формує терм, інверсне значення якого передається матрицею розподілу термів в локальну програмовану матрицю і може бути використано у будь-якому МЕ даного ЛБ.

Як видно з рис. 9.10, наявні 36 сигналів ПМЗ, а також 16 інверсних сигналів з розподілюваних логічних розширювачів, що дозволяє у межах одного ЛБ реалізувати логічну функцію до 52 термів рангу 1.

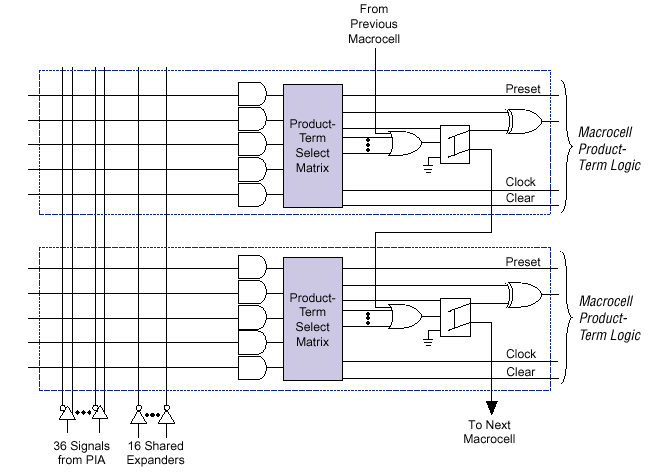

Рис. 9.11

Паралельний логічний розширювач (рис. 9.11) дозволяє використовувати локальні матриці суміжних МЕ для реалізації функцій, в які входять більше 5 термів. Одна ланка паралельних розширювачів може містити до 4 МЕ, реалізуючи функцію 20 термів.

Рис. 9.12

Програмована матриця з’єднань (рис. 9.12) побудована так, що на неї виводяться сигнали від всіх можливих джерел – ЕВВ, сигналів зворотних зв’язків ЛБ, спеціалізованих виділених виводів. При програмуванні забезпечуються тільки необхідні зв’язки для передачі сигналів.

Рис. 9.13

Елементи вводу/виводу ПЛІС (рис. 9.13) дозволяють забезпечити режими роботи на ввід/вивід інформації, а також режими з відкритим колектором та Z-станом.

Мікросхеми сімейства МАХ3000 повністю підтримують стандарт JTAG. Програмування забезпечується підвищеною порівняно з живленням (3,3 В) напругою, яка створюється спеціалізованими схемами помножувачів напруги, що входять до складу ПЛІС.

Послідовність програмування, режим тактування тригерів, конфігурація окремих модулів повністю забезпечуються автоматично під час синтезу проекту в САПР MAX+plus II.

Наступною групою параметрів ПЛІС є часові параметри програмування. Але, оскільки ПЛІС програмуються за допомогою САПР, то їх компілятори повністю забезпечують необхідні часові співвідношення між сигналами і користувачу їх знання необов’язкове.

Для користувача важливими є затримки в розповсюдженні сигналів. До них відносять:

затримки розповсюдження сигналу вхід/вихід;

затримка глобального тактового сигналу до виходу;

час установлення глобального тактового сигналу;

максимальна глобальна тактова частота.

Для ПЛІС сімейства МАХ3000 часові затримки знаходяться у межах 3…5 нс, а максимальна тактова частота досягає до 200 МГц.

ПЛІС, що розглядаються, мають передбачувану величину затримки у розповсюджені сигналу, тому при моделюванні в САПР МАХ+plus II результати часового моделювання відповідатимуть реальним часовим затримкам у мікросхемі. Тому за результатами моделювання можна отримати більш детальні дані по величинах часових затримок сигналу між заданими входами та виходами мікросхеми.