- •Розділ IX основи проектування цифрових пристроїв на базі програмованих логічних матриць (пліс)

- •9.1. Основи побудови структур простих пліс

- •9.1.1. Плм (програмовані логічні матриці)

- •9.1.2. Пмл (програмована матрична логіка)

- •9.1.3. Мікросхеми програмованої макрологіки

- •9.1.4. Бмк (базові матричні кристали)

- •9.2. Сучасні пліс

- •9.3. Основні параметри пліс

- •9.4. Основи проектування цифрових пристроїв

- •9.4.3. Реалізація простих логічних пристроїв на базі пліс

- •Контрольні питання

9.2. Сучасні пліс

Розглянуті у § 9.1 мікросхеми ПЛІС послужили основою для розвитку двох сучасних напрямків ВІС і НВІС з програмованими і репрограмованими структурами. Перший продовжує напрямок розвитку програмованої матричної логіки в серіях CPLD (Complex Programmable Logic Devices), а другий напрямок розвиває БМК в серіях FPGA (Field Programmable Gate Array). Альтернативою обох напрямків стала змішана архітектура НВІС з назвою FLEX (Flexible Logic Element matriX). Зростання рівня інтеграції дало можливість розміщувати на одному кристалі схеми, складність яких відповідає цілим електронним системам.

Сучасний рівень інтеграції НВІС настільки високий, що на кристалі розміщуються мільйони логічних елементів. Реальне та функціональне знання схемотехніки НВІС для розробників цифрової апаратури, особливо фахівців невисокої кваліфікації, не має суттєвого значення. Тому розглянемо лише ті особливості, які можуть дати корисну інформацію.

Програмованість НВІС забезпечується наявністю в ній великої кількості двополюсників (ключів), які за допомогою програмних засобів можуть переводитись користувачем в стан високої або низької (нульової) провідності. Тим самим задається необхідна конфігурація схеми, що формується на кристалі. Кількість програмованих ключів для сучасних ПЛІС досягає декількох мільйонів.

У сучасних ПЛІС використовуються такі типи програмованих ключів:

перемички типу antifuse (тонкі діелектричні пробивані перемички);

ЛІЗМОН-транзистори з подвійним затвором;

ключові польові транзистори, керовані тригерами пам’яті конфігурації.

Програмування з перемичками типу antifuse є одноразовим. Перемички мають малі розміри і в початковому стані пропускають дуже малі струми (≈ 10–15 A). Програмуючий імпульс напруги пробиває перемичку і створює провідний канал. Опір каналу досить точно залежить від величини пробивного струму, що дає можливість створювати перемички з заданою величиною опору. Параметри обох станів перемички можуть зберігатись близько 40 років.

Елементи ЕЕРROM (FLASH) на ЛІЗМОН були розглянуті раніше.

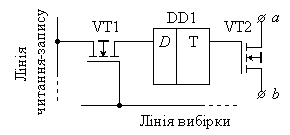

Приклад схеми ключа, керованого тригером пам’яті конфігурації, приводиться на рис. 9.7.

Рис. 9.7

Ключ VT2 забезпечує комутацію ділянки ab в залежності від стану тригера. Тригер, у свою чергу, встановлюється високим потенціалом на лінії вибірки і відповідним сигналом (1 або 0) на лінії читання-запису.

Застосування такого ключа відкриває широкі можливості використання ПЛІС, оскільки час їх запису визначається десятками-сотнями мілісекунд, а витрати часу на стирання взагалі непотрібні.

ВІС, в яких схема створюється з використанням логічних елементів і програмованих ключів, називаються ВІС (НВІС) програмованої логіки.

Дещо іншу архітектуру мають програмовані користувачем вентильні матриці (FPGA). Вони побудовані на основі спеціалізованих блоків ідентичної конфігурації, в якості яких використовуються:

прості логічні елементи;

логічні модулі на основі мультиплексів;

логічні модулі на основі ПЗП;

а також спеціалізовані блоки типу блока вводу-виводу і т. п. Блоки мають можливість об’єднуватись між собою, створюючи необхідну конфігурацію схеми.

Існує досить велика кількість архітектур FPGA, які мало чим можуть бути корисні для схемотехніків цифрових пристроїв.

Складні програмовані логічні схеми (CPLD і FLEX) архітектурно містять в собі центральну комутаційну матрицю та велику кількість функціональних блоків (макроелементів), периферійних блоків. Їх архітектура і схемотехніка досить складна і не має суттєвого значення для розробників цифрової апаратури. Класичними представниками CPLD є мікросхеми МАХ7000 фірми ALTERA. На ринку НВІС представлена велика кількість CPLD і НВІС ПЛМ фірм ALTERA (сімейство МАХ, FLEX, APEX), ATMEL (сімейство ATF1500), VANTIS (сімейство МACН), XILINX (сімейство XC9500) і т. ін. У рамках кожного сімейства є ряд НВІС різних за складністю, вартістю та іншими показниками. У виборі необхідних мікросхем допомагають програмні засоби, призначені для їх програмування.

Наступним станом розвитку ПЛІС стали НВІС, які визначаються як “система на кристалі” (в англомовній літературі SoC – System on Crystal). Поява таких НВІС обумовлена зростанням рівня інтеграції та швидкодії, внаслідок чого з’явилась можливість створювати на кристалі спеціалізовані обчислювальні модулі та цілі процесори, оперативну та постійну пам’ять, периферійні пристрої, а також спеціалізовані пристрої тестування. Зрозуміло, такі ПЛІС мають велику кількість спеціалізованих блоків, але, у той же час, на базі таких ПЛІС виникає можливість будувати спеціалізовані цифрові системи досить високої потужності. До таких ПЛІС відносяться сімейство НВІС типу АРЕХ20К/КE фірми ALTERA, а також сімейство НВІС типу VIRTEX фірми XILINX.

Суттєвою відмінністю ПЛІС останнього покоління є суттєва приближення їх до користувача з точку зору програмування та тестування. Для цього ПЛІС забезпечуються сукупністю засобів та операцій, які дозволяють забезпечити тестування ВНІС без фізичного доступу до кожного з її виводів. Комплекс вмонтованих апаратних і програмних засобів, призначених для розв’язання задач тестового контролю, називається інтерфейсом JTAG (Joint Test Action Group – група, що розробила стандарт тестування). Тестування за JTAG-стандартом має назву “периферійного сканування” (Boundary Scan Testing (BST)). Периферійне сканування дозволяє перевірити роботу мікросхем, монтажні з’єднання мікросхем між собою на друкованій платі, зчитувати сигнали на виводах мікросхеми під час її роботи або керувати цими сигналами.

Важливою властивістю ПЛІС останнього покоління є можливість забезпечення реконфігурації (програмування) в системі, що надає можливість виконувати зміни в логіці їх роботи. Властивість програмованості безпосередньо в системі позначається скороченням ISP (In-System Programmable). Необхідність в використанні цієї властивості виникає при потребі в оновленні системи або при виявленні помилок в роботі.