- •Управляющие эвм, требования к ним по сравнению с пк

- •Датчики угла поворота вала

- •Упрощенный критерий оценки эвм, блок-схема «машины фон-Неймана», сравнение с Гарвардской архитектурой

- •2. Синхронный двигатель (сравнение с асинхронным)

- •Логарифмическая шкала, децибелы

- •2. Полевые транзисторы (field effect transistors - fet)

- •Сигнальные процессоры и плк

- •1. Принцип действия кэШа, многоуровневое кэширование, регистры процессора

- •Функционирование

- •1. Память эвм

- •1. Предвыборка данных, принцип повышения скорости передачи информации для памяти ddr2, ddr3

- •2.Полевые транзисторы с управляющим p-n переходом

- •1. Частотно-регулируемый электропривод переменного токa

- •2. Числовое программное управление (чпу)

- •2. Система пид

- •1. Компьютерные сети в сау (profibus и can)

- •2. Акустическое оформление громкоговорителей (колонки)

- •1. Система scada

- •2. Сквозной акустический такт

- •2. Терморегулирование

- •2. Силовые импульсные цепи

- •1. Основные показатели усилителя

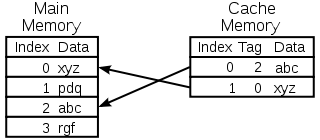

1. Принцип действия кэШа, многоуровневое кэширование, регистры процессора

Кэш[1][2][3] или кеш[4][5][6] (англ. cache, от фр. cacher — «прятать»; произносится [kæʃ] — «кэш») — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы.

Функционирование

Диаграмма

кэша памяти ЦПУ

Диаграмма

кэша памяти ЦПУ

Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа (далее «основная память»). Кэширование применяется ЦПУ, жёсткими дисками, браузерами, веб-серверами, службами DNS и WINS. Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти. Когда клиент кэша (ЦПУ, веб-браузер, операционная система) обращается к данным, прежде всего исследуется кэш. Если в кэше найдена запись с идентификатором, совпадающим с идентификатором затребованного элемента данных, то используются элементы данных в кэше. Такой случай называется попаданием кэша. Если в кэше не найдена запись, содержащая затребованный элемент данных, то он читается из основной памяти в кэш, и становится доступным для последующих обращений. Такой случай называется промахом кэша. Процент обращений к кэшу, когда в нём найден результат, называется уровнем попаданий или коэффициентом попаданий в кэш. Например, веб-браузер проверяет локальный кэш на диске на наличие локальной копии веб-страницы, соответствующей запрошенному URL. В этом примере URL — это идентификатор, а содержимое веб-страницы — это элементы данных. Если кэш ограничен в объёме, то при промахе может быть принято решение отбросить некоторую запись для освобождения пространства. Для выбора отбрасываемой записи используются разные алгоритмы вытеснения. При модификации элементов данных в кэше выполняется их обновление в основной памяти. Задержка во времени между модификацией данных в кэше и обновлением основной памяти управляется так называемой политикой записи. В кэше с немедленной записью каждое изменение вызывает синхронное обновление данных в основной памяти. В кэше с отложенной записью (или обратной записью) обновление происходит в случае вытеснения элемента данных, периодически или по запросу клиента. Для отслеживания модифицированных элементов данных записи кэша хранят признак модификации (изменённый или «грязный»). Промах в кэше с отложенной записью может потребовать два обращения к основной памяти: первое для записи заменяемых данных из кэша, второе для чтения необходимого элемента данных. В случае, если данные в основной памяти могут быть изменены независимо от кэша, то запись кэша может стать неактуальной. Протоколы взаимодействия между кэшами, которые сохраняют согласованность данных, называют протоколами когерентности кэша.

Многоуровневое кэширование. Специфика конструирования современных процессорных ядер привела к тому, что систему кэширования в подавляющем большинстве CPU приходится делать многоуровневой. Кэш первого уровня (самый «близкий» к ядру) традиционно разделяется на две (как правило, равные) половины: кэш инструкций (L1I) и кэш данных (L1D). Это разделение предусматривается так называемой «гарвардской архитектурой» процессора, которая по состоянию на сегодня является самой популярной теоретической разработкой для построения современных CPU. В L1I, соответственно, аккумулируются только команды (с ним работает декодер, см. ниже), а в L1D — только данные (они впоследствии, как правило, попадают во внутренние регистры процессора). «Над L1» стоит кэш второго уровня — L2. Он, как правило, больше по объёму, и является уже «смешанным» — там располагаются и команды, и данные. L3 (кэш третьего уровня), как правило, полностью повторяет структуру L2, и в современных x86 CPU встречается редко. Чаще всего, L3 — это плод компромисса: за счёт использование более медленной и узкой шины, его можно сделать очень большим, но при этом скорость L3 всё равно остаётся более высокой, чем скорость памяти (хотя и не такой высокой, как у L2-кэша). Тем не менее, алгоритм работы с многоуровневым кэшем в общих чертах не отличается от алгоритма работы с одноуровневым, просто добавляются лишние итерации: сначала информация ищется в L1, если её там нет — в L2, потом — в L3, и уже потом, если ни на одном уровне кэша она не найдена — идёт обращение к основной памяти (ОЗУ).

Уровни кэша. Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N. Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L1 разделен на два кэша, кэш команд (инструкций) и кэш данных (Гарвардская архитектура). Большинство процессоров без L1 кэша не могут функционировать. L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт. Зачастую является возможным выполнять несколько операций чтения/записи одновременно. Латентность доступа обычно равна 2−4 тактам ядра. Объём обычно невелик — не более 384 Кбайт. Вторым по быстродействию является L2-cache — кэш второго уровня, обычно он расположен на кристалле, как и L1. В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1−12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в nM Мбайт на каждое ядро приходится по nM/nC Мбайта, где nC количество ядер процессора. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L2. Иногда существует и 4 уровень кэша, обыкновенно он расположен в отдельной микросхеме. Применение кэша 4 уровня оправдано только для высоко производительных серверов имейнфреймов. Проблема синхронизации между различными кэшами (как одного, так и множества процессоров) решается когерентностью кэша. Существует три варианта обмена информацией между кэш-памятью различных уровней, или, как говорят, кэш-архитектуры: инклюзивная, эксклюзивная и неэксклюзивная. Инклюзивная архитектура предполагает дублирование информации кэша верхнего уровня в нижнем (предпочитает фирма Intel). Эксклюзивная кэш-память предполагает уникальность информации, находящейся в различных уровнях кэша (предпочитает фирма AMD). В неэксклюзивной кэши могут вести себя как угодно.

Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором и большой частью недоступен программисту: например, при выборке из памяти очередной команды она помещается в регистр команд (англ.), к которому программист обратиться не может. Имеются также регистры, которые в принципе программно доступны, но обращение к ним осуществляется из программ операционной системы, например, управляющие регистры и теневые регистры дескрипторов сегментов. Этими регистрами пользуются в основном разработчики операционных систем. Существуют также так называемые регистры общего назначения (РОН), представляющие собой часть регистров процессора, использующихся без ограничения в арифметических операциях, но имеющие определенные ограничения, например в строковых. РОН, не характерные для эпохи мейнфреймов типа IBM/370[1] стали популярными в микропроцессорах архитектуры X86 — i8085, i8086 и последующих[2]. Специальные регистры[3] содержат данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д. Часть специальных регистров принадлежит устройству управления, которое управляет процессором путём генерации последовательности микрокоманд. Доступ к значениям, хранящимся в регистрах, как правило, в несколько раз быстрее, чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1-4 Гб[4], суммарная «ёмкость» регистров общего назначения/данных для процессора Intel 80386 и более новых 32 битов * 8 = 256 бит). Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. По типу приёма и выдачи информации различают 2 типа регистров:

С последовательным приёмом и выдачей информации — сдвиговые регистры.

С параллельным приёмом и выдачей информации — параллельные регистры.

Сдвиговые регистры представляют собой последовательно соединённую цепочку триггеров. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

По назначению регистры различаются на:

аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

флаговые — хранят признаки результатов арифметических и логических операций;

общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса;

индексные — хранят индексы исходных и целевых элементов массива;

указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека);

сегментные — хранят адреса и селекторы сегментов памяти;

управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.Адрес

Содержимое

0

Данные или команда

1

…

…

…

…

…

N

…

2. АЧХ акустического тракта

АЧХ — амплитудно-частотная характеристика тракта. Это — частотная зависимость отношения нормированных амплитуд синусоидальных сигналов на выходе и входе тракта. Замечу, что АЧХ лишь косвенно характеризует свойства тракта при передаче несинусоидальных сигналов. ФЧХ — фазо-частотная характеристика. Это — частотная зависимость разности фаз синусоидальных сигналов на выходе и входе тракта. АЧХ и ФЧХ однозначно связаны в большинстве электротехнических цепей преобразованием Гильберта: зная АЧХ, можно однозначно определить ФЧХ и наоборот. Цепи, для которых АЧХ и ФЧХ связаны однозначно, называются минимально-фазовыми. Большинство АС, и в том числе все многополосные, минимально-фазовыми не являются. Амплитудно-частотная характеристика (АЧХ) — функция, показывающая зависимость модуля некоторой комплекснозначной функции от частоты. Также может рассматриваться АЧХ других комплекснозначных функций частоты, например, спектральной плотности мощности сигнала.

АЧХ в теории автоматического управления. АЧХ в теории линейных стационарных систем означает зависимость модуля передаточной функции системы от частоты. АЧХ показывает во сколько раз амплитуда сигнала на выходе системы отличается от амплитуды входного сигнала на всём диапазоне частот. На графике АЧХ по оси абсцисс откладывается частота, а по оси ординат отношение амплитуд выходного и входного сигналов системы. Обычно для частоты используетсялогарифмический масштаб, так как исследуемый диапазон частот может изменяться в достаточно широких пределах (от единиц до миллионов Гц или рад/с). В случае когда логарифмический масштаб используется и на оси ординат, АЧХ превращается в логарифмическую амплитудно-частотную характеристику. ЛАЧХ получила широкое распространение в теории автоматического управления в связи с простотой построения и наглядностью при исследовании систем управления. Амплитудно-частотной характеристикой (АЧХ) линейной цепи называют модуль ее комплексной частотной характеристики. Для четырехполюсного устройства это модуль коэффициента передачи. Из определения следует наиболее простой метод измерения АЧХ: снятие зависимости отношения амплитуд выходного и входного напряжений гармонического сигнала в отдельных частотных точках (“по точкам”) с последующей интерполяцией. На практике обычно снимают зависимость напряжения на выходе исследуемого устройства от частоты при постоянной амплитуде гармонического напряжения на входе. Описанный метод измерения АЧХ “по точкам” основан на использовании перестраиваемого генератора гармонических колебаний и вольтметра. Структурная схема измерительной установки представлена на рис. 1.1, а. Генератор последовательно настраивают на ряд выбранных частот, а напряжение на выходе исследуемого устройства измеряют вольтметром. При этом амплитуду напряжения генератора поддерживают постоянной. Зависимость UВЫХ(f), построенная по результатам измерений, представляет собой АЧХ исследуемой цепи (рис. 1.1, б). Данный способ обеспечивает достаточно высокую точность измерений. Основными источниками погрешностей являются:

1) погрешность установки частоты генератора; 2) погрешность установки амплитуды напряжения на выходе генератора и его нестабильность в процессе измерения АЧХ;3) погрешность вольтметра, измеряющего напряжение на выходе цепи;4) искажения АЧХ, связанные с влиянием выходного сопротивления генератора и входного импеданса вольтметра на параметры исследуемой цепи.

Вклад первых трех источников в общую погрешность измерения может быть уменьшен использованием приборов более высокого класса точности. Влияние генератора снижают выбором способа подключения к измеряемой цепи. Вольтметр следует выбирать с большим входным сопротивлением и минимальной входной емкостью.

Билет 7