- •2.1 Структура мпс

- •2.2. Шинная организая мпс. Адресная система

- •2.6. Структурна схема мікропроцесора.

- •2.3 Загальна структура, та основні функції мікропроцесорів

- •2.4 Режими роботи мп

- •2,5 Основні дані, що характеризують мікропроцесор

- •2.7 Архітектура мікроЕом

- •2.8 Способы адресации команд и схемы их выполнения.

- •2.9 Команди мп кр580ик80 (класифікація, призначення, приклади).

- •2.10 Системи числення.

- •2.12 Коды чисел в мпс.

- •2.11 Переклад з однієї системи числення в іншу.

- •2.13 Арифметичні дії з кодами чисел

- •2.14 Способы представления чисел в микроЭвм.

- •2.17. Оператор switch

- •2,20 Стандартные типы данных

2.1 Структура мпс

МПС в качестве основных необх-ых частей содержит: 1.процессор (МП) – программно-управляемое устройство, осуществляющее процесс цифровой обработки информации и управления им; построены на одной или неск. БИС. 2.память (ЗУ) – используется ЗУ произвольного доступа, т.е. время доступа к любой ячейке памяти одинаково. 3.устр-во ввода/вывода (УВВ) – специальные управляемые регистры – порты.

МПС хар-ся понятием «архитектура» - структурно-логическая организация. Архитектура включает в себя: 1.структурно-логическую схему МПС; 2.способы обращения ко всем доступным для пользователя элементам; 3.способы представления и формат данных; 4.набор команд или операций; 5.назначение и характеристики используемых управляющих и информационных сигналов.

МПС имеют шинную организацию. Виды шин: 1. шина адреса (ША) – однонаправленная шина; по ней выбирается адрес; минимальное число разрядов – 16. 2. шина данных (ШД) – двунаправленная шин; информация идет как от процессора к ЗУ и УВВ, так и обратно; минимальное кол-во разрядов – 8. 3. шина управления (ШУ) – шина имеет сложную направленность. Минимальное число разрядов – от 5 и выше.

МПС по типу архитектуры подраздел-ся: 1. МПС с фоннейменовской архитектурой – программа и данные находятся в общей памяти, доступ к которой осущ-ся по одной и той же ШД; 2. МПС с гарвардской арх-рой – память данных и память команд разделены и имеют отдельные шины.

2.2. Шинная организая мпс. Адресная система

И-ция в МПС передается минимум по трем шинам: Шина адреса (ША, МА, А) Шина данных (ШД, МД, Д) Шина управления (ШУ, МУ, С) Шина адреса – минимальная 16 разрядов, однонаправленная. ШД от 8 и выше, двунаправленная. ШУ от 5 и выше, дву и однонаправленная в целом двунаправленная. С помощью ША организуется адресная система МП. Простейшие из них имеют вид:

![]()

Макс число 216=65536=64К; К=1024

Режимы работы МПС: 1. Режим выполнения программ 2. режим выполнения подпрограмм 3. режим выполнения прерывания. 4. режим прямого доступа к памяти.

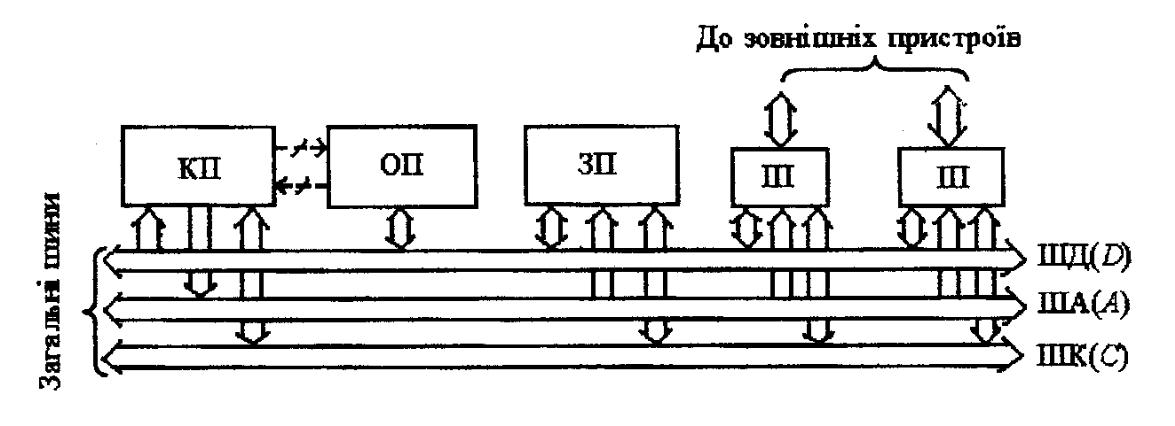

Общая структура магистрально-модульной цифровой системы.

Обычно в составе общей магистрали выделяют отдельные группы линий связи – шины (магистрали) для передачи обозначенного вида информации. Чаще всего выделяют шину данных (D), по которой передаются данные, а в программно-управляющих системах тоже команды, шина адреса А, на которую приходит адрес обратной ячейки ЗП или ПП и ширина управления С, служит для обмена сигналами, которые задают режим работы процессора ЗП и ПП.

2.6. Структурна схема мікропроцесора.

МП складається з наступних основних функціональних ву-злів: арифметико-логічного пристрою ALU (Arithmetic-Logic Unit), пристрою керування і блоку регістрів (рис. 8.10).

До складу блоку регістрів входять: 16-розрядний регістр адреси команди або програмний лічильник PC (Program Counter), 16-розрядний покажчик стека SP (Stack Pointer), 16-розрядний регістр тимчасового збереження {WZ), 16-розрядна схема інкремен-ту-декременту адреси INC/DEC (Increment/Decrement) і шість 8-розрядних регістрів загального призначення (РЗП) В, С, D, Е, Н, L, які можуть використовуватися і як три 16-розрядних регістри (регістрової пари) ВС, DE, IIL. РЗП призначені для збереження і видачі даних. Назва регістрової пари завжди визначається Назвою першого регістра, у якому зберігається старший байт шістнадця-гирозрядного числа. Практично всі арифметичні і логічні дії над даними виконуються в регістрі-акумуляторі АСС (Accumultor).

Регістри відіграють роль акумуляторів, коли в них містяться оброблювані дані, або роль покажчиків, коли в них зберігаються адреси операндів. Вони вибираються за допомогою схеми вибору регістру. Восьмирозрядні дані можуть передаватися на внутрішню шину даних МП через мультиплексор (MUX). Шіст-надцятирозрядні адреси обмінюються між регістрами і буфером адреси В А через адресний регістр-засувку і схему інкременту-декременту адреси.

Система команд МП містить команди довжиною в 1, 2 і З байти інформації. Перший байт команди завжди міститься в регістрі команд IR (Instruction Register). Другий і третій байти багато-байтних команд розміщаються в допоміжних регістрах W і Z. Вибір того чи іншого регістра, які приймають участь у виконанні команди, здійснюється схемою вибору регістрів, яка дешифрує код команди.