- •Часть 2

- •Введение

- •1 Объем учебной программы

- •1.1 Объем теоретической части

- •1.2 Перечень вопросов по защите контрольной работы

- •1.2.1 Основные логические операции.

- •2 Теоретические основы

- •2.1 Конечный автомат

- •2.2 Основные логические операции

- •2.2.1 Операция отрицания

- •2.2.2 Операция логического умножения

- •2.2.3 Операция логического сложения

- •2.2.4 Операция эквиваленция

- •2.2.5 Операция импликация

- •2.2.6 Сумма по модулю 2

- •2.2.7 Штрих Шеффера

- •2.2.8 Стрелка Пирса

- •2.3 Функции одной переменной

- •2.4 Функции двух переменных

- •2.5 Выражение одних элементарных функций через другие

- •2.6 Законы и правила конъюнкции, дизъюнкции и отрицания

- •2.7 Аналитические формы представления лф

- •2.7.1 Представление лф в совершенной дизъюнктивной форме

- •2.7.2 Дизъюнктивная нормальная форма

- •2.7.3 Представление лф в совершенной конъюнктивной форме

- •2.8 Аналитический метод минимизации фл

- •2.9 Метод минимизации фл с помощью карт Карно

- •2 .9.1 Правила минимизации по картам Карно

- •2.9.2 Соседние клетки карт Карно

- •2.9.3 Правило объединения соседних клеток

- •2.9.4 Определение простых импликант

- •2.9.5 Не определенные логические функции в картах Карно

- •2.10 Синтез комбинационных схем

- •2.11 Построение преобразователя кодов

- •2.12 Программируемые логические матрицы

- •3.1.5 Задание 5

- •Пример решения.

- •3.2 Вариантное задание

- •3.2.1 Задание 6

- •Пример решения.

- •4 Требования к оформлению контрольной работы

- •4.1 Перечень технической литературы

2.12 Программируемые логические матрицы

Наряду со стандартными большими интегральными схемами (БИС) и сверхбольшими интегральными схемами (СБИС) существует ряд нестандартных цифровых устройств малого и среднего уровня интеграции (МИС, СИС), общее число которых значительно, так как они чаще подвергаются изменениям.

С целью снижения затрат проектирования, начали выпускать стандартные ИС с программируемой и репрограммируемой структурой.

Первыми представителями таких ИС были программируемые логические матрицы (ПЛМ, PLA – Programmable Logic Array, или Programmable Logic Devices PLD), и дальнейшее их развитие, программируемая матричная логика (ПМЛ, PAL - Programmable Array Logic) и базовые матричные кристаллы БМК, называемые также вентильными матрицами (ВМ, GA – Gate Array).

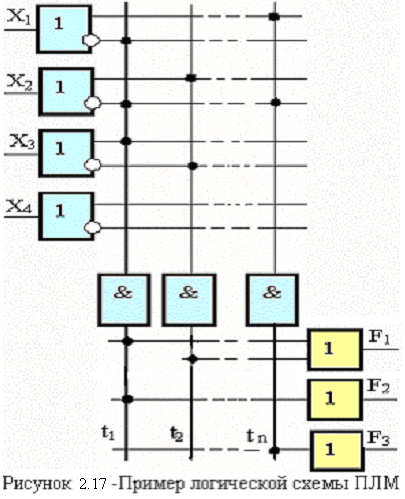

Основой ПЛМ служит последовательность программируемых матриц логических элементов «И, ИЛИ». В структуру входят и буферные входные/выходные каскады, предназначенные для согласования нагрузок, управления (например, разрешение выхода с помощью сигнала ОЕ) и других более сложных действий. Базовая структура ПЛМ приведена на рисунке 2.17.

Основными параметрами ПЛМ являются число входных переменных m, число термов s, число выходов n. Входные переменные Хі поступают через блок согласования буферных входных каскадов на матрицу конъюнкторов, где образуется до s минтермов. Число минтермов не может превышать число конъюнкторов матрицы. Минтермы поступают на матрицу дизъюнкций, где и реализуются дизъюнктивные нормальные формы воспроизводимых логических функций. Таким образом, любую систему функций (меньше n) реализует схема двухуровневой логики. Комбинации минтермов и ДНФ определяются программированием ПЛМ с последующим прожиганием связей на простих приспособлениях. ПЛМ выпускаются как на основе биполярной технологии, так и на МОП- транзисторах.

На рисунке 2.17 показана ПЛМ, воспроизводящая цифровое устройство, отвечающее поведению системы логических функций:

F1=Х1Х2 Х3 + Х2Х3;

F2=Х1Х2 Х3;

F3= Х1Х2.

На рисунке 2.18 в упрощенном виде показана схемотехника биполярной ПЛМ серии К556 РТ1 с программированием прожигания перемычек.

Элементами связи в матрице И служат диоды, соединяющие горизонтальные и вертикальные шины, как показано на рисунке 2.18 а.

Совместно с резистором и источником питания, цепи выработки минтермов образуют обычные, диодные схемы И. До прожигания все перемычки целы, и диоды связи размещены во всех узлах координатной сетки. В этом случае, на всех выходах будет ноль, т. к. ХХ = 0.

После программирования и прожигания, в схеме остаются только необходимые перемычки, а ненужные связи устраняются. Высокий уровень выходного напряжения (логическая единица) появится на шине t только при наличии высоких уровней на всех выходах буферных каскадов. Низкое напряжение будет, если хотя бы на одном входе будет низкое напряжение, т. к. открывается диод этого входа. Так выполняется операция И.

Элементами связи в матрице ИЛИ служат транзисторы (рисунок 2.18 б), параллельно включенные по схеме многоэмитерного повторителя относительно входов (минтермов) и образующие схему ИЛИ относительно выхода Fi.

В схемах на МОП- транзисторах в качестве базовых логических ячеек используются элементы Пирса (ИЛИ-НЕ) или элементы Шеффера (И-НЕ) в обеих матрицах одинаковые, например, ИЛИ-НЕ.

Очень часто при проектировании логическая мощность ПЛМ используется не полно. Это особенно проявляется при синтезе переключательных функций, где нет пересечений по одинаковым минтермам. В этих случаях, возможность использования различных комбинаций И по различным ИЛИ становится излишней. Отказ от этого исключает программирование матрицы ИЛИ и приводит к структуре программируемой матричной логики (ПМЛ, PAL,GAL). В ПМЛ выходы первой матрицы И жестко распределены между элементами ИЛИ второй, теперь уже не программируемой, матрицы. Поэтому, ПМЛ имеют меньшую функциональную гибкость, но их изготовление проще.

Включение в состав ПЛМ, помимо комбинационной части, схем с памятью на кристаллах (например, D–триггеров, регистров) позволяет проектировать различные микропрограммные цифровые автоматы.

3 ЗАДАНИЯ КОНТРОЛЬНОЙ РАБОТЫ

3.1 Общие задания

Пункты общего, безвариантного задания выполняются студентами в соответствии с теоретическими основами подразделов 2.2– 2.9 и приведенными примерами решений.

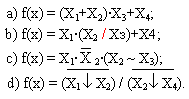

3.1.1 Задание 1

Найти значения

следующих булевых функций f(x),

подставляя набор Х![]() =1,

Х2=0, Х3=0, Х

=1,

Х2=0, Х3=0, Х![]() =1

входных переменных:

=1

входных переменных:

Пример решения.

![]()

3.1.2 Задание 2

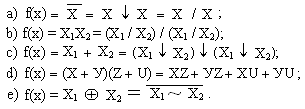

С помощью таблиц истинности показать справедливость следующих соотношений:

Пример решения.

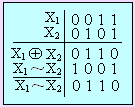

Построим таблицу истинности для функции f(x)=x1 x2 = .

Сравнивая функции первой и третьей строки, видим, что значения их одинаковы т. е. равенство справедливо.

3.1.3 Задание 3

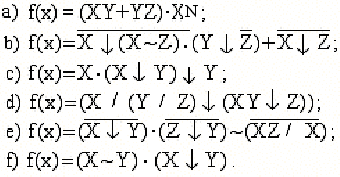

Преобразовать к минимальной, дизъюнктивной (или конъюнктивной) нормальной форме, представив в алгебре Буля следующие логические функции:

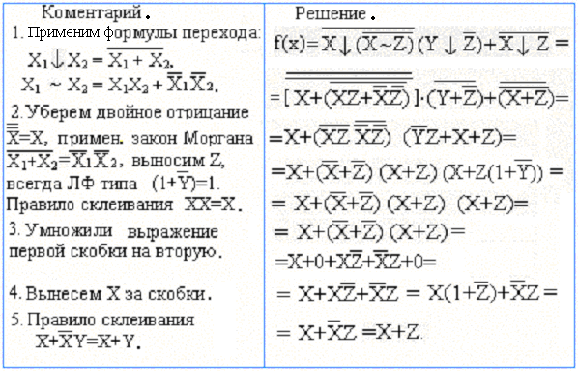

Пример решения.

Проведем преобразование следующей логической функции:

![]()

Кроме логических

операций алгебры Буля «И, ИЛИ, НЕ» в

данной функции присутствуют операции

«штрих Пирса (![]() )»

и «эквиваленция (

)»

и «эквиваленция (![]() )».

Решение и комментарий представлены в

блоке.

)».

Решение и комментарий представлены в

блоке.

3 .1.4 Задание

4

.1.4 Задание

4

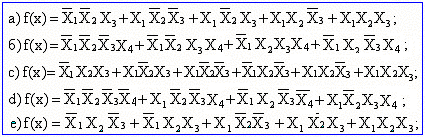

Применяя аналитические методы решения, минимизировать функции и нарисовать рисунки логических схем.

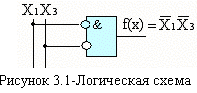

Пример решения.

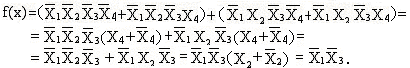

Пусть необходимо минимизировать функцию

![]()

Отыскиваем

минтермы которые отличаются между собой

только одной координатой. Группируем

эти минтермы. Выносим за скобки одинаковые

переменные. В скобках остается

![]() ,

что всегда равно 1 по определению операции

дизъюнкции. Повторяем аналогичные

действия до полного склеивания. Для

нашего примера имеем:

,

что всегда равно 1 по определению операции

дизъюнкции. Повторяем аналогичные

действия до полного склеивания. Для

нашего примера имеем:

Для

функции

![]() строим логическую схему (см. рисунок

3.1)

строим логическую схему (см. рисунок

3.1)

на одном элементе «И» с инверсией сигналов по входу.