- •Абсолютные способы формирования исполнительного адреса операндов

- •Встраиваемые и промышленные компьютеры

- •В чем суть mmx-технологии и потоковых simd-расширений?

- •В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

- •Иерархическая структура памяти компьютера

- •Как определяется энергоэффективность процессора?

- •Как осуществляется декодирование команд x86 в процессоре Intel Nehalem?

- •Как осуществляется декодирование команд x86 в ядре amd k10?

- •Какие новые возможности появились у процессора с введением расширения команд sse-2, sse-3?

- •Какими преимуществами обладают блейд-серверы?

- •Какими характеристиками должен обладать пк?

- •Классификация mimd-систем по способу взаимодействия процессоров

- •Классификация архитектуры sisd с краткой характеристикой классов

- •Классификация интерфейсов

- •Классификация ноутбуков

- •Классификация методов построения центрального устройства управления процессора

- •Классификация микро-эвм с краткой характеристикой классов

- •Классификация пк по способу использования

- •Классификация серверов с пояснениями

- •Классификация, состав, платформы, производители карманных пк

- •Классификация способов организации simd-архитектуры с пояснениями

- •Конвейерная технология выполнения команд

- •Концепция виртуальной памяти

- •Косвенная адресация операндов

- •Логическая организация центрального процессора эвм

- •Методы обновления строк в основной и кэш-памяти

- •Методы повышения пропускной способности оперативной памяти (организация памяти на ddr sdram)

- •Методы повышения пропускной способности оперативной памяти (расслоение обращений)

- •Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

- •Методы замещения строк в кэш-памяти

- •Методы ускорения процессов обмена информацией между оп и внешними запоминающими устройствами

- •Механизм преобразования виртуального адреса в физический при страничной организации памяти

- •Механизм стековой адресации по способу lifo

- •Модульная структура процессора Intel Nehalem

- •Обобщенная структура эвм и основные направления её развития

- •Обобщенный формат команд x86

- •Общие принципы организации оперативной памяти компьютера

- •Объяснить суть процедуры переименования регистров в современных процессорах

- •Определить назначение, количество, принцип действия исполнительных устройств процессора Intel Nehalem

- •Определить назначение, количество, принцип действия исполнительных устройств ядра amd k10

- •Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

- •Определить назначение, структуру, количество основных функциональных регистров ia-32

- •Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

- •Регистры ммх-технологии

- •Организация многоуровневой кэш-памяти

- •Основные отличительные черты epic-концепции

- •Основные характерные черты cisc-архитектуры

- •Основные характерные черты risc-архитектуры

- •Основные характерные черты vliw-архитектуры

- •Основные характерные черты суперскалярной обработки

- •Особенности микроархитектуры Intel Core

- •Особенности микроархитектуры Intel Sandy Bridge

- •Особенности микроархитектуры процессоров Intel Nehalem

- •Особенности архитектуры процессоров x86-64 (amd64, Intel64)

- •Особенности процессоров семейства Intel Westmere

- •Особенности процессорного ядра amd k10

- •Особенности системы команд в ia-64

- •Охарактеризуйте все виды производительности компьютера

- •Перечислить основные требования, которые учитываются при проектировании серверов

- •Принцип работы кэш-памяти с полностью ассоциативным распределением

- •Принцип работы кэш-памяти с частично ассоциативным распределением

- •Программно-управляемая передача данных в компьютере

- •Программно-управляемый приоритет прерывающих программ

- •Прямой доступ к памяти в компьютере

- •Показать развитие и классификацию однопроцессорных архитектур

- •Почему появились многоядерные структуры процессоров и технологии многопоточности?

- •Развитие cisc-системы команд x86 (по годам)

- •Распределение оперативной памяти динамическими разделами

- •Распределение оперативной памяти перемещаемыми разделами

- •Распределение оперативной памяти фиксированными разделами

- •Расширение системы команд aes-ni, avx

- •Реализация адресации «Базирование с индексированием»

- •Реализация адресации операндов «Базирование способом совмещения составляющих исполнительного адреса Аи»

- •Реализация адресации операндов «Базирование способом суммирования»

- •Реализация индексной адресации операндов

- •Регистровые структуры процессоров ia-64

- •Регистровые структуры процессоров x86-64 архитектуры (amd64, Intel64)

- •Сегментное распределение виртуальной памяти

- •Сильносвязанные и слабосвязанные многопроцессорные системы

- •Системная организация эвм на базе чипсетов Intel

- •Страничное распределение виртуальной памяти

- •Стратегия развития процессоров Intel

- •Странично-сегментное распределение памяти

- •Структура кэш-памяти с прямым распределением данных

- •Теги и дескрипторы

- •Типовая структура кэш-памяти

- •Типы данных ia-32 (без mmx и sse)

- •Типы данных ia-64

- •Типы данных mmx-технологии

- •Типы данных sse, sse-2 расширений

- •Форматы команд risc-процессора

- •Формат команд в ia-64, структура пакета инструкций

- •Функции центрального устройства управления процессором

- •Функциональные возможности, назначение, платформы рабочих станций

- •Функциональные возможности, назначение, современные разработки ультра-мобильных и планшетных пк

- •Функциональные возможности, области применения, основные производители мэйнфреймов

- •Функциональные возможности, пути развития, современные разработки супер-эвм

- •Характеристики интерфейсов

- •Характеристики системы прерывания

- •Характерные черты современных универсальных микропроцессоров

- •Центральное устройство управления микропрограммного типа

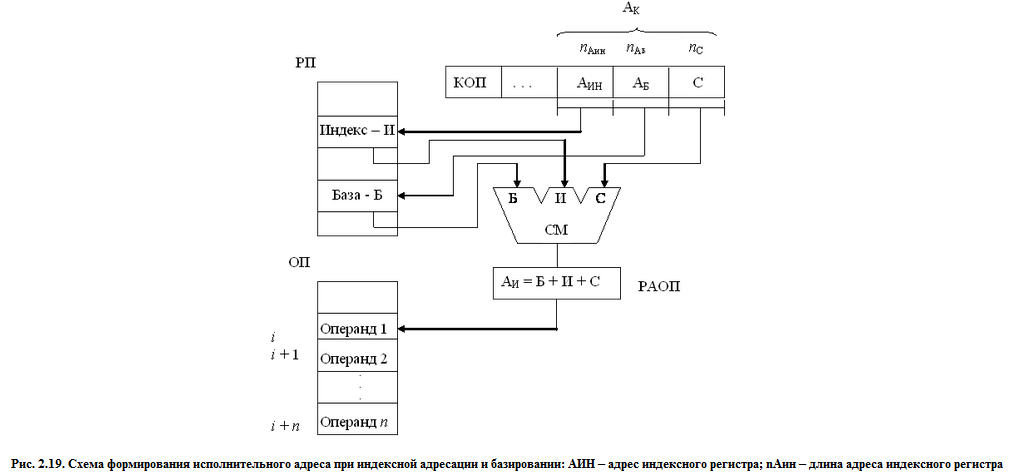

Реализация индексной адресации операндов

Для работы программ с массивами, требующими однотипных операций над элементами массива, удобно использовать индексную адресацию. Схема индексной адресации аналогична базированию путем суммирования (рис.2.17). В этом случае адрес i-го операнда в массиве определяется как сумма начального адреса массива (задаваемого полем смещения С) и индекса И, записанного в одном из регистров РП, называемом теперь индексным регистром. Адрес индексного регистра задается в команде полем адреса индекса – АИН (аналогично АБ).

В каждом i-м цикле содержимое индексного регистра изменяется на величину постоянную (часто равную 1). Использование индексной адресации значительно упрощает программирование циклических алгоритмов.

Для эффективной работы при относительной адресации применяется комбинированная индексация с базированием, при которой адрес операнда вычисляется как сумма трех величин (рис. 2.19):

АИОП = Б + И + С.

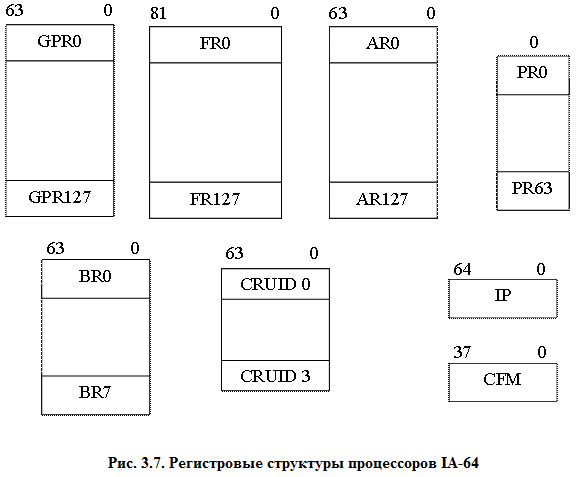

Регистровые структуры процессоров ia-64

В состав регистровых файлов IA-64 входят: 128 регистров общего назначения GPR (64-разрядных); 128 регистров с плавающей запятой FR (82-разрядных); 128 прикладных регистров (в основном 64-разрядных) AR; 64 одноразрядных регистров предикатов PR; 8 регистров переходов BR (64-разрядных); не менее 4-х регистров идентификатора процесса CPUID; счетчик команд IP; регистр маркера текущего окна CFM стека регистров и др.

64-разрядные регистры GPR0–GPR127 применяются не только для целочисленных операций IA-64; GPR8–GPR31 в режиме IA-32 используются также под целочисленные регистры и регистры селекторов и дескрипторов сегментов IA-32. GPR0–GPR31 называются статическими регистрами (GPR0 всегда содержит 0), а GPR32–GPR127 – стекируемыми регистрами. Статические регистры «видны» всем программам. Стекируемые регистры становятся доступными в программной единице через окно стека регистров, включающее локальные и выходные регистры, число которых задается командой alloc.

82-разрядные регистры с плавающей запятой FR0–FR127 также подразделяются на статические (FR0–FR31, причем всегда FR0 = 0.0, FR1 = 1.0) и вращаемые (FR32–FR127). FR8–FR31 в режиме IA-32 содержат числа с плавающей запятой и мультимедийные регистры. Вращение регистров является в некотором роде частным случаем переименования регистров, применяемого в современных суперскалярных процессорах с внеочередным выполнением команд. В отличие от них (переименование регистров осуществляется аппаратно) вращение регистров в IA-64 управляется программно.

Прикладные регистры AR0–AR127 – специализированные. Ряд AR-регистров является фактически регистрами IA-32. AR0–AR7 называются регистрами ядра. Запись в них привилегированна, но они доступны на чтение в любом приложении и используются для передачи приложению сообщений от операционной системы. AR16 (RSC) – регистр конфигурации стека регистров, используемый для управления работой стека регистров IA-64. AR40 (FPSR) – регистр состояния для команд с плавающей запятой IA-64.

Регистры предикатов PR0–PR63 являются одноразрядными, в них помещаются результаты выполнения команд сравнения. Обычно эти команды устанавливают сразу два соседних регистра PR в состояния «1» – истина, «0» – ложь или наоборот в зависимости от значения условия. Такая избыточность обеспечивает дополнительную гибкость.

64-разрядные регистры переходов BR0–BR7 применяются для указания адреса перехода в соответствующих командах перехода (если адрес перехода не кодируется в команде явно).

В регистрах CPUID 0 и CPUID 1 находится информация о производителе, в регистре CPUID 2 – серийный номер процессора, а в регистре CPUID 3 задается тип процессора (семейство, модель, версия архитектуры и т. п.) и число CPUID-регистров. Разряды регистра CPUID4 указывают на поддержку конкретных особенностей IA-64, которые реализованы в данном процессоре.