- •Абсолютные способы формирования исполнительного адреса операндов

- •Встраиваемые и промышленные компьютеры

- •В чем суть mmx-технологии и потоковых simd-расширений?

- •В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

- •Иерархическая структура памяти компьютера

- •Как определяется энергоэффективность процессора?

- •Как осуществляется декодирование команд x86 в процессоре Intel Nehalem?

- •Как осуществляется декодирование команд x86 в ядре amd k10?

- •Какие новые возможности появились у процессора с введением расширения команд sse-2, sse-3?

- •Какими преимуществами обладают блейд-серверы?

- •Какими характеристиками должен обладать пк?

- •Классификация mimd-систем по способу взаимодействия процессоров

- •Классификация архитектуры sisd с краткой характеристикой классов

- •Классификация интерфейсов

- •Классификация ноутбуков

- •Классификация методов построения центрального устройства управления процессора

- •Классификация микро-эвм с краткой характеристикой классов

- •Классификация пк по способу использования

- •Классификация серверов с пояснениями

- •Классификация, состав, платформы, производители карманных пк

- •Классификация способов организации simd-архитектуры с пояснениями

- •Конвейерная технология выполнения команд

- •Концепция виртуальной памяти

- •Косвенная адресация операндов

- •Логическая организация центрального процессора эвм

- •Методы обновления строк в основной и кэш-памяти

- •Методы повышения пропускной способности оперативной памяти (организация памяти на ddr sdram)

- •Методы повышения пропускной способности оперативной памяти (расслоение обращений)

- •Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

- •Методы замещения строк в кэш-памяти

- •Методы ускорения процессов обмена информацией между оп и внешними запоминающими устройствами

- •Механизм преобразования виртуального адреса в физический при страничной организации памяти

- •Механизм стековой адресации по способу lifo

- •Модульная структура процессора Intel Nehalem

- •Обобщенная структура эвм и основные направления её развития

- •Обобщенный формат команд x86

- •Общие принципы организации оперативной памяти компьютера

- •Объяснить суть процедуры переименования регистров в современных процессорах

- •Определить назначение, количество, принцип действия исполнительных устройств процессора Intel Nehalem

- •Определить назначение, количество, принцип действия исполнительных устройств ядра amd k10

- •Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

- •Определить назначение, структуру, количество основных функциональных регистров ia-32

- •Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

- •Регистры ммх-технологии

- •Организация многоуровневой кэш-памяти

- •Основные отличительные черты epic-концепции

- •Основные характерные черты cisc-архитектуры

- •Основные характерные черты risc-архитектуры

- •Основные характерные черты vliw-архитектуры

- •Основные характерные черты суперскалярной обработки

- •Особенности микроархитектуры Intel Core

- •Особенности микроархитектуры Intel Sandy Bridge

- •Особенности микроархитектуры процессоров Intel Nehalem

- •Особенности архитектуры процессоров x86-64 (amd64, Intel64)

- •Особенности процессоров семейства Intel Westmere

- •Особенности процессорного ядра amd k10

- •Особенности системы команд в ia-64

- •Охарактеризуйте все виды производительности компьютера

- •Перечислить основные требования, которые учитываются при проектировании серверов

- •Принцип работы кэш-памяти с полностью ассоциативным распределением

- •Принцип работы кэш-памяти с частично ассоциативным распределением

- •Программно-управляемая передача данных в компьютере

- •Программно-управляемый приоритет прерывающих программ

- •Прямой доступ к памяти в компьютере

- •Показать развитие и классификацию однопроцессорных архитектур

- •Почему появились многоядерные структуры процессоров и технологии многопоточности?

- •Развитие cisc-системы команд x86 (по годам)

- •Распределение оперативной памяти динамическими разделами

- •Распределение оперативной памяти перемещаемыми разделами

- •Распределение оперативной памяти фиксированными разделами

- •Расширение системы команд aes-ni, avx

- •Реализация адресации «Базирование с индексированием»

- •Реализация адресации операндов «Базирование способом совмещения составляющих исполнительного адреса Аи»

- •Реализация адресации операндов «Базирование способом суммирования»

- •Реализация индексной адресации операндов

- •Регистровые структуры процессоров ia-64

- •Регистровые структуры процессоров x86-64 архитектуры (amd64, Intel64)

- •Сегментное распределение виртуальной памяти

- •Сильносвязанные и слабосвязанные многопроцессорные системы

- •Системная организация эвм на базе чипсетов Intel

- •Страничное распределение виртуальной памяти

- •Стратегия развития процессоров Intel

- •Странично-сегментное распределение памяти

- •Структура кэш-памяти с прямым распределением данных

- •Теги и дескрипторы

- •Типовая структура кэш-памяти

- •Типы данных ia-32 (без mmx и sse)

- •Типы данных ia-64

- •Типы данных mmx-технологии

- •Типы данных sse, sse-2 расширений

- •Форматы команд risc-процессора

- •Формат команд в ia-64, структура пакета инструкций

- •Функции центрального устройства управления процессором

- •Функциональные возможности, назначение, платформы рабочих станций

- •Функциональные возможности, назначение, современные разработки ультра-мобильных и планшетных пк

- •Функциональные возможности, области применения, основные производители мэйнфреймов

- •Функциональные возможности, пути развития, современные разработки супер-эвм

- •Характеристики интерфейсов

- •Характеристики системы прерывания

- •Характерные черты современных универсальных микропроцессоров

- •Центральное устройство управления микропрограммного типа

Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

Регистры ММХ-технологии

При реализации ММХ-операций регистры данных FPU используются как 64-разрядные регистры ММ0 – ММ7, где могут храниться несколько целочисленных операндов (восемь 8-разрядных, четыре 16-разрядных, два 32-разрядных или один 64-разрядный), над которыми одновременно выполняется поступившая в процессор команда.

Регистры SSE, SSE-2 расширений

Потоковые команды расширений SSE, SSE-2 используют восемь 128-разрядных регистров. ХММ0 – ХММ7, в которых могут храниться несколько вещественных или целочисленных операндов, и новый регистр состояния и управления MXCSR.

Регистр состояния и управления MXCSR содержит: поле флагов возникновения исключений (разряды 0 – 5), поле маскирования исключений (разряды 7 – 12), поле установления режима округления данных (разряды 13, 14), поле FZ (15 разряд); 6, 16 – 31 разряды не используются.

127 0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XMM0 |

|

Регистр MXCSR |

|||||||||||||||

XMM1 |

|

||||||||||||||||

XMM2 |

|

31 - 16 |

15 |

14 13 |

12 |

12 |

10 |

|

|

7 |

|

5 |

4 |

|

|

|

0 |

XMM3 |

|

… |

F |

RC |

P |

U |

0 |

Z |

D |

I |

R |

P |

U |

0 |

Z |

D |

I |

XMM4 |

|

Z |

M |

M |

M |

|

M |

M |

|||||||||

XMM5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XMM6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XMM7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Определить назначение, структуру, количество основных функциональных регистров ia-32

В процессорах IA-32 можно выделить следующие группы регистров:

Основные функциональные регистры: 1. регистры общего назначения (GPR); 2. указатель команд; 3. регистр флагов; 4. регистры сегментов.

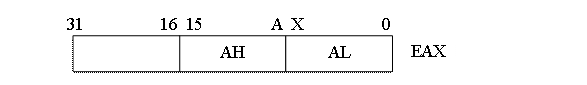

1. Регистры общего назначения. Восемь 32-разрядных регистров (EAX, ECX, EDX, EBS, EBP, ESP, ESI, EDI) предназначены для хранения данных и адресов. Они поддерживают работу с данными разрядностью 1, 8, 16 и 32 бита, битовыми полями длиной от 1 до 32 бит и адресами размером 16 и 32 бита. Младшие 16 разрядов этих регистров (рис.3.2) доступны отдельно при использовании соответствующего имени, например регистр ЕАХ (имя АХ для 16 разрядов).

При операциях с байтами можно отдельно обращаться к младшему байту (разряды 0 – 7) и старшему байту (8 – 15) по именам AL и AH. Доступ к отдельным байтам обеспечивает дополнительную гибкость при операциях с данными.

С труктура

регистра общего назначения

труктура

регистра общего назначения

2 .

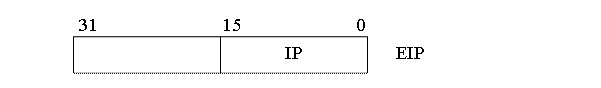

Указатель команд. Указатель команд

(см. рис) представляет собой 32-разрядный

регистр с именем EIP, содержимое которого

используется в качестве смещения при

определении адреса следующей выполняемой

команды. Смещение задается относительно

базового адреса сегмента команд CS.

Младшие 16 бит (0 – 15)

содержат 16-разрядный указатель команд

с именем IP, который используется при

16-разрядной адресации. Указатель

команд непосредственно программисту

недоступен. Его содержимое изменяется

при выполнении команд передачи управления

и прерываний. 3. Регистр

флагов. Регистр флагов является

32-разрядным, имеет имя EFLAGS. Его разряды

содержат признаки результата выполнения

команды, управляют обработкой прерываний,

последовательностью вызываемых задач,

вводом/выводом и рядом других процедур.

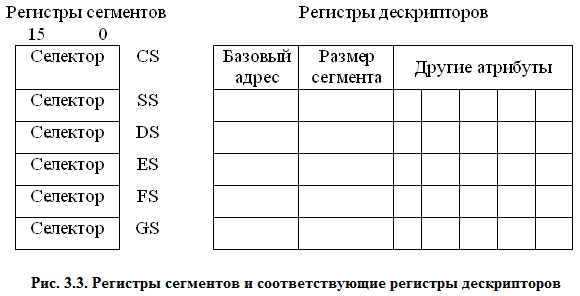

4. Регистры сегментов и дескрипторы

сегментов. Шесть 16-разрядных сегментных

регистров (CS, SS, DS, ES, FS, GS) содержат значения

селекторов сегментов, указывающих на

текущие адресуемые сегменты памяти. С

каждым из них связан программно-недоступный

регистр дескриптора сегмента. В защищенном

режиме каждый сегмент может иметь размер

от 1 байта до 4 Гбайт, в режиме реальных

адресов максимальный размер сегмента

составляет 64 Кбайта.

.

Указатель команд. Указатель команд

(см. рис) представляет собой 32-разрядный

регистр с именем EIP, содержимое которого

используется в качестве смещения при

определении адреса следующей выполняемой

команды. Смещение задается относительно

базового адреса сегмента команд CS.

Младшие 16 бит (0 – 15)

содержат 16-разрядный указатель команд

с именем IP, который используется при

16-разрядной адресации. Указатель

команд непосредственно программисту

недоступен. Его содержимое изменяется

при выполнении команд передачи управления

и прерываний. 3. Регистр

флагов. Регистр флагов является

32-разрядным, имеет имя EFLAGS. Его разряды

содержат признаки результата выполнения

команды, управляют обработкой прерываний,

последовательностью вызываемых задач,

вводом/выводом и рядом других процедур.

4. Регистры сегментов и дескрипторы

сегментов. Шесть 16-разрядных сегментных

регистров (CS, SS, DS, ES, FS, GS) содержат значения

селекторов сегментов, указывающих на

текущие адресуемые сегменты памяти. С

каждым из них связан программно-недоступный

регистр дескриптора сегмента. В защищенном

режиме каждый сегмент может иметь размер

от 1 байта до 4 Гбайт, в режиме реальных

адресов максимальный размер сегмента

составляет 64 Кбайта.

Селектор в CS обеспечивает обращение к текущему сегменту команд, селектор в SS — к текущему сегменту стека, селекторы в DS, ES, FS, GS — к текущим сегментам данных. Каждый регистр дескриптора содержит базовый адрес сегмента, 32-разрядный размер сегмента и другие необходимые атрибуты.

Когда в регистр сегмента загружается новое значение селектора, содержимое соответствующего регистра дескриптора автоматически корректируется. В реальном режиме базовый адрес сегмента получается путем сдвига значения селектора на 4 разряда влево (20 разрядов), максимальный размер и атрибуты сегмента в реальном режиме имеют фиксированные значения.