- •Абсолютные способы формирования исполнительного адреса операндов

- •Встраиваемые и промышленные компьютеры

- •В чем суть mmx-технологии и потоковых simd-расширений?

- •В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

- •Иерархическая структура памяти компьютера

- •Как определяется энергоэффективность процессора?

- •Как осуществляется декодирование команд x86 в процессоре Intel Nehalem?

- •Как осуществляется декодирование команд x86 в ядре amd k10?

- •Какие новые возможности появились у процессора с введением расширения команд sse-2, sse-3?

- •Какими преимуществами обладают блейд-серверы?

- •Какими характеристиками должен обладать пк?

- •Классификация mimd-систем по способу взаимодействия процессоров

- •Классификация архитектуры sisd с краткой характеристикой классов

- •Классификация интерфейсов

- •Классификация ноутбуков

- •Классификация методов построения центрального устройства управления процессора

- •Классификация микро-эвм с краткой характеристикой классов

- •Классификация пк по способу использования

- •Классификация серверов с пояснениями

- •Классификация, состав, платформы, производители карманных пк

- •Классификация способов организации simd-архитектуры с пояснениями

- •Конвейерная технология выполнения команд

- •Концепция виртуальной памяти

- •Косвенная адресация операндов

- •Логическая организация центрального процессора эвм

- •Методы обновления строк в основной и кэш-памяти

- •Методы повышения пропускной способности оперативной памяти (организация памяти на ddr sdram)

- •Методы повышения пропускной способности оперативной памяти (расслоение обращений)

- •Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

- •Методы замещения строк в кэш-памяти

- •Методы ускорения процессов обмена информацией между оп и внешними запоминающими устройствами

- •Механизм преобразования виртуального адреса в физический при страничной организации памяти

- •Механизм стековой адресации по способу lifo

- •Модульная структура процессора Intel Nehalem

- •Обобщенная структура эвм и основные направления её развития

- •Обобщенный формат команд x86

- •Общие принципы организации оперативной памяти компьютера

- •Объяснить суть процедуры переименования регистров в современных процессорах

- •Определить назначение, количество, принцип действия исполнительных устройств процессора Intel Nehalem

- •Определить назначение, количество, принцип действия исполнительных устройств ядра amd k10

- •Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

- •Определить назначение, структуру, количество основных функциональных регистров ia-32

- •Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

- •Регистры ммх-технологии

- •Организация многоуровневой кэш-памяти

- •Основные отличительные черты epic-концепции

- •Основные характерные черты cisc-архитектуры

- •Основные характерные черты risc-архитектуры

- •Основные характерные черты vliw-архитектуры

- •Основные характерные черты суперскалярной обработки

- •Особенности микроархитектуры Intel Core

- •Особенности микроархитектуры Intel Sandy Bridge

- •Особенности микроархитектуры процессоров Intel Nehalem

- •Особенности архитектуры процессоров x86-64 (amd64, Intel64)

- •Особенности процессоров семейства Intel Westmere

- •Особенности процессорного ядра amd k10

- •Особенности системы команд в ia-64

- •Охарактеризуйте все виды производительности компьютера

- •Перечислить основные требования, которые учитываются при проектировании серверов

- •Принцип работы кэш-памяти с полностью ассоциативным распределением

- •Принцип работы кэш-памяти с частично ассоциативным распределением

- •Программно-управляемая передача данных в компьютере

- •Программно-управляемый приоритет прерывающих программ

- •Прямой доступ к памяти в компьютере

- •Показать развитие и классификацию однопроцессорных архитектур

- •Почему появились многоядерные структуры процессоров и технологии многопоточности?

- •Развитие cisc-системы команд x86 (по годам)

- •Распределение оперативной памяти динамическими разделами

- •Распределение оперативной памяти перемещаемыми разделами

- •Распределение оперативной памяти фиксированными разделами

- •Расширение системы команд aes-ni, avx

- •Реализация адресации «Базирование с индексированием»

- •Реализация адресации операндов «Базирование способом совмещения составляющих исполнительного адреса Аи»

- •Реализация адресации операндов «Базирование способом суммирования»

- •Реализация индексной адресации операндов

- •Регистровые структуры процессоров ia-64

- •Регистровые структуры процессоров x86-64 архитектуры (amd64, Intel64)

- •Сегментное распределение виртуальной памяти

- •Сильносвязанные и слабосвязанные многопроцессорные системы

- •Системная организация эвм на базе чипсетов Intel

- •Страничное распределение виртуальной памяти

- •Стратегия развития процессоров Intel

- •Странично-сегментное распределение памяти

- •Структура кэш-памяти с прямым распределением данных

- •Теги и дескрипторы

- •Типовая структура кэш-памяти

- •Типы данных ia-32 (без mmx и sse)

- •Типы данных ia-64

- •Типы данных mmx-технологии

- •Типы данных sse, sse-2 расширений

- •Форматы команд risc-процессора

- •Формат команд в ia-64, структура пакета инструкций

- •Функции центрального устройства управления процессором

- •Функциональные возможности, назначение, платформы рабочих станций

- •Функциональные возможности, назначение, современные разработки ультра-мобильных и планшетных пк

- •Функциональные возможности, области применения, основные производители мэйнфреймов

- •Функциональные возможности, пути развития, современные разработки супер-эвм

- •Характеристики интерфейсов

- •Характеристики системы прерывания

- •Характерные черты современных универсальных микропроцессоров

- •Центральное устройство управления микропрограммного типа

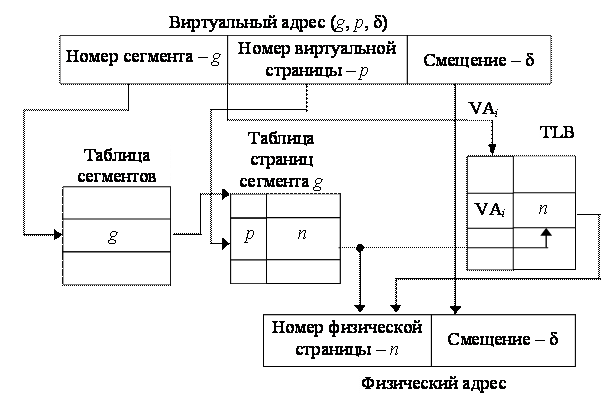

Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

Процесс преобразования адресов посредством таблиц является достаточно длительным и, естественно, приводит к снижению производительности системы. С целью ускорения этого процесса используется специальная полностью ассоциативная кэш-память (рис. 4.17), которая называется буфером преобразования адресов TLB (translation lookaside buffer).

В иртуальный

адрес страницы VAi,

составленный из полей g и p,

передается в TLB в качестве

поискового признака (тега). Он сравнивается

с тегами (VA) всех ячеек

TLB, и при совпадении из

найденной ячейки выбирается физический

адрес страницы n,

позволяющий сформировать полный

физический адрес элемента данных,

находящегося в ОП. Если совпадение не

произошло, то трансляция адресов

осуществляется обычными методами через

таблицы сегментов и страниц. Эффективность

преобразования адресов с использованием

TLB зависит от коэффициента

«попадания» в кэш-памяти, т. е. от того,

насколько редко приходится обращаться

к табличным методам трансляции адресов.

Учитывая принцип локальности программ

и данных, можно сказать, что при первом

обращении к странице, расположенной в

ОП, физический адрес определяется с

помощью таблиц и загружается в

соответствующую ячейку TLB.

Последующие обращения к странице

выполняются с использованием TLB.

иртуальный

адрес страницы VAi,

составленный из полей g и p,

передается в TLB в качестве

поискового признака (тега). Он сравнивается

с тегами (VA) всех ячеек

TLB, и при совпадении из

найденной ячейки выбирается физический

адрес страницы n,

позволяющий сформировать полный

физический адрес элемента данных,

находящегося в ОП. Если совпадение не

произошло, то трансляция адресов

осуществляется обычными методами через

таблицы сегментов и страниц. Эффективность

преобразования адресов с использованием

TLB зависит от коэффициента

«попадания» в кэш-памяти, т. е. от того,

насколько редко приходится обращаться

к табличным методам трансляции адресов.

Учитывая принцип локальности программ

и данных, можно сказать, что при первом

обращении к странице, расположенной в

ОП, физический адрес определяется с

помощью таблиц и загружается в

соответствующую ячейку TLB.

Последующие обращения к странице

выполняются с использованием TLB.

Рис. 4.17. Механизм преобразования адресов с использованием TLB

Методы замещения строк в кэш-памяти

Способ определения строки, удаляемой из кэш-памяти, называется стратегией замещения. Для замещения строк кэш-памяти существует несколько методов: метод замещения наиболее давнего по использованию объекта — строки, метод LRU (замещение наименее используемой информации); метод FIFO (первым пришёл — первым вышел) и метод произвольного замещения. В первом случае среди строк, являющихся объектами замещения, выбирается строка, к которой наиболее длительное время не было обращений. По методу FIFO среди всех строк, являющихся объектами замещения, выбирается та, которая самой первой была переслана в кэш-память. И наконец, по последнему методу строка выбирается произвольно. Реализация этих методов упрощается в указанной последовательности, но наибольшим эффектом обладает метод замещения наиболее давнего по использованию объекта (строки).

Для реализации этого метода необходимо манипулировать строками, которые являются объектами замещения, с помощью LRU-стека. При каждой загрузке в этот стек помещается строка, в результате чего при замене используется строка, хранящаяся в наиболее глубокой позиции стека, и эта строка удаляется из стека. При доступе к строке, которая уже содержится в LRU-стеке, эта строка удаляется из стека и заново загружается в него. Стек типа LRU устроен таким образом, что, чем дольше к строке не было доступа, тем в более глубокой позиции она располагается. Реализация стека типа LRU, позволяющего с высокой скоростью выполнять такую операцию, усложняется по мере увеличения числа строк.

По методу частично ассоциативного распределения число строк в каждом стеке LRU равно числу строк в одной группе, и так как это число мало (порядка 2 – 4), то для каждой группы необходимо использовать свой стек. Если число групп сравнительно велико, то оснащение каждой из них стековым механизмом приводит к повышению стоимости.