- •Абсолютные способы формирования исполнительного адреса операндов

- •Встраиваемые и промышленные компьютеры

- •В чем суть mmx-технологии и потоковых simd-расширений?

- •В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

- •Иерархическая структура памяти компьютера

- •Как определяется энергоэффективность процессора?

- •Как осуществляется декодирование команд x86 в процессоре Intel Nehalem?

- •Как осуществляется декодирование команд x86 в ядре amd k10?

- •Какие новые возможности появились у процессора с введением расширения команд sse-2, sse-3?

- •Какими преимуществами обладают блейд-серверы?

- •Какими характеристиками должен обладать пк?

- •Классификация mimd-систем по способу взаимодействия процессоров

- •Классификация архитектуры sisd с краткой характеристикой классов

- •Классификация интерфейсов

- •Классификация ноутбуков

- •Классификация методов построения центрального устройства управления процессора

- •Классификация микро-эвм с краткой характеристикой классов

- •Классификация пк по способу использования

- •Классификация серверов с пояснениями

- •Классификация, состав, платформы, производители карманных пк

- •Классификация способов организации simd-архитектуры с пояснениями

- •Конвейерная технология выполнения команд

- •Концепция виртуальной памяти

- •Косвенная адресация операндов

- •Логическая организация центрального процессора эвм

- •Методы обновления строк в основной и кэш-памяти

- •Методы повышения пропускной способности оперативной памяти (организация памяти на ddr sdram)

- •Методы повышения пропускной способности оперативной памяти (расслоение обращений)

- •Методы преобразования виртуального адреса в физический при странично-сегментном распределении памяти с использованием tlb

- •Методы замещения строк в кэш-памяти

- •Методы ускорения процессов обмена информацией между оп и внешними запоминающими устройствами

- •Механизм преобразования виртуального адреса в физический при страничной организации памяти

- •Механизм стековой адресации по способу lifo

- •Модульная структура процессора Intel Nehalem

- •Обобщенная структура эвм и основные направления её развития

- •Обобщенный формат команд x86

- •Общие принципы организации оперативной памяти компьютера

- •Объяснить суть процедуры переименования регистров в современных процессорах

- •Определить назначение, количество, принцип действия исполнительных устройств процессора Intel Nehalem

- •Определить назначение, количество, принцип действия исполнительных устройств ядра amd k10

- •Определить назначение, структуру, количество регистров mmx-технологии и расширений sse, sse2

- •Определить назначение, структуру, количество основных функциональных регистров ia-32

- •Определить назначение, структуру, количество регистров процессора обработки чисел с плавающей точкой ia-32 (x87)

- •Регистры ммх-технологии

- •Организация многоуровневой кэш-памяти

- •Основные отличительные черты epic-концепции

- •Основные характерные черты cisc-архитектуры

- •Основные характерные черты risc-архитектуры

- •Основные характерные черты vliw-архитектуры

- •Основные характерные черты суперскалярной обработки

- •Особенности микроархитектуры Intel Core

- •Особенности микроархитектуры Intel Sandy Bridge

- •Особенности микроархитектуры процессоров Intel Nehalem

- •Особенности архитектуры процессоров x86-64 (amd64, Intel64)

- •Особенности процессоров семейства Intel Westmere

- •Особенности процессорного ядра amd k10

- •Особенности системы команд в ia-64

- •Охарактеризуйте все виды производительности компьютера

- •Перечислить основные требования, которые учитываются при проектировании серверов

- •Принцип работы кэш-памяти с полностью ассоциативным распределением

- •Принцип работы кэш-памяти с частично ассоциативным распределением

- •Программно-управляемая передача данных в компьютере

- •Программно-управляемый приоритет прерывающих программ

- •Прямой доступ к памяти в компьютере

- •Показать развитие и классификацию однопроцессорных архитектур

- •Почему появились многоядерные структуры процессоров и технологии многопоточности?

- •Развитие cisc-системы команд x86 (по годам)

- •Распределение оперативной памяти динамическими разделами

- •Распределение оперативной памяти перемещаемыми разделами

- •Распределение оперативной памяти фиксированными разделами

- •Расширение системы команд aes-ni, avx

- •Реализация адресации «Базирование с индексированием»

- •Реализация адресации операндов «Базирование способом совмещения составляющих исполнительного адреса Аи»

- •Реализация адресации операндов «Базирование способом суммирования»

- •Реализация индексной адресации операндов

- •Регистровые структуры процессоров ia-64

- •Регистровые структуры процессоров x86-64 архитектуры (amd64, Intel64)

- •Сегментное распределение виртуальной памяти

- •Сильносвязанные и слабосвязанные многопроцессорные системы

- •Системная организация эвм на базе чипсетов Intel

- •Страничное распределение виртуальной памяти

- •Стратегия развития процессоров Intel

- •Странично-сегментное распределение памяти

- •Структура кэш-памяти с прямым распределением данных

- •Теги и дескрипторы

- •Типовая структура кэш-памяти

- •Типы данных ia-32 (без mmx и sse)

- •Типы данных ia-64

- •Типы данных mmx-технологии

- •Типы данных sse, sse-2 расширений

- •Форматы команд risc-процессора

- •Формат команд в ia-64, структура пакета инструкций

- •Функции центрального устройства управления процессором

- •Функциональные возможности, назначение, платформы рабочих станций

- •Функциональные возможности, назначение, современные разработки ультра-мобильных и планшетных пк

- •Функциональные возможности, области применения, основные производители мэйнфреймов

- •Функциональные возможности, пути развития, современные разработки супер-эвм

- •Характеристики интерфейсов

- •Характеристики системы прерывания

- •Характерные черты современных универсальных микропроцессоров

- •Центральное устройство управления микропрограммного типа

В чем суть mmx-технологии и потоковых simd-расширений?

Еще одним примером SIMD - архитектуры является технология MMX, которая существенно улучшила архитектуру микропроцессоров фирмы Intel. Она разработана для ускорения выполнения мультимедийных и коммуникационных программ. В ММХ используются 4 новых типа данных и 57 новых инструкций. Команды ММХ выполняют одну и ту же функцию с различными частями данных, например: 8 байт графических данных передаются в процессор как одно упакованное 64-х разрядное число и обрабатываются одной командой.

Следующим шагом по пути использования SIMD-архитектуры в микропроцессорах фирмы Intel (Pentium III) явились потоковые SIMD-расширения (SSE), которые реализуют 70 новых SIMD-инструкций, оперирующих со специальными 128-битными регистрами. Каждый из этих регистров хранит 4 вещественных числа одинаковой точности. Таким образом, выполняя операцию над двумя регистрами, SSE фактически оперирует четырьмя парами чисел, т.е. благодаря этому процессор может выполнять до четырех операций одновременно.

В чем суть матричного и векторно-конвейерного способов организации simd-архитектуры

Суть матричной структуры заключается в том, что имеется множество процессорных элементов, исполняющих одну и ту же команду над различными элементами матрицы, объединенных коммутатором. Основная проблема заключается в программировании обмена данными между процессорными элементами через коммутатор.

В отличие от матричной структуры, векторно-конвейерная структура компьютера содержит конвейер операций, на котором обрабатываются параллельно элементы векторов и полученные результаты последовательно записываются в единую память. При этом отпадает необходимость в коммутаторе процессорных элементов, служащем камнем преткновения в матричных компьютерах.

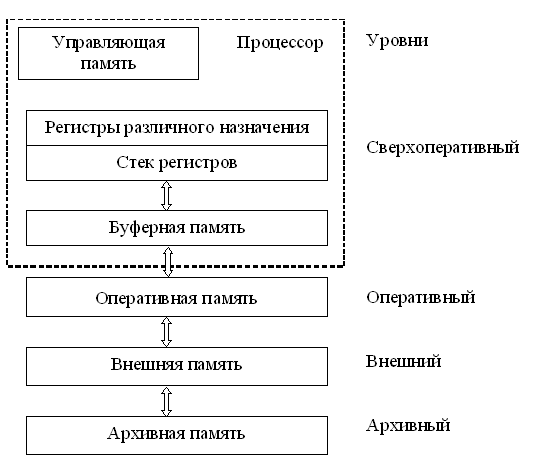

Иерархическая структура памяти компьютера

Стоимость памяти составляет значительную часть общей стоимости ЭВМ. Исходя из этого, память ЭВМ организуется в виде иерархической структуры запоминающих устройств, обладающих различным быстродействием и емкостью. Чем выше уровень, тем выше быстродействие соответствующей памяти, но меньше её емкость. Система управления памятью обеспечивает обмен информационными блоками между уровнями, причем обычно первое обращение к блоку информации вызывает его перемещение с низкого медленного уровня на более высокий. Это позволяет при последующих обращениях к данному блоку осуществлять его выборку с более быстродействующего уровня памяти.

Сравнительно небольшая емкость оперативной памяти компенсируется практически неограниченной емкостью внешних запоминающих устройств. Однако эти устройства работают намного медленнее, чем оперативная память. Исходя из этого, вычислительный процесс должен протекать с возможно меньшим числом обращений к внешней памяти.

Н епрерывный

рост производительности ЭВМ проявляется,

в первую очередь, в повышении скорости

работы процессора. Быстродействие ОП

также растет, но все время отстает от

быстродействия аппаратных средств

процессора в значительной степени

потому, что одновременно происходит

опережающий рост её емкости, что делает

более трудным уменьшение времени цикла

работы памяти. Вследствие этого

быстродействие ОП часто оказывается

недостаточным для обеспечения требуемой

производительности ЭВМ.Возникающая

проблема выравнивания их пропускных

способностей решается путем использования

сверхоперативной буферной памяти

небольшой емкости и повышенного

быстродействия.

епрерывный

рост производительности ЭВМ проявляется,

в первую очередь, в повышении скорости

работы процессора. Быстродействие ОП

также растет, но все время отстает от

быстродействия аппаратных средств

процессора в значительной степени

потому, что одновременно происходит

опережающий рост её емкости, что делает

более трудным уменьшение времени цикла

работы памяти. Вследствие этого

быстродействие ОП часто оказывается

недостаточным для обеспечения требуемой

производительности ЭВМ.Возникающая

проблема выравнивания их пропускных

способностей решается путем использования

сверхоперативной буферной памяти

небольшой емкости и повышенного

быстродействия.

При обращении к блоку данных, находящемуся на оперативном уровне, его копия пересылается в сверхоперативную буферную память (СБП). Последующие обращения производятся к копии блока данных, находящейся в СБП. Поскольку время выборки из сверхоперативной буферной памяти tСБУ (несколько наносекунд) много меньше времени выборки из оперативной памяти tОП, введение в структуру памяти СБП приводит к уменьшению эквивалентного времени обращения tЭ по сравнению с tОП:

tЭ = tСБП + atОП ,

где a = (1 — q) и q — вероятность нахождения блока в СБП в момент обращения к нему, т. е. вероятность «попадания».

В основе такой организации взаимодействия ОП и СБП лежит принцип локальности обращений, согласно которому при выполнении какой-либо программы (практически для всех классов задач) большая часть обращений в пределах некоторого интервала времени приходится на ограниченную область адресного пространства ОП, причем обращения к командам и элементам данных этой области производятся многократно. Это позволяет копии наиболее часто используемых участков программ и некоторых данных загрузить в СБП и таким образом обеспечить высокую вероятность попадания q. Высокая эффективность применения СБП достигается при q i 0,9.

Буферная память не является программно доступной. Это значит, что она влияет только на производительность ЭВМ, но не должна оказывать влияния на программирование прикладных задач. Поэтому она получила название кэш-памяти (в переводе с английского — тайник). В структуре одних ЭВМ используется объединенная кэш-память команд и данных, в других ЭВМ — раздельные кэш-памяти для команд и для данных. В современных компьютерах применяют многоуровневую кэш-память (до трех уровней), которая еще больше способствует производительности ЭВМ.