- •Логические операции и элементарные логические функции.

- •2. Законы отрицания

- •3. Комбинационные законы

- •3.Способы представления логических функций. Минимизация функций алгебры логики методом Вейча-Карно.

- •3. Логические элементы. Параметры логических элементов. Типы выходных каскадов.

- •4. Типовые комбинационные схемы. Назначение, принципы построения, примеры использования.

- •5.Триггеры.

- •6.Регистры. Классификация, принципы построения, выполняемые функции, примеры использования.

- •7. Счётчики: назначение, классификация, принципы построения, примеры использования

- •8. Полупроводниковая память: назначение, классификация. Принципы построения адресных зу.

- •9. Принцип работы эвм. Классификация мп. Программная модель мп Intel 8086. Сегментация памяти

- •10. Система памяти эвм. Особенности памяти типа стек. Назначение и принцип действия кэш-памяти.

- •Общие замечания

- •Целостность данных

- •11. Система команд универсального микропроцессора.

- •Команды передачи управления.

- •13.Организация взаимодействия человека оператора с вычислительной системой.

- •14. Видеосистемы пк типа ibm pc. Устройство и характеристики мониторов.

- •15. Виды обмена с внешними устройствами.

- •16.Внешний интерфейс. Примеры реализации

- •17. Обобщенная структура микропроцессорной информационной измерительно-управляющей системы(ииус). Схемы построения многоканальных измерительных систем.

- •18. Микроконтроллеры: назначение, особенности архитектуры. Типовые периферийные устройства.

- •19. Измерение временных параметров импульсно-модулированных сигналов. Формирование импульсно-модулированных сигналов управления.

7. Счётчики: назначение, классификация, принципы построения, примеры использования

Устройство которое подсчитывает число событий происходящих на их входе (либо положительный, либо отрицательный перепад).

По способу построения счётчики делятся на:

синхронные (параллельные)

асинхронные (последовательные)

По направлению счёта:

прямые

реверсивные

универсальные – которые могут складывать и вычитать

По системе счисления:

двоичные

двоично – десятичные

специальные

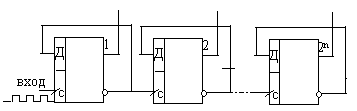

Основу составляют: Счётчик на базе Т-триггера (счётный триггер)

- прямой асинхронный двоичный счётчик.

2n – все выходы счётчика. n – количество триггеров.

Временные диаграммы (3-х разрядный)

|

|

2 |

1 |

4 |

2 |

1 |

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

1 1 1 1 0 0 0 0 |

1 1 0 0 1 1 0 0 |

1 0 1 0 1 0 1 0 |

Счёт в прямом направлении, если снимать с прямых входов. Инверсные входы будут образовывать обратный счёт.

Недостаток: быстродействие прямо пропорционально количеству разрядов.

В параллельных счётчиках сигнал синхронизации подаётся одноактно, а функция счётчика реализуется за счёт схемы подключения выхода счётчика по выходам счётчика.

Современные микросхемы счётчиков имеют разъёмы для наращивания разряда.

8. Полупроводниковая память: назначение, классификация. Принципы построения адресных зу.

Полупроводниковые ЗУ служат для хранения и обработки информации, обмена его с другими устройствами. Основные параметры ЗУ являются альтернативными друг другу: > информационная емкость противоречит быстродействию, что в свою очередь не сочетается с ценой. В связи с этим память в современных ЭВМ/ЦУ имеет многоступенчатую иерархическую структуру: 1ур – Регистровые ЗУ – встроенные в процессор (наиболее б/д память небольшого объема) – сокращение количества обращений к др. видам памяти. СОЗУ, РОН, РФ. 2 ур. – КЭШ память служит для хранения копий информации, участвующей в текущих операциях обмена. Размер – 512 кБ, высокое быстродействие обеспечивает повышение производительности системы в целом. 3 ур. – Основная память – полупроводниковая, постоянная или оперативная память ОЗУ, ПЗУ имеет достаточно большой объем но менее быстродействующая. Память хранит используемый в текущий момент фрагмент программы вместе с данными. Быстродействие в идеале должно быть согласовано с быстрод. процессора. В этом случае отпадает необходимость в КЭШ памяти. 4 ур. – специальные виды памяти – многопортовая, ассоциативная, видеопамять, буферы промежуточного хранения и др. Многопортовая ОЗУ. 5 ур – Внешняя память ВЗУ: магнитные диски, CD, флеш. Многие виды ВЗУ представляют собой механические устройства с вращающимся носителем информации, что ограничивает быстродействие таких устройств. ВЗУ имеют значительно большую емкость чем основная память при значительно более низком быстродействии. Особенность – возможность хранения информации при отсутствии питания. Основные параметры ЗУ: 1) Информационная емкость – max возможный объем хранимой информации (бит, байт, кбит, кбайт, Мбайт – 220б, Гбайт – 230б; если шина 32 разрядн – 232/230=4Гб), 2) Организация ЗУ – произведение числа хранимых слов на их разрядность: 2048*8=2кБайт, 3) Быстродействие ЗУ оценивается временем записи, длительностью цикла чтения-записи. Время считывания – интервал между моментами появления сигнала чтения и слова на выходе ЗУ. Время записи – интервал после появления сигнала записи, достаточного для установления запоминающей ячейки в состояние, заданное входным кодом. Минимально допустимый интервал между последовательными циклами чтения-записи образует соответствующий цикл доступа. Длительности цикла в чтении и записи несколько больше собственно цикла чтения и записи. Это связано с тем, что после выполнения операции требуется некоторое время для восстановления начала записи ЦУ.

Классификация ЗУ по способу доступа: 1)Адресные (Rom – ROM-M, P-ROM, EROM, EEROM, FLASH; RAM: статические: асинхронные, синхронные, конвейерные; динамические: стандартные, квазистандартные, повышенного быстродействия), 2) Последовательные (буферного типа – FIFO, LIFO, файловые, циклические), 3) Ассоциативные (Полностью ассоциативные, с прямым отображением, наборно-ассоциативные).

При адресном доступе код на адресн. входах указывает ячейку, к которой происходит обращение. Все ячейки в момент обращения равнодоступны, следов-но время обращения к любой ячейке одинаково. Другие типы ЗУ часто строится на базе адресных ЗУ (ROM, RAM, ОЗУ). ROM –read only memory – память только для чтения – ПЗУ. RAM – random access memory – память с произвольным доступом ОЗУ. ОЗУ – для хранения данных, которые могут быть изменены в произвольный момент времени: фрагмент исполняемой программы вместе с используемыми данными. Хранит информацию при наличии питания. Не является энергонезависимой памятью. Отличие между статическими и динамическими ОЗУ осуществляется в построении запоминающей ячейки. Ячейки статической ОЗУ – простейший асинхронный RS-триггер. Ячейка динамической ОЗУ представляет конденсатор, выполняемый в виде МОП-структуры. Информация в динамической запоминающей ячейке хранится в виде заряда конденсатора. Т.к. заряд конденсатора с течением времени уменьшается, ячейки динамического ОЗУ необходимо подвергать регенерации. (контроллеры регенерации –SRAM static RAM, DRAM - dynamic RAM). В случае асинхронных ЗУ сигналы управления могут быть как импульсными, так и потенциальными. В синхронных статических ОЗУ некоторые сигналы обязательно должны быть импульсными (сигн. управления – напр. сигнал выборки кристалла CS), позволяют привязать цикл обращения к тактам процессора. В конвейерных ОЗУ организован конвейерный принцип обработки информации, согласно которому цикл обработки (обращения к памяти) разбивается на несколько фаз. Конвейерной называют такую организацию исполнения команд обращения к памяти, при которой в каждом такте одновременно выполняются несколько команд, находящихся в различных фазах обработки. При конвейерной организации обмен осуществляется пакетами. Первое обращение в пакете – длинное (стандартное), 2е и последующие – более быстрые, за счет эффекта от конвейера.

Динамические ОЗУ характеризуются наибольшей информационной емкостью и относительно невысокой стоимостью. Как правило, именно они составляют основную память вычислительной машины.

В ПЗУ время записи >> времени чтения. Информация записывается в спец режиме (режиме программирования). Время программирования 1 запоминающей ячейки зависит от типа ПЗУ. В принципе, время считывания из ПЗУ соизмеримо с временем считывания из ОЗУ. ПЗУ – энергонезависимое устройство, хранящее информацию без питания. По типу запомин ячеек ПЗУ делятся на: масочные (ROMM – однократно программируемые), однократно программируемые (PROM), перепрограммируемые с УФ стиранием (EPROM – стирается сразу вся информация), перепрограммируемые с электрическим стиранием (EEPROM), Flash- память. 2 оставшихся типа предполагают электрическое стирание (можно стирать и программировать на плате). Избирательное стирание (до 1 блока). Flash программируется том же напряжении, при котором считывается (5V). Остальные используют дополнительные источники питания 12-25V.

Последовательные (Буферные, файловые, циклические).

-В буферах типа FIFO даже одна запись после записи в пустой буфер сразу доступна для чтения.

-В файловых ЗУ запись доступна для чтения только после заполнения буфера.

-В циклических ЗУ снова доступны одно за другим, кот определяются емкостью ЗУ, к такому типу ЗУ относят видеопамять.

-Кадровый буфер хранит инф-цию о пикселях.

Ассоциативные (полная ассоциация,с прямым отображением,наборн. ассоциат)

В ассоциативных ЗУ – поиск инф-ции осущ по некоторому пр-ку, а не по расположению в памяти (по адресу и месту расположения в буфере).

Стек-часть оперативной памяти процессора, буфер для временного хранения данных, кот представляет собой память с последующим доступом-стек.

Кэш – служит для хранения копий информации с памяти участвующей в текущей операции обмена.

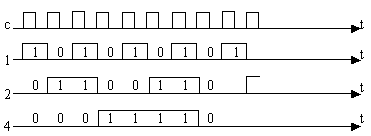

Основные структуры адресных ЗУ:

2D – структура – двухмерная, с однокоординатной выборкой. ЗУ состоит из дешифратора адреса (DC), накопителя, усилителя записи/считывания, схема управления. Код, подаваемый на вход DC, активизирует одну из строк накопителей. В режиме записи усилитель считывания подключает входы данных запоминающих элементов накопителя. В результате входной код записывается в запомин элемент выбранной строки. В режиме чтения на выходах данных устанавливается код = содержимому ячеек активизированной строки накопителя. Направлением передачи данных управляет внешний сигнал Read/Write, обычно 0/1. Сигнал выборки кристалла CS – разрешает работу микросхемы вообще. Информационная емкость Vзу=2nx m=разрядность одной ячейки x на количество ячеек выхода. Недостаток структуры: сложность адресного дешифратора при большой информационной емкости.

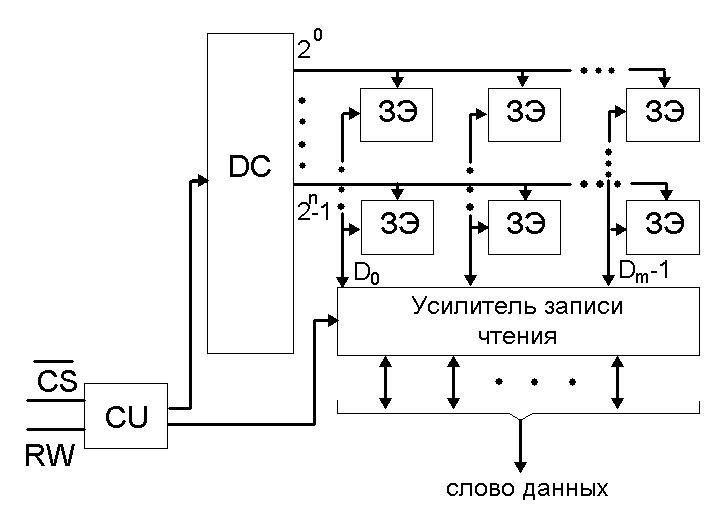

Структура 3D с однобитной (одноразрядной) организацией накопителя.

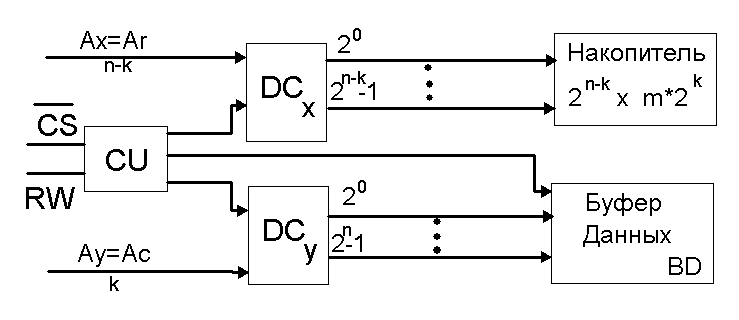

Имеются два адресных дешифратора.

A=AxAy=Axn-k-1=Ax0Ayk…Ay0

DCx – дешифратор строк

DCy – дешифратор столбцов

В результате подачи адреса запомин ячейки на вход интегральной схемы ЗУ активизируется один запоминающий элемент, находящийся на пересечении строки и столбца, номер которого содержится в поле адреса. Достоинства 3D: сокращение общего количества выходов адресного дешифратора.

Nx=2n-k Ny=2k n-k=k=k/2, n – четное

N=Nx+Ny=2n/2+2n/2=2*2n/2=2*2k/2=2n/2+1

Недостаток: усложнение схемы запомин элемента за счет двухкоординатной выборки.

На базе структуры с одноразрядной организацией строятся структуры с многоразрядной организацией накопителя. В этом случае m- одноразрядных накопителей включаются параллельно относительно адресных дешифраторов, где m- разрядность слова данных. Получается полноценная 3D структура.

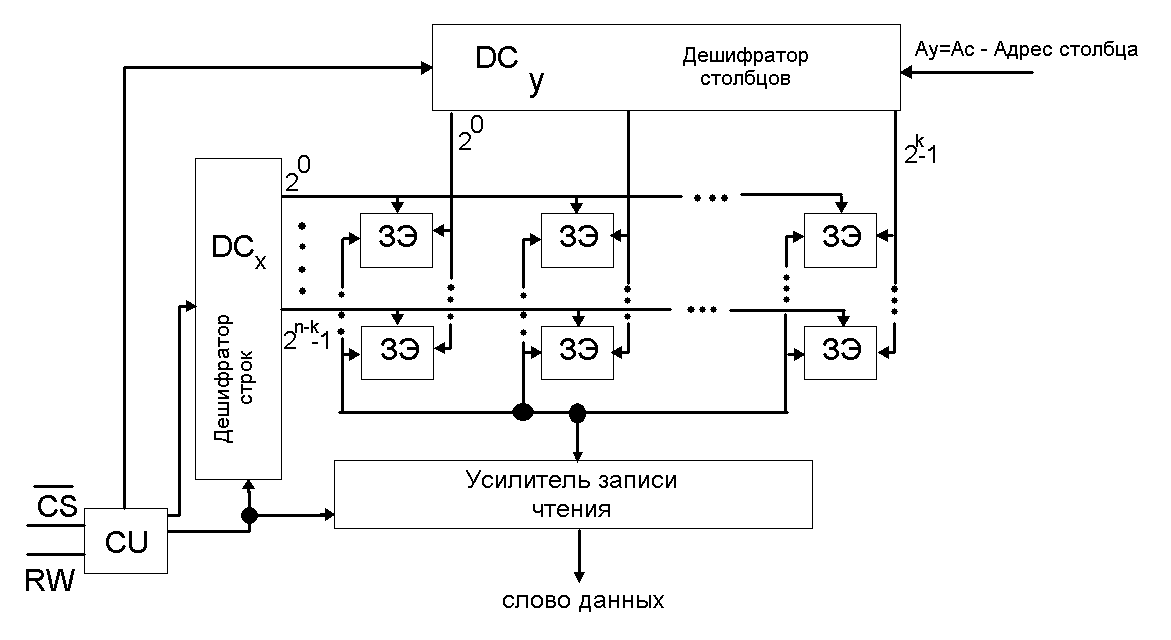

Достоинства 2D и 3D структур сочетаются в модифицированной 2D структуре 2DМ

1). Сигналом активного уровня с выхода DCx возбуждается 1 из 2n-k строк накопителя длиной m*2k, m – разрядность слова данных.

2). Сигналом активного уровня с выхода DCy из m*2k выбранных запомин элементов обращение осуществляется к одному слову из m элементов (т.е. в каждой из m групп элементов размером 2k выбирается один элемент – 1 бит слова данных).

3). В данном случае сложность схемы переносится на схему буфера данных, который должен иметь в своем составе m двунаправленных мультиплексоров с организацией 2kх1, кот. в режимах записи и чтения по коду адреса столбца формируют из длинной строки слово данных.

4

4