- •Логические операции и элементарные логические функции.

- •2. Законы отрицания

- •3. Комбинационные законы

- •3.Способы представления логических функций. Минимизация функций алгебры логики методом Вейча-Карно.

- •3. Логические элементы. Параметры логических элементов. Типы выходных каскадов.

- •4. Типовые комбинационные схемы. Назначение, принципы построения, примеры использования.

- •5.Триггеры.

- •6.Регистры. Классификация, принципы построения, выполняемые функции, примеры использования.

- •7. Счётчики: назначение, классификация, принципы построения, примеры использования

- •8. Полупроводниковая память: назначение, классификация. Принципы построения адресных зу.

- •9. Принцип работы эвм. Классификация мп. Программная модель мп Intel 8086. Сегментация памяти

- •10. Система памяти эвм. Особенности памяти типа стек. Назначение и принцип действия кэш-памяти.

- •Общие замечания

- •Целостность данных

- •11. Система команд универсального микропроцессора.

- •Команды передачи управления.

- •13.Организация взаимодействия человека оператора с вычислительной системой.

- •14. Видеосистемы пк типа ibm pc. Устройство и характеристики мониторов.

- •15. Виды обмена с внешними устройствами.

- •16.Внешний интерфейс. Примеры реализации

- •17. Обобщенная структура микропроцессорной информационной измерительно-управляющей системы(ииус). Схемы построения многоканальных измерительных систем.

- •18. Микроконтроллеры: назначение, особенности архитектуры. Типовые периферийные устройства.

- •19. Измерение временных параметров импульсно-модулированных сигналов. Формирование импульсно-модулированных сигналов управления.

4. Типовые комбинационные схемы. Назначение, принципы построения, примеры использования.

Типовые узлы ЭВМ.

Удобной мат. Моделью при решении задач анализа и синтеза любой структурной единицы ЭВМ является цифровой автомат (любое устройтсво обработки информации в цифровом виде).

ЦА без памяти.

ЦА с памятью (конечные или последовательные).

Любой ЦА является дискретным уст-вом, т.е. входные и выходные сигналы изменяются в дискретные моменты времени. Для отображения этого факта надо использовать дискретное время.

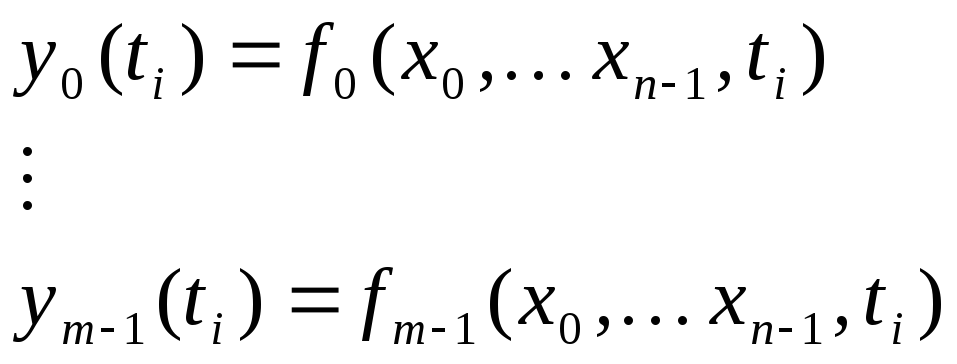

КЛА

В них выходные сигналы в некоторый момент времени ti однозначно определяются входными сигналами в совпадающие моменты времени. Для мат. Описания КЛС достаточно аппарата логики, при этом каждый выход КЛС описывается логической функцией, число аргументов которой равно числу логических форм.

, где xj

– логическая переменная, модулир. сигнал

на i-том

входе, yj

- на выходе.

Чтобы определить логическую структуру

КЛС достаточно рассмотреть каждый выход

КЛС как независимую логическую

функцию.Однако, минимизация отдельных

выходов не гарантирует минимизацию КЛС

в целом. Для поиска минимальной структуры

КЛС надо учитывать зависимость между

выходами КЛС.

, где xj

– логическая переменная, модулир. сигнал

на i-том

входе, yj

- на выходе.

Чтобы определить логическую структуру

КЛС достаточно рассмотреть каждый выход

КЛС как независимую логическую

функцию.Однако, минимизация отдельных

выходов не гарантирует минимизацию КЛС

в целом. Для поиска минимальной структуры

КЛС надо учитывать зависимость между

выходами КЛС.

Если лог. ф-ии имеют общие члены, то такие ф-ии можно упростить путем введения вспомогательных переменных.

![]() ,

,

![]() ,

,

![]() .

.

Заменим

![]() .

Быстродействие хуже, т.к. сначала

считаетсяy,

а потом все остальное. Увеличивается

число последовательно соединенных ЛЭ.

.

Быстродействие хуже, т.к. сначала

считаетсяy,

а потом все остальное. Увеличивается

число последовательно соединенных ЛЭ.

Выражение одной логической функции через другую.

Пример. КЛС имеет два выхода.

![]()

![]() ,

,

Рассмотрим S как лог. ф-ию от 4-х переменных x,y,z и p. Из 16 наборов переменных 8 старших наборов явл. запрещенными, т.е они не могут иметь место в реальном устр-ве.

Цифровой компаратор, дешифратор, мультиплексор:

К омпаратор:

сравнение кодов.

омпаратор:

сравнение кодов.

Применение: делитель с переменным коэффициентом деления.

Дешифратор: устройство преобразует входной 2-ый код в в позиционный (десятичный)

П ДС

Мультиплексор – демультиплексор(наоборот): объединяет несколько входов на один выход.

П рименение:

мультиплексированные линии адреса -

данных.

рименение:

мультиплексированные линии адреса -

данных.

Дешифратор относится к преобразователем кодов.

В зависимости от входного двоичного кода на входе дешифратора возбуждается одна и только одна из выходных цепей.

Двоичные шифраторы выполняют операцию, обратную по отношению к дешифратору. При возбуждении одного из входов шифратора на его на его выходе формируется двоичный код номер возбужденноё входной линии.

Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением управляющего слова. Коммутаторы (устройства сравнения) определяют отношение между двумя словами.

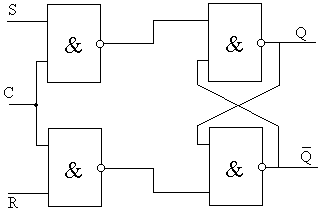

5.Триггеры.

Т

риггер

– элементарные автоматы, содержащие

собственно элемент памяти(фиксатор) и

схему управления. Фиксатор сроится на

двух инверторах, связанных друг с другом

накрест, так что выход одного соединяется

со входа другого. Если на входе инвертора

1 имеется логический 0, то он обеспечивает

на входе инвертора 2 логическую 1, то же

согласование сигналов имеет место и

для второго состояния, когда инвертор

1 находится в логической единице, а

инвертор 2 в 0.

риггер

– элементарные автоматы, содержащие

собственно элемент памяти(фиксатор) и

схему управления. Фиксатор сроится на

двух инверторах, связанных друг с другом

накрест, так что выход одного соединяется

со входа другого. Если на входе инвертора

1 имеется логический 0, то он обеспечивает

на входе инвертора 2 логическую 1, то же

согласование сигналов имеет место и

для второго состояния, когда инвертор

1 находится в логической единице, а

инвертор 2 в 0.

Такое соединение дает цепь с двумя устойчивыми состояниями.

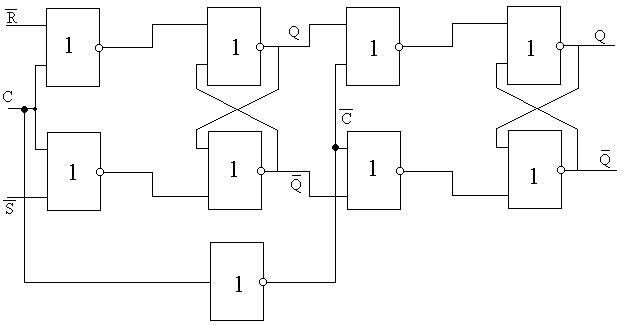

Классификация триггеров проводится по признакам логического функционирования и по способу записи информации. По логическому функционированию различают триггеры типов RS,D,T,JK и др.

Кроме того, используются комбинированные триггеры, в которых совмещается одновременно несколько типов.

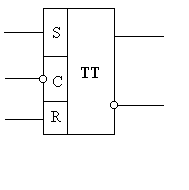

Триггеры типа RS имеют 2 входа – установки в единицу (S) и установки в 0 (R).

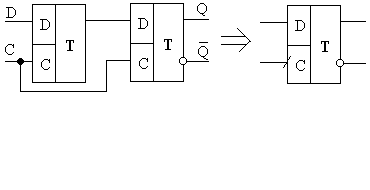

Триггеры типа D(задержка) имеет один вход. Его состояние повторяет входной сигнал, но с задержкой, определяемой тактовым сигналом.

Триггеры типа Т изменяет своё состояние каждый раз при поступлении входного сигнала. Имеет один вход и называется триггером со счётным входом или счётным триггером.

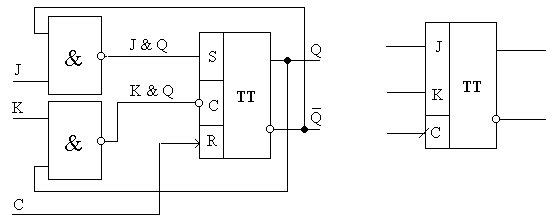

Триггер типа JK универсален, он имеет входы установки (J) и сброса (K) подобные входам триггера SR. В отличие от последнего допускает ситуацию с одновременной подачей сигналов на оба эти входа (J=K=1). В этом режиме работает как счётный триггер относительно третьего (тактового) входа.

В комбинированных триггерах совмещается несколько режимов.

По способу записи информации различают асинхронный и синхронный триггеры (не тактируемые и тактируемые)

В не тактируемых переход в новое состояние вызывается непосредственно изменением входных информационных сигналов.

В тактируемых, имеющих специальный вход, переход происходит только при подаче на этот вход тактовых сигналов.

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем и управляемые фронтов.

Динамический вход может быть прямым и инверсным. Прямое динамическое управление означает разрешение на переключении при изменении тактового сигнала с нулевого значения на единичное, инверсное – при изменении тактового сигнала с единичного значения на нулевое.

Уравнение триггера:

JK:

Qn = JQ

QK D: Qn = D

JK:

Qn = JQ

QK D: Qn = D