639_Nosov_V.I._RRL_STSI._Mnogourovnevyj_kodek_

.pdf

S(F) |

1 |

0.5

F,

0 |

|

|

|

|

|

|

|

|

0 |

FT |

2·F |

3·F |

T |

|

4·FT |

||

|

|

|

T |

|

|

|||

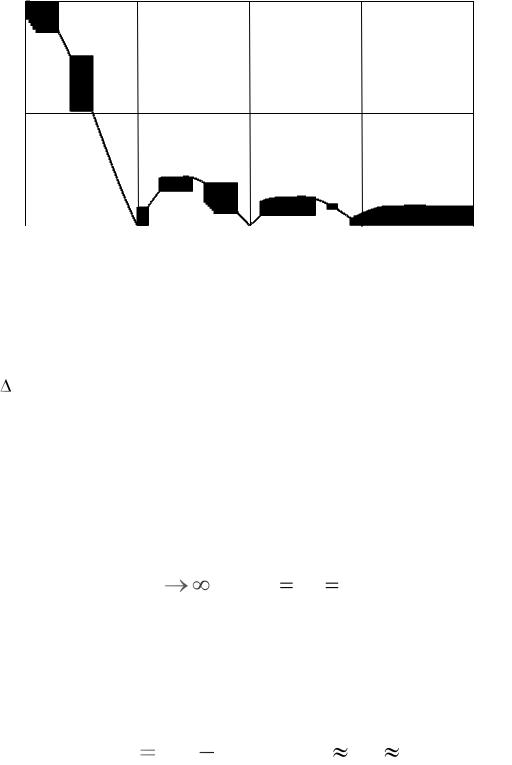

Рис. 2.10. Нормированная спектральная плотность мощности одиночного импульса

Из (2.6) следует, что для случайного цифрового потока ТЦП  расстояние между соседними спектральными составляющими стремится к нулю FДС

расстояние между соседними спектральными составляющими стремится к нулю FДС  0. Следовательно, спектр случайной импульсной последовательности, так же как и спектр одиночного импульса, является сплошным.

0. Следовательно, спектр случайной импульсной последовательности, так же как и спектр одиночного импульса, является сплошным.

Теперь рассмотрим спектральную плотность мощности цифрового сигнала с псевдослучайной последовательностью. Отметим, что термин псевдослучайная последовательность появился из следующих соображений. Известна случайная последовательность, которая имеет период следования ТСП стремящийся к бесконечности и равную вероятность появления нулей и единиц

ТСП |

, |

р0 р1 0,5. |

(2.7) |

Псевдослучайная последовательность (ПСП) имеет период повторения, определяемый разрядностью регистра сдвига генератора псевдослучайной последовательности (2.3), а вероятность появления нулей и единиц в такой последовательности примерно одинакова

ТПСП (2n |

1)T, |

р0 р1 0,5. |

(2.8) |

Как и у любой импульсной последоввательности, спектральная плотность мощности псевдослучайной последовательности является дискретной и расстояние между соседними дискретными составляющими согласно (2.6) и

(2.3)

41

FДС 1/ТПСП 1/(2n |

1)T FT /(2n |

1). |

(2.9) |

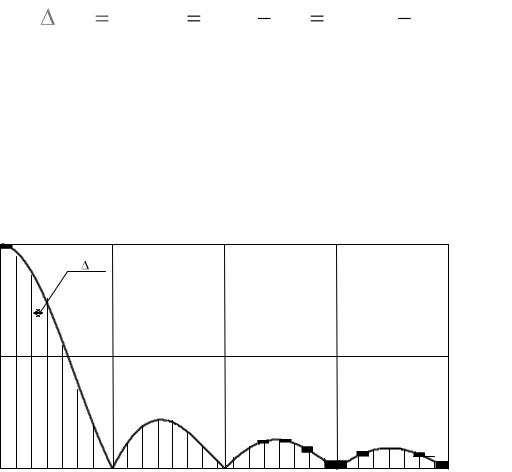

Спектральная плотность мощности псевдослучайной цифровой последовательности рисунок 2.11 будет иметь огибающую дискретных составляющих такую же как и для одиночного импульса (2.5)

Из формулы (2.9) и рисунка 2.11 следует, что в участке спектра шириной FT располагается ( 2n - 1) дискретных составляющих спектра псевдослучайной последовательности.

S(F) |

|

|

|

|

|

1 |

|

|

|

|

|

|

F |

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

|

F, |

0 0 |

FT |

2·F |

3·F |

T |

4·FT |

|

|

T |

|

||

Рис. 2.11. Нормированная спектральная плотность мощности псевдослучайной |

|||||

|

|

последовательности |

|

|

|

Если не использовать скремблер, то при длинной серии нулей на вход |

|||||

модулятора не поступает модулирующий сигнал, а при длинной серии единиц на вход модулятора поступает постоянная составляющая. В том и другом случае на выходе модулятора, а следовательно и на выходе передатчика будет немодулированная несущая, на которой сосредоточена вся мощность передатчика. Так как частотно-территориальное планирование радиосредств ведется с учетом излучения передатчиками модулированных сигналов, то данный передатчик создаст недопустимую помеху приемникам других радиосредств, работающих на этой или близкой частотах, и нарушит их нормальное функционирование. Т.е. это приводит к резкому ухудшению электромагнитной совместимости.

Использование же скремблирования цифрового сигнала позволяет исключить возможность появления длинных серий нулей и единиц, т.е. создает условия постоянного присутствия на входе модулятора модулирующего сигнала. Это позволяет в значительной степени улучшить электромагнитную совместимость радиосредств, причем улучшение электромагнитной

42

совместимости будет тем выше, чем больше период псевдослучайной последовательности.

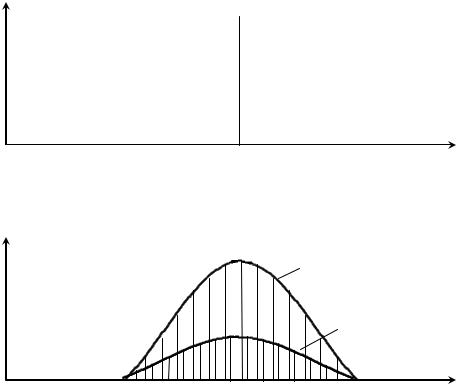

Действительно, при отсутствии модулирующего сигнала на выходе передатчика будет одна дискретная составляющая (несущая), мощность которой равна мощности передатчика рисунок 2.12. Если же используется скремблер, то появляется модулирующий сигнал, количество дискретных составляющих, в котором определяется периодом псевдослучайной последовательности, и мощность передатчика распределяется между этими дискретными составляющими пропорционально их амплитуде. В результате при фиксированной мощности передатчика, мощность приходящаяся на отдельные дискретные составляющие будет тем меньше, чем больше их количество, т.е. тем больше период псевдослучайной последовательности рисунок 2.12, где ТПСП2 > ТПСП1. Таким образом, скремблер осуществляет дисперсию мощности передатчика по спектру, а при меньшей амплитуде дискретных составляющих в спектре сигнала он оказывает меньшее влияние на приемники других радиосредств.

После скремблера проскремблированный сигнал восьмью потоками поступает на второй преобразователь скорости, в котором восемь цифровых потоков преобразуются в шесть (при 64 КАМ) и их суммарная скорость увеличивается на 10 Мбит/с.

В общем случае на выходе второго преобразователя кода необходимо получить к потоков, которые обеспечивали бы М различных состояний, где М – позиционность модуляции, реализуемая в модуляторе. Так как в цифровых потоках используется аппаратный двоичный код NRZ, то общее число

различных состояний, которые могут дать к таких потоков |

|

M 2k. |

(2.10) |

Из (2.10) следует, что при 16 КАМ необходимо четыре цифровых потока, при 32 КАМ – 5, при 64 КАМ – 6, при 128 КАМ – 7 и т.д.

Для формирования шести выходных потоков в исходных восьми потоках нумеруются все биты в блоке, причем соседние биты имеют одинаковые номера, но разный цвет таблица 1. При формировании шести потоков из одного блока входных потоков формируются два блока, причем в блоке 1 размещаются «светлые» информационные биты, а в блоке 2 – «темные» биты с теми же номерами.

Таким образом, в выходных потоках соседние биты оказываются разнесенными, в данном случае на двенадцать тактовых интервалов. Такое разнесение во времени бит цифрового сигнала называется перемежением, а расстояние между соседними битами глубиной перемежения. Данные шесть потоков являются по существу модулирующим сигналом и передаются по тракту передачи. Из за глубоких селективных замираний на пролете и из-за

43

действия импульсных помех в цифровом сигнале на приемной стороне возникают пакеты ошибок, для исправления которых требуются коды с большой избыточностью.

Р

РП

f

f0

а

Р

ТПСП1

ТПСП2

f

f0-FT |

f0 |

f0+FT |

б

Рис. 2.12 Спектры сигнала на выходе передатчика без скремблирования а и со скремблированием б

Процесс преобразования восьми потоков в шесть изображен в таблицах

2.2 и 2.3.

|

|

Нумерация блока бит входных потоков |

|

Таблица 2.2 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d8 |

|

57 |

57 |

58 |

58 |

59 |

59 |

60 |

60 |

61 |

61 |

62 |

62 |

|

63 |

63 |

64 |

64 |

65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d7 |

|

65 |

66 |

66 |

67 |

67 |

68 |

68 |

45 |

45 |

46 |

46 |

47 |

|

47 |

48 |

48 |

49 |

49 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d6 |

|

50 |

50 |

51 |

51 |

52 |

52 |

53 |

53 |

54 |

54 |

55 |

55 |

|

56 |

56 |

33 |

33 |

34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d5 |

|

34 |

35 |

35 |

36 |

36 |

37 |

37 |

38 |

38 |

39 |

39 |

40 |

|

40 |

41 |

41 |

42 |

42 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d4 |

|

43 |

43 |

44 |

44 |

21 |

21 |

22 |

22 |

23 |

23 |

24 |

24 |

|

25 |

25 |

26 |

26 |

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d3 |

|

27 |

28 |

28 |

29 |

29 |

30 |

30 |

31 |

31 |

32 |

32 |

10 |

|

10 |

11 |

11 |

12 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d2 |

|

13 |

13 |

14 |

14 |

15 |

15 |

16 |

16 |

17 |

17 |

18 |

18 |

|

19 |

19 |

20 |

20 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d1 |

|

1 |

2 |

2 |

3 |

3 |

4 |

4 |

5 |

5 |

6 |

6 |

7 |

|

7 |

8 |

8 |

9 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44

|

|

|

|

|

|

|

|

|

|

Расположение бит в выходных потоках |

|

|

|

|

|

|

Таблица 2.3 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D6' |

|

|

57 |

58 |

59 |

60 |

61 |

62 |

63 |

|

64 |

65 |

66 |

6 |

68 |

57 |

58 |

59 |

60 |

61 |

62 |

63 |

64 |

65 |

66 |

67 |

68 |

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

D5' |

|

|

45 |

46 |

47 |

48 |

49 |

50 |

51 |

|

52 |

53 |

54 |

55 |

|

5 |

45 |

46 |

47 |

48 |

49 |

50 |

51 |

52 |

53 |

54 |

55 |

56 |

45 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D4' |

|

|

33 |

34 |

35 |

36 |

37 |

38 |

39 |

|

40 |

41 |

42 |

43 |

|

4 |

33 |

34 |

35 |

36 |

37 |

38 |

39 |

40 |

41 |

42 |

43 |

44 |

33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D3' |

|

|

21 |

22 |

23 |

24 |

25 |

26 |

27 |

|

28 |

29 |

30 |

31 |

|

3 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

29 |

30 |

31 |

32 |

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D2' |

|

|

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

17 |

18 |

19 |

20 |

|

* |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

* |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

D1' |

|

|

1 |

2 |

3 |

* |

4 |

5 |

6 |

|

* |

7 |

8 |

9 |

|

* |

1 |

2 |

3 |

* |

4 |

5 |

6 |

* |

7 |

8 |

9 |

* |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок 1 |

Блок 2 |

|

45

После преобразования на приемной стороне шести потоков в восемь осуществляется и деперемежение соседних бит. При этом происходит преобразование пакетов ошибок в одиночные, которые могут исправляться корректирующими кодами с меньшей избыточностью.

Как видно из таблицы 2.3 избыточные биты добавляются только в первый и второй из шести цифровых потоков, причем в первом потоке избыточные биты вводятся после каждых трех информационных, а во втором потоке - после каждых двенадцати. При этом скорость кодирования соответственно равна

RD1 3 4, RD2 11 12. |

(2.11) |

Дополнительная скорость для избыточного кодирования, введенная во втором преобразователе скорости составляет 9,4 Мбит/с, причем в первом цифровом потоке эта скорость составляет 7,05 Мбит/с, а во втором 2,35 Мбит/с.

Востальных четырех потоках избыточных бит нет.

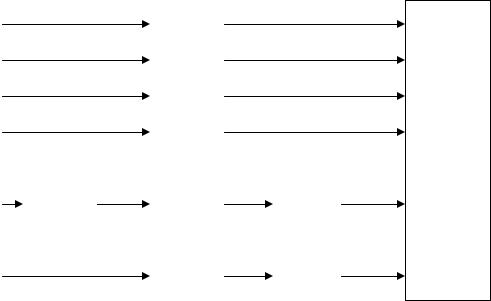

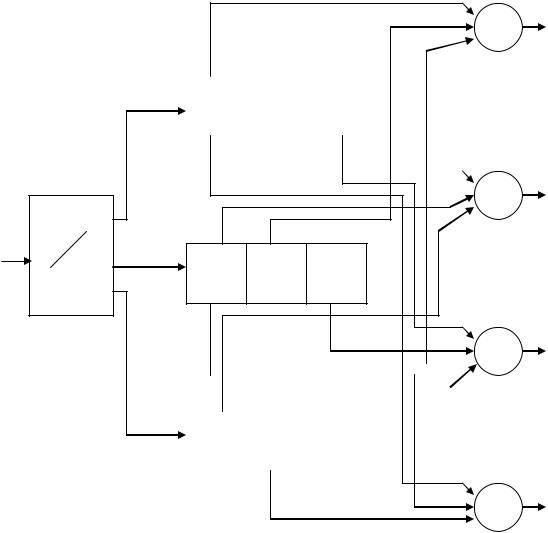

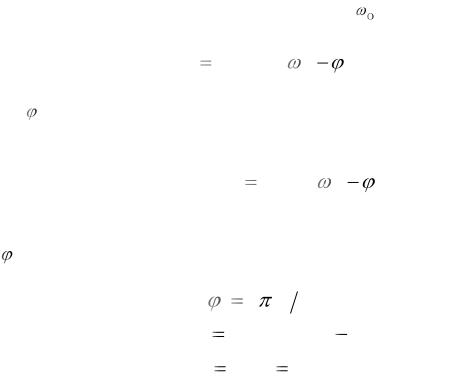

Свыхода преобразователя скорости рисунок 2.1. шесть цифровых потоков со скоростью 28,193 Мбит/с каждый поступают на блок кодирования и размещения, подробная структурная схема которого приведена на рисунке 2.13. Избыточные биты в первом потоке заполняются в кодере 1, в качестве которого используется сверточный кодер рисунок 2.14.

В этом кодере первый цифровой поток разбивается на три параллельных потока, каждый из которых подается на свой трехразрядный регистр сдвига. С выходов элементов этих регистров сдвига цифровые сигналы поступают на четыре сумматора по модулю два, на выходах которых получаются в

параллельном коде три информационных бита i1, i2, i3 и избыточный бит r. Такой сверточный код называется не систематическим, так как

информационные биты поступают на выход не непосредственно с выхода последовательно-параллельного преобразователя, а с выходов регистров сдвига. При этом выходные биты кодера зависят не только от текущих значений входных бит, но и от ряда их предыдущих значений, число которых определяется разрядностью регистров сдвига. Разрядность регистров сдвига определяет глубину кодирования сверточного кода и с ее увеличением увеличивается выигрыш от использования избыточного кодирования. Избыточное кодирование сверточным кодом со скоростью 3/4, позволяет на приемной стороне обнаруживать и исправлять ошибки в трех битовых информационных блоках.

Второй цифровой поток поступает на дифференциальный кодер (кодер относительности), с помощью которого на приемной стороне устраняется неоднозначность фазы опорного напряжения в фазовом детекторе. После дифференциального кодирования сигнал поступает на кодер 2, в котором входной цифровой поток разбивается на одиннадцать параллельных потоков

46

D6 |

|

|

|

|

|

d6 |

|

|

|

|

|

|

|

D5 |

|

|

Задерж |

|

|

d5 |

|

|

|

|

|

|

|

D4 |

|

|

ка |

|

|

d4 |

|

|

|

|

|

||

D3 |

|

|

|

|

|

d3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Диф. |

|

Кодер 2 |

|

P/S |

d2 |

D2 |

кодер |

|

|

|

преобр |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

Кодер 1 |

|

P/S |

d1 |

|

|

|

|

|

преобр |

|

|

|

|

|

|

|

|

P1

P1

Размеще  P2 ние

P2 ние  P3

P3

Q1

Q1

Q2

Q2

Q3

Q3

Рис. 2.13 Структурная схема кодера и размещения

.

Информационные биты этих одиннадцати потоков суммируются по модулю два и результат суммирования помещается в избыточный двенадцатый бит. Таким образом в этом кодере осуществляется проверка блока из одиннадцати информационных бит на четность, что позволяет на приемном конце обнаружить наличие ошибки в этом блоке.

С выходов кодеров 1 и 2 сигналы поступают на преобразователи параллельного кода в последовательный (p/s – parallel / serial). Поскольку цифровые потоки с третьего по шестой не содержат избыточных бит и не обрабатываются в кодерах, для сохранения синхронности всех шести потоков на входе схемы размещения, они проходят через линию задержки.

В устройстве размещения шесть входных потоков, которые имеют 64 различных состояния, размещаются на фазово-амплитудной плоскости модулятора, т.е. на синфазной Р и квадратурной Q осях. Количество цифровых потоков для каждой из осей определяет количество уровней сигналов, т.е. определяет многоуровневый сигнал, откуда и произошло название многоуровневый кодер. Процедура размещения шести цифровых потоков на фазово-амплитудной плоскости модулятора будет рассмотрена в следующем параграфе.

47

+

S1 |

S2 |

S3 |

|

|

|

|

|

|

|

|

|

|

|

|

+

Посл.

D1

Пар. |

S1 |

S2 |

S3 |

|

+

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

S2 |

S3 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

+

i1

i2

i3

r

Рис. 2.14 Сверточный кодер

48

Контрольные вопросы

1.Поясните принцип формирования дополнительного заголовка радиоцикла.

2.Поясните для чего используется дополнительный заголовок радиоцикла.

3.Поясните принцип преобразования скорости цифрового потока.

4.Поясните назначение циклового синхросигнала дополнительного заголовка радиоцикла.

5.Поясните назначение и принцип работы скремблера.

6.Поясните причину улучшения электромагнитной совместимости при использовании скремблера.

7.Поясните назначение перемежения символов цифровых потоков.

8.Поясните принцип работы сверточного кодера.

Список литературы

1.Носов В.И. Основы построения радиорелейных линий синхронной цифровой иерархии. Учебное пособие. УМО по специальности связь. – Новосибирск.: СибГУТИ, 1999. – 98 с.

2.SDH Digital Microwave Radio System. System Handbook, vol. 1,2. – NEC, Japan. 1995.

3.SDH Digital Microwave Radio System. Instruction Manual, vol. 1,2,3,4,5. – NEC, Japan. 1995.

49

3 МОДУЛЯТОР КАМ

С выхода многоуровневого кодера Кр цифровых потоков для синфазной составляющей и КQ цифровых потоков для квадратурной составляющей суммарной скоростью 169,158 Мбит/с поступают на вход квадратурного амплитудного модулятора.

Необходимость использования многопозиционной квадратурной (амплитудно-фазовой) модуляции вызвана следующими причинами. С одной стороны, согласно частотным планам для радиорелейных линий, полоса частот отводимая для одного ствола составляет, в диапазонах частот 2,4,5,6,8,11 ГГц, 28 или 40 МГц. С другой стороны через ствол с такой шириной полосы частот необходимо передать сигнал, модулированный высокоскоростным цифровым потоком с тактовой частотой 155,520 МГц (СТМ – 1) или же 51,84МГц (СТМ –

0).

3.1 Многопозиционная модуляция

Колебания модулированной несущей с частотой

s(t) S(t) cos 0t (t) , (3.1)

где S(t), (t) - определяют закон модуляции амплитуды и фазы несущей. Сигнал М позиционной фазовой модуляции (М-ФМ) на интервале одного

символа |

|

|

si (t) S0 cos( 0t |

i ). |

(3.2) |

Соотношения для кратности модуляции М, дискретных значений фазы сигнала i.

i 2 ai M ; |

(3.3) |

аi |

{0,1,2,...,М 1}; |

(3.4) |

М |

2к , к 1,2,3,... |

(3.5) |

Из (3.4) и (3.5) следует, что каждый М-ичный символ аi |

соответствует |

|

набору из к

50