639_Nosov_V.I._RRL_STSI._Mnogourovnevyj_kodek_

.pdf

четырьмя служебными двоичными цифровыми потоками Р4Р5Р6Р7 |

по |

синфазному и Q4Q5Q6Q7 по квадратурному каналам. |

|

Операция обратная размещению (mapping), проведенному |

в |

многоуровневом кодере при 64-КАМ таблица 3.4, деразмещение (demapping) осуществляется на входе устройства обнаружения и исправления ошибок рисунок 7.2. В устройстве demapping шесть входных информационных потоков Р1Р2Р3Q1Q2Q3 преобразуются в шесть потоков d6d5d4d3d2d1 согласно кодовой таблице 3.4 для 64-КАМ.

В полученных шести потоках d6d5d4d3d2d1 избыточные биты есть в первом d1 цифровом потоке со скоростью R=3/4 и во втором d2 цифровом потоке со скоростью R=11/12, таблица 2.3. Эти избыточные биты были заполнены символами «0» или «1» в сверточном кодере для потока d1 и в кодере проверки на четность для потока d2 в многоуровневом кодере на передающей стороне рисунок 2.13.

Поток d1 с выхода устройства demapping поступает на декодер Витерби, который позволяет обнаружить и исправить одиночные ошибки в информационных символах закодированных сверточным кодом.

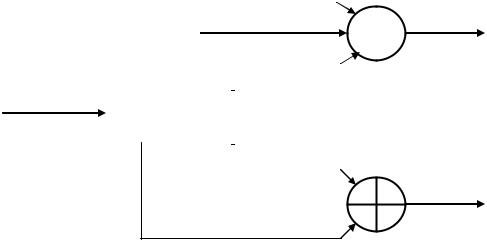

При сверточном кодировании преобразование информационных последовательностей в кодовые происходит непрерывно. Кодер двоичного сверточного кода рисунок 2.14 содержит регистры сдвига на m разрядов (в данном случае m=3) и сумматоры по модулю 2 для образования кодовых символов i1i2i3r. Входы сумматоров по модулю 2 соединены с определенными разрядами регистров сдвига.

В общем случае скорость кода R=к/n, где к - число информационных символов, поступающих за один такт на вход кодера, n - число соответствующих им символов на выходе кодера. В примере на рисунке 2.14 R=3/4. В дальнейшем работу сверточного кодера и декодера Витерби рассмотрим на наиболее простом примере для скорости R=1/2 рисунок 7.3а.

|

|

|

|

|

|

|

|

|

|

|

|

|

V1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(i) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Вход |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

S2 |

S3 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V2

(r)

Рисунок 7.3а Структурная схема кодера для R=1/2

141

Сверточный кодер как конечный автомат |

с памятью описывают |

диаграммой состояний. |

|

S1S2 00,01,10,11 |

(7.1) |

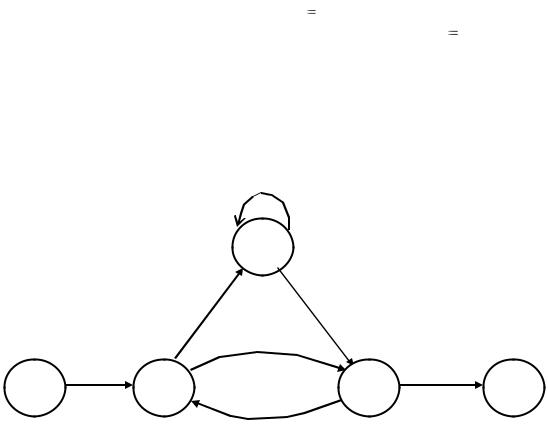

Диаграмма состояний представляет собой направленный граф, число вершин которого равно числу состояний (7.1), а ребра графа описывают все возможные переходы из одного состояния в другое, а также символы выходов кодера, сопровождающие эти переходы. Пример диаграммы показан на рисунке 7.3. В кружках, соответствующих вершинам графа, указаны состояния кодера. Диаграмма соответствует графу с направленными ребрами (направление перехода указано стрелками) и петлями, когда в результате перехода кодер остается в том же состоянии. Возле ребер и петель показаны символы на выходе кодера V1V2, соответствующие каждому переходу таблица 7.1

|

00 |

|

00 |

11 |

11 |

|

00 |

10 |

01 |

|

10 |

01 |

01 |

|

|

|

11 |

|

10 |

Рисунок 7.3 Диаграммы состояний кодера

Диаграмма построена следующим образом. В начальный момент времени все ячейки регистра кодера устанавливаются в нулевое состояние S1S2S3=000.

Состояния кодера |

|

|

|

|

Таблица 7.1 |

|||

№ |

Вход |

|

S1 |

S2 |

S3 |

V1 |

|

V2 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

2 |

0 |

|

0 |

1 |

0 |

1 |

|

0 |

3 |

1 |

|

1 |

0 |

1 |

0 |

|

0 |

4 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

|

|

|

|

142 |

|

|

|

|

При поступлении на вход символа U=1 кодер переходит в состояние S1S2= 10 и на выходе кодера будут сформированы символы V1V2=11. На диаграмме рисунок 7.3 этот переход изображен ребром 11 из вершины 00 в вершину 10. Далее при поступлении символа U=0 кодер переходит из состояния S1S2=10 в состояние S1S2=01 и на выходе кодера будут сформированы символы V1V2=10. На диаграмме этот переход обозначен ребром 10 из вершины 10 в вершину 01. Если затем на вход поступит символ U=1, то кодер перейдет из состояния S1S2=01 в состояние S1S2=10 и на выходе кодера будут сформированы символы V1V2=00. На диаграмме это переход обозначен ребром 00 из вершины 01 в вершину 10. Построение диаграммы заканчивается, когда получены все возможные переходы (ребра) из каждого из четырех состояний (вершин) во все остальные. Ребро в виде петли появляется в том случае, если после прихода очередного символа состояние кодера (S1S2) не изменяется.

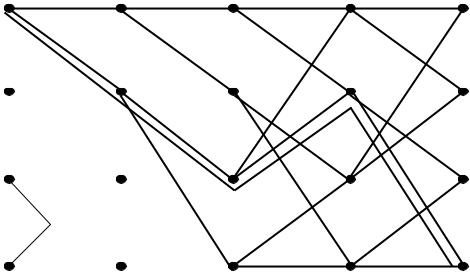

Для расчетов помехоустойчивости используют модифицированную диаграмму рисунок 7.4, которую получают расчленяя (разрывая) исходную диаграмму рисунок 7.3 в состоянии 00. Переходы маркируют переменными Dk N е , где к – число единиц в наборе выходных символов V1V2, соответствующих данному переходу; 0 , если переход соотвествует поступлению на вход информационного символа U=0, и 1 , если переход соответствует поступлению U=1. Например, переходу из состояния S1S2=00 в состояние S1S2=10 соответствует набор символов V1V2=11. Этот переход на модифицированной диаграмме обозначают как D2N. В результате модифицированная диаграмма состояний содержит 7 ребер и петель, которые соединяют 5 вершин графа, поэтому такой код обозначают (7,5).

|

|

|

DN |

|

|

|

|

|

11 |

|

|

|

|

DN |

D |

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

D2N |

|

|

D |

2 |

00 |

10 |

|

01 |

00 |

|

|

|

N

Рисунок 7.4 Модифицированные диаграммы состояний кодера

143

Из диаграммы состояний рисунок 7.4 следует, что данный сверточный кодер осуществляет преобразование входного цифрового потока в следующем виде

Взаимосвязь входного и выходного сигналов кодера |

Таблица 7.2 |

||

вход кодера |

выход кодера |

|

|

1011… |

11100001… |

|

|

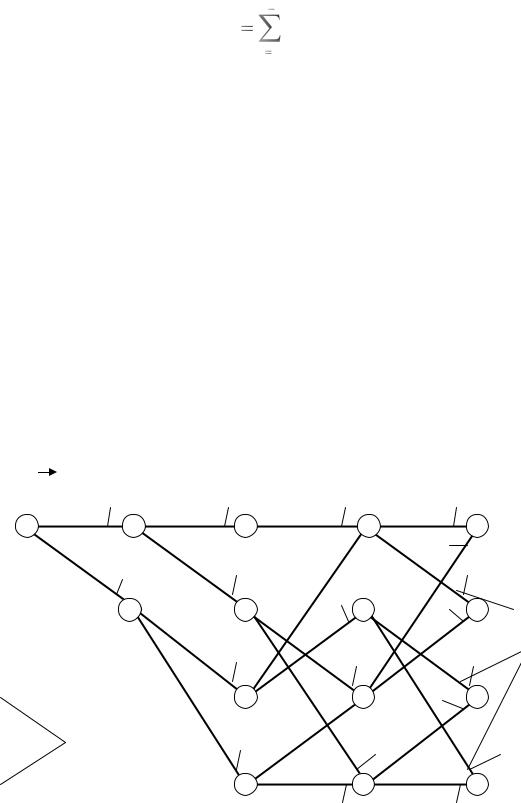

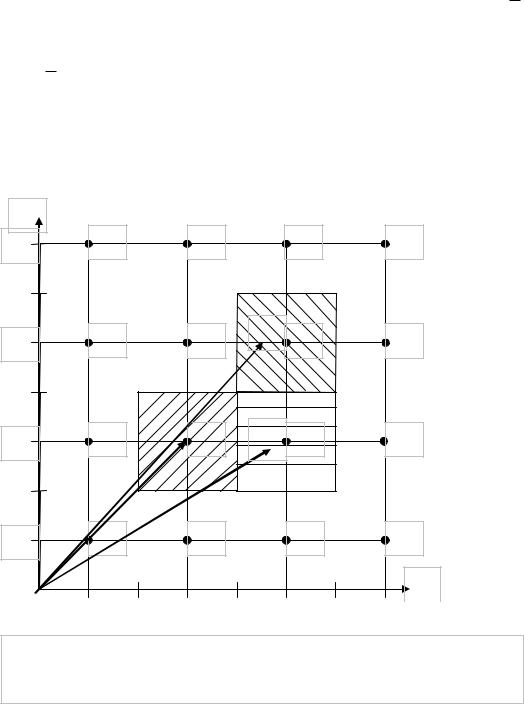

Если осуществить развертку диаграммы состояний рисунок 7.4 во времени, то получится решетчатая диаграмма сверточного кода рисунок 7.5. На решетчатой диаграмме состояния кодера показаны узлами, а переходы между состояниями соединяющими их линиями (ветвями). После каждого перехода из одного состояния в другое происходит смещение на один шаг вправо. Решетчатая диаграмма представляет все разрешенные пути, по которым может продвигаться кодер при кодировании. Штриховой линией на рисунке 7.5 показан путь по решетке 11100001…, соответствующий поступлению на вход кодера двоичной последовательности 1011…таблица 7.2.

00 |

00 |

00 |

|

00 |

|

00 |

|

|

|

|

|

11 |

11 |

11 |

|

11 |

|

|

|

|

|||

|

|

|

|

|

|

10 |

|

11 |

|

11 |

|

|

|

|

|

||

|

|

00 |

|

00 |

|

|

10 |

|

|

|

|

|

|

10 |

|

|

11 |

01 |

|

|

|

|

|

|

01 |

|

|

|

|

Состояния |

|

01 |

01 |

01 |

01 |

|

|

||||

11 |

|

10 |

|

10 |

|

|

|

|

|

|

Рисунок 7.5 Решетчатая диаграмма кода

Наиболее распространенным алгоритмом декодирования сверточных кодов является алгоритм максимального правдоподобия, предложенный А.Витерби. При декодировании по критерию максимального правдоподобия выбирают такую последовательность сигналов и однозначно связанную с ней последовательность ветвей, которая обеспечивает минимум суммы метрики

144

декодированного пути МП. Метрика пути содержит в качестве слагаемых метрики ветвей

L 1 |

|

МП МВi |

(7.2) |

t 0 |

|

В канале с гауссовским шумом метрика ветви пропорциональна квадрату Евклидова расстояния между вектором принимаемой суммы сигнала и помехи и вектором сигнала, соответствующего ветви кода. В дискретном канале для оценки расстояний используют метрику Хэмминга.

Периодическая структура решетчатой диаграммы существенно упрощает сравнение и выбор путей с минимальной суммой метрик ветвей (7.2). Пути с наименьшей метрикой называются выжившими. В соответствии с алгоритмом Витерби сравнение и отбрасывание отрезков путей производится периодически на каждом шаге декодирования.

Рассмотрим декодирование кода (7,5) рисунок 7.4, символы которого таблица 7.2 передаются по дискретному каналу. В этом случае метрика ветви МВ равна расстоянию Хэмминга между набором входных символов Z1Z2 на входе декодера и набором символов V1V2, соответствующих данной ветви на решетчатой диаграмме.

На рисунке 7.6 показано развитие процесса декодирования символов кода (7,5). На вход декодера поступают пары символов из канала Z1Z2=11100001…

Вх. сигнал |

11 |

10 |

00 |

|

2 |

1 |

0 |

|

00 |

00 |

00 |

00 |

0 |

2 |

3 |

2 |

2

11 |

0 |

11 |

1 |

|

|||

|

|

|

11

0

10 |

0 |

3 |

0 |

00

10 |

0 |

|

1 |

|

10 |

||

|

|

||

|

|

|

01 |

0 |

3 |

|

01 |

|

01 |

|

|

|

|

1 |

|

|

00 |

|

3 |

|

|

|

|

|

|

1 |

|

|

11 |

|

1 |

|

|

|

|

|

11 |

1 |

3 |

Выжив |

|

|||

|

шие |

||

00 |

|

||

|

пути |

||

|

|

|

|

|

11 |

2 |

|

|

|

|

|

|

2 |

2 |

|

|

|

|

|

Состояния |

2 |

11 |

2 |

01 |

01 |

1 |

01 |

01 |

1 |

|

|||||

|

|

|

|

10 |

3 |

10 |

1 |

|

|

||

|

1 |

|

1 |

Рисунок 7.6 Процесс декодирования кода (7,5) по алгоритму Витерби

145

Цифрами около ветвей обозначены метрики ветвей, цифры в кружках обозначают метрики состояний. В начальный момент времени полагаем, что декодер находится в состоянии 00 и исходная метрика состояния МС(00)=0. Если из канала поступили символы Z1Z2=11, то метрики двух ветвей, выходящих из этого состояния МВ(00)=2, так как метрика Хэмминга для этого пути равна:

z1z2 |

11 |

|

v1v2 |

00 |

(7.3) |

|

|

|

d |

11 2 |

|

А метрика ветви МВ(11)=0. Это отмечено на первом шаге декодирования.

Так как других ветвей из состояния 00 нет (смотри рисунок 7.6), то метрики этих состояний принимаются равными метрикам входящих ветвей МС(00)=2, МС(10)=0. Аналогично и на следующем шаге, когда из канала поступают символы Z1Z2=10. При этом метрика ветви МВ(00)=1, МВ(11)=1,

МВ(10)=0, МВ(01)=2.

Метрики состояний на этом шаге определяются теперь как суммы метрик входящих ветвей с метриками предыдущих состояний МС(00)=2+1=3,

МС(10)=2+1=3, МС(01)=0+0=0, МС(11)=0+2=2. На этом развитие решетчатой диаграммы заканчивается, так как охвачены все четыре возможные состояния кодера S1S2=00,01,10,11.

Далее алгоритм периодически повторяет один основной шаг. В момент времени t в памяти декодера хранятся метрики состояний, вычисленных на предыдущем шаге: MC(00)i 1, MC(01)i 1, MC(10)i 1, MC(11)i 1 . По принятым

канальным символам Z1Z2 производится вычисление метрик ветвей МВ(00)(i),

МВ(11)(i), МВ(01)(i), МВ(10)(i) и формирование четырех новых метрик состояний МС(00)(i), МС(01)(i), МС(10)(i) , МС(11)(i) по следующему правилу.

К каждому новому состоянию ведет два пути. Например, к состоянию 00 ведут пути из состояний 00 и 01 (рисунок 7.6). Декодер вычисляет метрики путей как суммы метрик предыдущих состояний и метрик входящих ветвей

MC(00)(i )

MC(01)(i )

MC(10)(i )

MП(00)(i ) MП(00)(i )

MП(01)(i ) MП(01)(i )

MП(10)(i ) MП(10)(i )

MC(00)(i 1) |

MВ(00)(i ) |

MC(01)(i 1) |

MВ(11)(i ) , |

MC(10)(i 1) |

MВ(10)(i ) |

MC(11)(i 1) |

MВ(01)(i ) , |

MC(00)(i 1) |

MВ(11)(i) |

MC(01)(i 1) |

MВ(00)(i ) , |

146

MC(11)(i ) |

MП(11)(i ) |

MC(10)(i 1) |

MВ(01)(i ) |

. |

(7.3) |

|

MП(11)(i ) |

MC(11)(i 1) |

MВ(10)(i ) |

||||

|

|

|

Далее производят попарное сравнение метрик путей, входящих в каждое состояние (пары показаны в (7.3) фигурными скобками). В результате сравнения выбирают меньшую метрику и ее считают метрикой данного состояния для последующего шага декодирования. Путь, входящий в данное состояние с меньшей метрикой, считают выжившим. На рисунке 7.6 отрезки выживших путей показаны сплошными линиями. Пути, входящие в состояние с большими метриками, считают оборванными. Они показаны на решетчатой диаграмме штриховыми линиями.

Таким образом, декодер прослеживает по кодовой решетке путь, имеющий минимальное расстояние от пути, который генерирует кодер. Так в рассматриваемом примере выжившим путем будет считаться путь с минимальной метрикой, который принимается за путь кодера и выдает на выходе декодера двоичную последовательность 1011, т.е. ту, которая была на входе сверточного кодера.

При наличии одиночных ошибок декодер находит правильный путь и таким образом производит исправление ошибок, возникших в канале в последовательности Z1Z2. При этом кодер определяет местоположение ошибочного символа во входном цифровом потоке.

Если же кодер не находит правильный путь, то на его выходе возникает пакет ошибок.

Цифровой поток d2 рисунок 7.2 с выхода устройства demapping через устройство задержки на время обработки сигнала в декодере Витерби потока d1 поступает на декодер проверки на четность. В этом декодере последовательный блок из двенадцати символов преобразуется в параллельный и все 12 символов подаются на сумматор по модулю два. Если на выходе сумматора получится ноль, то количество единиц в блоке четное и ошибки в тракте передачи в этом блоке не произошло. Если же на выходе сумматора получится единица, т.е. число единиц в блоке нечетное, то фиксируется наличие ошибки символа в одном из двенадцати символов.

Из рисунка 7.2 следует, что результат декодирования потока d1 в декодере Витерби используется в декодере четности потока d2 и при принятии решения по потокам d3-d6. Результат декодирования потока d2 в декодере четности так же используется при принятии решения по потокам d3-d6. Кроме того, при принятии решения в потоках d3-d6 используются четыре дополнительных потока Р4-Р7 по синфазному и Q4-Q7 по квадратурному каналам. Эти потоки несут информацию о знаке отклонения принимаемого уровня от номинального значения перед принятием решения о принятом уровне на выходе адаптивного транверсального эквалайзера.

Рассмотрим процедуру исправления ошибок в потоках d2-d6. Из кодовой таблицы для 64 КАМ и рисунка 7.7 следует, что ошибка при приеме сигнальной точки под номером 19 произойдет, если под воздействием шумов, помех и

147

искажений она переместится за пределы квадрата со стороной d, построенного вокруг этой точки.

Если эта сигнальная точка будет смещена на расстояние меньшее

2d , то будет зафиксирована одна из соседних сигнальных точек под номерами 11,18,20 или 27. Если же эта сигнальная точка будет смещена на расстояние

2d , то будет зафиксирована одна из соседних сигнальных точек под номерами 11,18,20 или 27. Если же эта сигнальная точка будет смещена на расстояние

больше, чем

2d по одной из диагоналей, то будет зафиксирована одна из сигнальных точек, расположенных по диагонали от рассматриваемой сигнальной точки 19-точки 10,12, 26 или 28.

2d по одной из диагоналей, то будет зафиксирована одна из сигнальных точек, расположенных по диагонали от рассматриваемой сигнальной точки 19-точки 10,12, 26 или 28.

Q

7L |

25 |

17 |

9 |

1 |

|

|

|

|

5L |

26 |

18 |

б |

10 |

2 |

|

|||||

|

|

|

|

|

3L |

27 |

19 |

а |

11 |

3 |

|

|||||

|

|

|

|

|

|

1L |

28 |

20 |

|

12 |

4 |

|

|

|

|

|

P

|

|

|

|

|

|

|

|

|

1L |

|

3L |

|

5L |

|

7L |

|

|

|

|

|

|

|

|

|

|

|

Рисунок 7.7 Возникновение ошибки в потоке d1 а и в потоке d2 б при приеме сигнальной точки 19

Входные цифровые информационные потоки многоуровневого кодера Р1Р3 и Q1-Q3 по синфазному и квадратурному каналам, соответственно, и выходные потоки d1-d6 устройства demapping, соответствующие рассматриваемым сигнальным точкам на фазово-амплитудной плоскости рисунок 7.7, приведены в таблице 7.3.

148

|

|

|

Цифровые потоки для сигнальных точек |

|

Таблица 7.3 |

||||||||

|

Р1 |

Р2 |

Р3 |

Q1 |

Q2 |

Q3 |

d6 |

d5 |

d4 |

d3 |

d2 |

d1 |

|

19 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

11 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

27 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

18 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

20 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

10 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

12 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

26 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

28 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

Как следует из таблицы 7.3 принятое в данной радиорелейной системе избыточное кодирование позволяет исправлять только наиболее вероятные ошибки, соответствующие приему вместо переданной сигнальной точки, в данном примере под номером 19, одной из соседних точек под номерами 11,18, 20 и 27.

Это связано с тем, что при приеме этих сигнальных точек происходит ошибка в первом потоке d1, которая благодаря наличию в нем избыточного кодирования со скоростью R=3/4, может быть обнаружена и исправлена. Известно, что исправление ошибки производится инвертированием информационного бита, в котором произошла ошибка. Следовательно, для того, чтобы исправить ошибку необходимо определить ее местоположение в цифровом потоке.

Из таблицы 7.3 следует также, что при принятом способе избыточного кодирования ошибки, соответствующие приему вместо переданной сигнальной точки, в данном примере под номером 19, одной из ближайших точек по диагонали под номерами 10,12,26 или 28, не могут быть исправлены. Так как в этих случаях нет ошибки в первом цифровом потоке d1 и местоположение ошибки не может быть обнаружено.

Итак, рассмотрим последовательность исправления ошибок в потоках d2d6 при приеме вместо переданной сигнальной точки 19 одной из соседних точек 11,18,20 или 27. Предположим, что вместо 19 сигнальной точки принята сигнальная точка под номером 18. Эта точка соответствует уровням +5L по синфазному и +3L по квадратурному каналам. Перед принятием решения по принятому уровню на выходе адаптивного трансверсального эквалайзера с большой вероятностью по синфазному каналу было занижение уровня +5L. Эта информация передается в многоуровневый декодер в потоках Р4-Р7.

Декодер Витерби в потоке d1 определяет ошибку и ее местоположение и исправляет ее. В декодере четности также обнаруживается ошибка в блоке из одиннадцати информационных символов в потоке d2, но не определяется ее местоположение. Согласно таблице 2.3 ошибочным символом в потоке d2 с большой вероятностью будет символ, расположенный над ошибочным

149

символом в потоке d1, так как блок из шести символов расположенных в столбце таблицы соответствует одной сигнальной точке.

Всоответствии с рисунком 7.1 происходит исправление ошибочного символа в потоке d2. Если декодер Витерби в потоке d1 и декодер четности в потоке d2 обнаруживают ошибки, то с большой вероятностью можно утверждать, что произошла ошибка при приеме сигнальной точки. В решающем устройстве для потоков d3-d6 с помощью потоков Р4-Р7 в данной ситуации принимается решение, что вместо сигнальной точки под номером 18 нужно зафиксировать сигнальную точку под номером 19. В результате такого решения в потоках d6d5d4d3 кодовая комбинация 0001, соответствующая сигнальной точке 18, заменяется на кодовую комбинацию 0011, соответствующую точке 19.

Аналогичные действия производятся при приеме сигнальной точки под номером 20 и в результате решения в потоках d6d5d4d3 кодовая комбинация 1111, соответствующая сигнальной точке 20, заменяется на кодовую комбинацию 0011, соответствующую сигнальной точке 19.

Теперь предположим, что вместо 19 сигнальной точки принята сигнальная точка под номером 11. Эта точка соответствует уровням +3L по синфазному и +5L по квадратурному каналам. Перед принятием решения по принятому уровню на выходе адаптивного трансверсального эквалайзера с большой вероятностью по квадратурному каналу было занижение уровня +5L. Эта информация передается в многоуровневый декодер в потоках Q4-Q7.

Декодер Витерби в потоке d1 определяет ошибку, ее местоположение и исправляет ее. При этом в декодере четности не обнаруживается ошибка в блоке из одиннадцати информационных символов в потоке d2. Этот факт указывает на то, что смещение принимаемой сигнальной точки произошло в одну из соседних точек по квадратурной оси.

Вэтом случае в потоке d2 не осуществляется исправление символа и информация об этом передается в решающее устройство для потоков d3-d6. В этом решающем устройстве с помощью потоков Q4-Q7 в данной ситуации принимается решение, что вместо сигнальной точки под номером 11 нужно зафиксировать сигнальную точку под номером 19. В результате такого решения

впотоках d6d5d4d3 кодовая комбинация 0111, соответствующая сигнальной точке 11, заменяется на кодовую комбинацию 0011, соответствующую точке

19.

Аналогичные действия производятся при приеме сигнальной точки, под номером 27 и в результате решения в потоках d6d5d4d3 кодовая комбинация 0010, соответствующая сигнальной точке 27, заменяется на кодовую комбинацию 0011, соответствующую точке 19.

Таким образом, реализованный в рассматриваемой аппаратуре кодем (кодер и модулятор), в котором избыточное кодирование введено с учетом расположения сигнальных точек на фазово-амплитудной плоскости

модулятора, позволяет при малой избыточности кода 10Мбит/с/ 165Мбит/с 6% получить высокую исправляющую способность. Так, если без введения

150