639_Nosov_V.I._RRL_STSI._Mnogourovnevyj_kodek_

.pdf

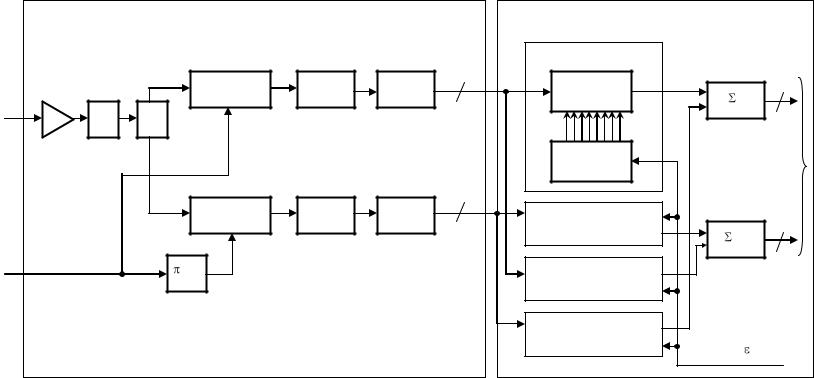

Несинфазность сигналов промежуточной частоты и цифровых сигналов на выходах демодуляторов обусловлена тем, что устройства обработки основного и кросс поляризационного сигналов разнесены территориально.

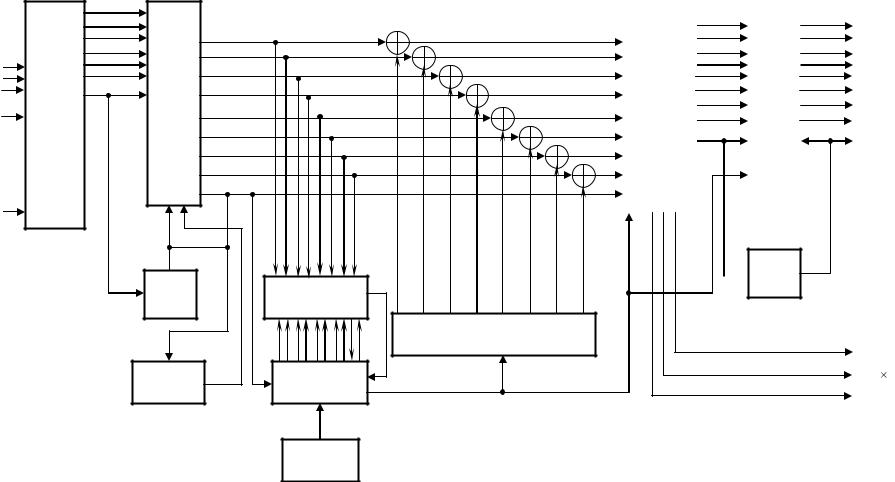

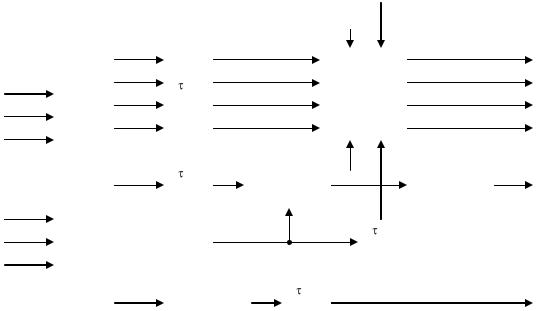

Демодулятор кросс поляризационного сигнала ХДЕМ имеет точно такую же структурную схему, что и основной демодулятор КАМ ДЕМ рисунок 6.9. Единственным отличием ХДЕМ от КАМ ДЕМ является то, что опорное напряжение на ХДЕМ подается от основного КАМ демодулятора.

Подавитель кросс поляризационных помех ХРIC имеет точно такую же схему как и адаптивный трансверсальный эквалайзер. Отличие ХРIC от АТЭ в том, что сигналы ошибки  на входы генераторов управляющих сигналов трансверсальных эквалайзеров ХРIC подаются от основного АТЭ рисунок 6.9.

на входы генераторов управляющих сигналов трансверсальных эквалайзеров ХРIC подаются от основного АТЭ рисунок 6.9.

|

|

КАМ |

|

FПЧ |

|

АТЭ |

|

|

|

|

|

|

ДЕМ |

|

|

|

|

|

|

От приемника основной |

|||

|

|

|

|||

|

|

|

поляризации |

||

- i |

|

UОП |

|||

|

|

|

|

||

|

|

|

|

|

|

ХPIC |

|

ХКАМ |

|

FПЧ |

|

|

ДЕМ |

|

|

|

|

|

От приемника |

||||

|

|

|

|||

|

|

|

кроссполяризационного |

||

|

|

|

|||

|

|

|

|

сигнала |

|

Рисунок 6.8 Структурная схема взаимодействия основного и кроссполяризационного сигналов.

Следующим отличием является то, что во всех 32 трансверсальных эквалайзерах ХРIC на сумматоры 1 не подаются символы So . В этих трансверсальных эквалайзерах так же проверяется могли ли символы кросс поляризационного сигнала привести к появлению межсимвольной помехи. После сумматора 1 в синфазном канале ХРIC получается величина кросс поляризационной межсимвольной помехи для синфазного канала основной поляризации. Эта межсимвольная помеха с инверсией подается на сумматор 3 рисунок 6.7, где и компенсируется.

Таким образом, в сумматорах 1, 2, 3 рисунок 6.7 осуществляется компенсация всех четырех видов межсимвольных помех, после чего в решающем устройстве РУ принимается решение о принятом уровне.

131

|

|

X ДEM |

|

XPIC |

|

|

|

|

вход |

|

|

|

|

|

|

8 |

Канал Р |

|

|

|

|

|

|

УПЧ |

ФДР |

УПТ |

АЦП |

Фильтр |

|

|

|

|

|

|

|

Вход ПЧ |

Р |

|

|

|

|

ПФ |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

Генератор |

к АТЭ |

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

Канал Q |

|

ФДQ |

УПТ |

АЦП |

Фильтр |

|

|

|

|

|

|

|

Вход UОП от |

/2 |

|

|

|

8 |

КAM ДEM |

|

|

Фильтр |

|

|

|

|

|

|

||

|

|

|

|

Фильтр |

|

|

|

|

|

|

от АТЭ |

Рисунок 6.9 Структурная схема кроссполяризационного демодулятора и подавителя |

|

||||

кроссполяризационных межсимвольных помех. |

|

|

|

||

132

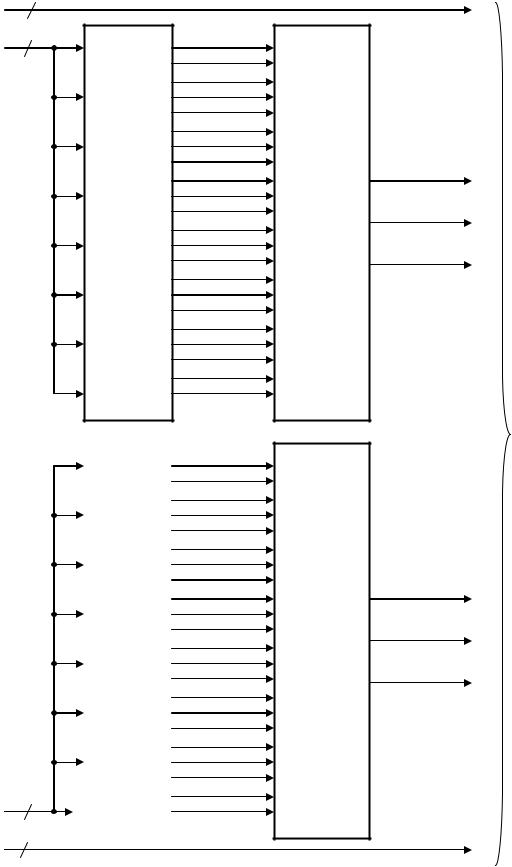

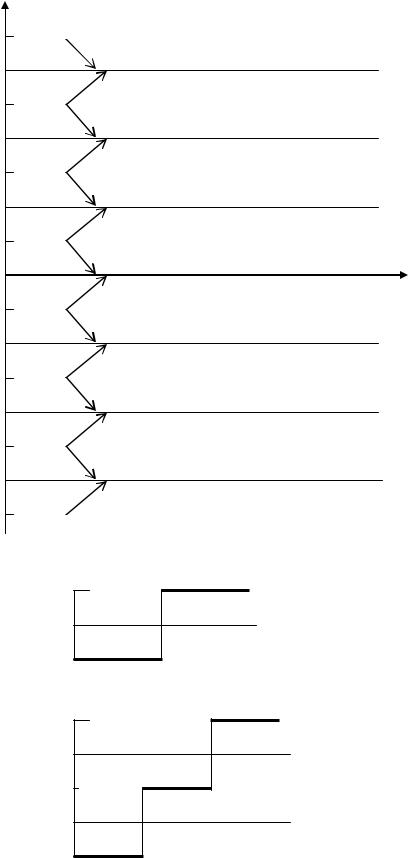

После принятия решения о принятом уровне сигнала рисунки 6.10 и 6.11, соответствующий уровень поступает на АЦП, в котором в соответствии с таблицей 6.1 преобразуется в одно из восьми состояний трех цифровых потоков (для 64 КАМ) по синфазному Р1Р2Р3 и квадратурному Q1Q2Q3 каналам.

Преобразование восьмиуровневого сигнала в АЦП |

Таблица 6.1 |

||||

№ |

Входной |

Выходные сигналы в каналах P(Q) |

|||

|

сигнал АЦП |

P1(Q1) |

P2(Q2) |

|

P3(Q3) |

1 |

7L |

0 |

0 |

|

0 |

2 |

5L |

0 |

0 |

|

1 |

3 |

3L |

0 |

1 |

|

0 |

4 |

1L |

0 |

1 |

|

1 |

5 |

-1L |

1 |

0 |

|

0 |

6 |

-3L |

1 |

0 |

|

1 |

7 |

-5L |

1 |

1 |

|

0 |

8 |

-7L |

1 |

1 |

|

1 |

Вуправляющую логику 2 рисунок 6.7 поступают сигналы различных цифровых потоков (уровней) до и после принятия решения. На основе этих сигналов и вырабатываются сигналы ошибки i, (по восемь значений для синфазного и квадратурного каналов), которые подаются на генераторы управляющих сигналов АТЭ и ХРIC.

Вэтой же управляющей логике анализируются «глазковые» диаграммы в каждом из каналов Р и Q и на основе проведенного анализа (см. раздел 3) вырабатываются управляющие сигналы для автоматической регулировки УПЧ, УПТ и фазовой автоподстройки генератора опорного сигнала в демодуляторе.

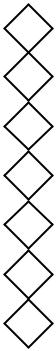

Вуправляющей логике на основе раздельного анализа «глазковых» диаграмм в синфазном и квадратурном каналах фиксируется знак отклонения принятого уровня от номинального значения в момент принятия решения. Поскольку при 64 КАМ анализируется восьмиуровневый сигнал, то при фиксации положительного и отрицательного отклонения принятого сигнала, получается шестнадцать различных состояний рисунок 6.12. Такое количество состояний можно закодировать четырехразрядным двоичным кодом и передать

спомощью четырех двоичных цифровых потоков. Такие дополнительные четыре цифровых потока передаются в многоуровневый декодер вместе с тремя информационными цифровыми потоками как по синфазному так и по квадратурному каналам рисунки 6.7 и 6.10.

133

Р4

8 |

|

РУ1 |

|

|

|

|

|

|

|

|

|

|

|

РУ2 |

|

|

|

|

|

|

|

РУ3 |

|

|

|

|

|

|

|

РУ4 |

|

|

|

|

|

|

|

РУ5 |

|

|

|

|

|

|

|

РУ6 |

|

|

|

|

|

|

|

РУ7 |

|

|

|

|

|

|

|

РУ8 |

|

|

|

|

|

|

|

РУ1 |

|

|

|

|

|

РУ2 |

|

|

|

|

|

РУ3 |

|

|

|

|

|

РУ4 |

|

|

|

|

|

РУ5 |

|

|

|

|

|

РУ6 |

|

|

|

|

|

РУ7 |

|

|

|

|

8 |

РУ8 |

Q |

|

|

|

|

|

|

4 |

|

7L

5L

7L

5L

3L

5L

3L

1L

3L

1L -1L

1L -1L -3L

-1L -3L -5L

-3L -5L -7L

-5L -7L

7L

5L

7L

5L

3L

5L

3L

1L

3L

1L -1L

1L -1L -3L

-1L -3L -5L

-3L -5L -7L

-5L -7L

АЦПР

АЦПQ

Р4 – Р7

Р1

Р2

Р3

К

многоу

ровнев

ому

декоде

ру

Q1

Q2

Q3

Q4 – Q7

Рисунок 6.10 Обработка сигналов на выходе адаптивного трансверсального эквалайзера.

134

U(t)

7L

6L

5L

4L

3L

2L

1L

0 -1L -2L -3L -4L -5L -6L -7L

РУ1

РУ2

РУ1 |

|

U ПОР1 |

|

РУ2 |

|

U ПОР2 |

|

РУ3 |

|

U ПОР3 |

|

РУ4 |

|

U ПОР4 |

t |

РУ5 |

|

U ПОР5 |

|

РУ6 |

|

U ПОР6 |

|

РУ7 |

|

U ПОР7 |

|

РУ8 |

|

а

7L

U ПОР1

5L

7L

U ПОР1

5L

U ПОР2

3L

б

Рисунок 6.11 Принцип работы решающих устройств.

135

7L |

+ |

0000 |

|||

- |

|

0001 |

|||

|

|

||||

5L |

+ |

0010 |

|||

|

|

|

0011 |

||

- |

|||||

|

|||||

3L |

+ |

0100 |

|||

|

|

|

|

||

|

- |

0101 |

|||

1L |

+ |

0110 |

|||

|

|

|

0111 |

||

- |

|||||

|

|||||

|

|

||||

-1L |

+ |

1000 |

|||

|

|

|

|

||

- |

1001 |

||||

|

|||||

-3L |

+ |

1010 |

|||

|

|

|

1011 |

||

- |

|||||

|

|||||

-5L |

+ |

1100 |

|||

|

|

|

|

||

- |

1101 |

||||

|

|||||

-7L |

+ |

1110 |

|||

|

|

|

|

||

- |

1111 |

||||

|

|||||

Рисунок 6.12 Формирование четырех дополнительных цифровых потоков.

Контрольные вопросы

1.Поясните причины появления межсимвольных помех

2.Поясните образование межсимвольных помех при многолучевом приеме

3.Поясните принцип работы адаптивного трансверсального эквалайзера

4.Поясните принцип вычисления весовых коэффициентов для компенсации межсимвольных помех на примере корректора Лакки

5.Поясните принцип компенсации межсимвольных помех в корректоре Лакки

6.Поясните принцип компенсации межсимвольных помех, возникающих из-за неточности восстановления опорного напряжения в демодуляторе

7.Поясните принцип компенсации межсимвольных помех, возникающих из-за переходов с вертикальной поляризации на горизонтальную и наоборот

8.Поясните принцип получения и назначение семи цифровых потоков по синфазному и квадратурному каналам на выходе АТЭ

Список литературы

1.Носов В.И. Основы построения радиорелейных линий синхронной цифровой иерархии. Учебное пособие. УМО по специальности связь. – Новосибирск.: СибГУТИ, 1999. – 98 с.

136

2.SDH Digital Microwave Radio System. System Handbook, vol. 1,2. – NEC, Japan. 1995.

3.SDH Digital Microwave Radio System. Instruction Manual, vol. 1,2,3,4,5. – NEC, Japan. 1995.

137

7 МНОГОУРОВНЕВЫЙ ДЕКОДЕР

Структурная схема многоуровневого декодера приведена на рисунке 7.1. На вход многоуровневого декодера с выхода адаптивного трансверсального эквалайзера поступают по три информационных двоичных цифровых потока по синфазному Р1Р2Р3 и квадратурному Q1Q2Q3 каналам и по четыре вспомогательных (служебных) цифровых потока Р4Р5Р6Р7 по синфазному каналу и Q4Q5Q6Q7 по квадратурному каналу.

В многоуровневом декодере вначале производится преобразование (де размещение - demapping) шести входных информационных потоков

Р1Р2Р3Q1Q2Q3 в шесть цифровых потоков d6d5d4d3d2d1, из которых потоки d2 и d1 имеют избыточные биты, а потоки d6d5d4d3 состоят только из информационных

бит. Затем в MLCM декодере с использованием избыточных бит осуществляется обнаружение и исправление ошибок.

После исправления ошибок шесть потоков d6d5d4d3d2d1 поступают на первый преобразователь скорости, в котором удаляются избыточные биты в первом d1 и втором d2 потоках и суммарная скорость цифрового потока уменьшается на 10 Мбит/с, т.е. здесь удаляется блок FEC рисунок 1.11. В этом же преобразователе скорости осуществляется деперемежение бит, в результате чего шесть цифровых потоков d6d5d4d3d2d1 преобразуются в восемь параллельных цифровых потоков.

Восемь цифровых потоков поступают на дескремблер, состоящий из генератора псевдослучайной последовательности с восьмью выходами и восьми сумматоров по модулю два. В дескремблере из цифрового сигнала удаляется псевдослучайная последовательность, которая выполнила свои функции при выделении тактовой частоты в демодуляторе и при обеспечении электромагнитной совместимости в тракте распространения на пролете.

После десклемблера цифровой сигнал восьмью потоками поступает на выделитель дополнительного заголовка радиоцикла, в котором выделяются служебные каналы общей скоростью 4,24 Мбит/с. Это: дополнительный цифровой поток 2,048 Мбит/с, пять служебных каналов данных по 64 Кбит/с каждый и канал, связывающий приемник и передатчик ствола на пролете для осуществления автоматической регулировки мощности передатчика при замираниях сигнала.

После расформирования дополнительного заголовка радиоцикла сигнал восьмью потоками поступает на второй преобразователь скорости, где устраняются биты, которые были заняты служебными сигналами дополнительного заголовка радиоцикла. После этого преобразователя скорости суммарная скорость цифрового сигнала становится равной 155, 520 Мбит/с, т.е. скорости синхронного транспортного модуля STM-1, который поступает на вход безобрывного переключателя рабочего ствола на резервный.

138

P

1

2

3

4

5

6

7

1 Q

2

3

4

5

6

7

FT

|

|

Пр-ль |

Деразме |

|

скорости |

щение и |

FT |

и |

декодер |

|

депереме |

|

|

жение |

FT

ГУН1

ГЦС2

Пр.ЦСС

ГПСП

ГЦС1

Переключ.

RFCOH |

|

Пр-ль |

DEMUX |

|

скорости |

|

|

|

|

|

|

ГУН2

ГУН2

Рисунок 7.1 Структурная схема многоуровневого декодера

139

К

безобрыв

ному

переклю

чателю

FT

2 М

64К 5

АРМП

Работой генератора псевдослучайной последовательности десклемблера, выделителя дополнительного заголовка радиоцикла и второго преобразователя скорости управляет генератор циклового синхросигнала ГЦС1, который синхронизируется под начало цикла принимаемого цифрового сигнала с помощью приемника циклового синхросигнала Пр.ЦСС.

7.1 Устройство обнаружения и исправления ошибок.

Структурная схема устройства обнаружения и исправления ошибок приведена на рисунке 7.2.

|

P4 – P7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Q4 – Q7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P1 |

|

|

d5 |

|

|

|

|

|

|

|

|

Решающее |

|

D5 |

|||||||

|

|

d4 |

2 |

|

|

|

|

|

|

|

D4 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

устройство |

|

||||||||

P2 |

|

|

d3 |

|

|

|

|

|

|

|

|

|

D3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

P3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Деразмеще |

|

d2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

|

ние |

|

1 |

|

|

|

Декодер |

|

|

|

|

|

|

|

Диф. |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Q1 |

|

|

|

|

|

|

|

|

четности |

|

|

|

|

|

|

|

Декодер |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

||||

Q3 |

|

|

d1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Декодер |

|

3 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Витерби |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 7.2 Устройство деразмещения входных сигналов и исправление ошибок

На входах устройства обнаружения и исправления ошибок приходят по

семь цифровых потоков Р1Р2Р3Р4Р5Р6Р7 по синфазному и Q1Q2Q3Q4Q5Q6Q7 по квадратурному каналам. По три информационных потока Р1Р2Р3 и Q1Q2Q3

получены в синфазном и квадратурном каналах соответственно на выходах адаптивного трансверсального эквалайзера рисунок 6.10, где в аналоговоцифровых преобразователях принятых восемь уровней преобразуются в три цифровых потока таблица 6.1.

В управляющей логике 2 в адаптивном трансверсальном эквалайзере рисунок 6.7 фиксируется знак отклонения принятого уровня от его номинального значения перед принятием решения. Эта информация передается

140