- •1. Интерфейсы, стыки, протоколы.

- •2 Основные понятия.

- •3 Классификация устройств (интер-сов)

- •4. Базовая эталонная модель взаимод-я открытых систем.

- •7. Шина расширения.

- •5. Пространство ввода-вывода.

- •6. Обработка прерываний

- •8. Шина isa.

- •9. Шина eisa.

- •10. Локальная шина vlb.

- •11. Шина pci.

- •12. Мосты на шине pci и конфигурирование устройств.

- •13. Разновидности шины pci.

- •14. Магистральный интерфейс agp.

- •17. Технология Hyper Transport.

- •18. Интерфейс lpc.

- •15. Шина pc mcia (pc Card).

- •18. Интерфейсы дисплея.

- •19. Интерфейсы нгмд

- •21. Scsi

- •22. Serial ata и sas

- •24. Сом порт

- •25. Интерфейсы клавиатуры и мыши.

- •26. Общие сведения о шине usb.

10. Локальная шина vlb.

Шины ввода/вывода ISA, МСА, EISA имеют низкую производительность, обусловленную их ролью в структуре PC. Современные приложения требуют существенного повышения пропускной способности шины. Одним из решений проблемы стало применение локальной шины процессора 486. Шину процессора использовали как место подключения периферии (контроллера дисков и графического адаптера). Шины ввода/вывода ISA, МСА, EISA имеют низкую производительность, обусловленную их ролью в структуре PC. Современные приложения требуют существенного повышения пропускной способности шины. Одним из решений проблемы стало применение локальной шины процессора 486. Шину процессора использовали как место подключения периферии (контроллера дисков и графического адаптера).

Из-за ограниченной нагрузочной способности шины процессора больше трех слотов VLB на системной плате не устанавливают. Максимальная тактовая частота шины – 66 МГц, хотя тина работает надежнее на частоте 33 МГц. Реально в пакетном цикле передача 4х4=16 байт данных требует 5 тактов шины, так что даже в нем пропускная способность составляет 105,6 Мбайт/с, а в обычном режиме (по такту на фазу адреса и на фазу данных) – 66 Мбайт/с. Шину VLB использовали для подключения графического адаптера и контроллера дисков. Встречаются системные платы, которые имеют встроенный графический и дисковый адаптеры с шиной VLB, но самих слотов VLB нет. Это означает, что на плате установлены микросхемы указанных адаптеров для шины VLB. Такая неявная шина по производительности не уступает обычной, а с точки зрения надежности и совместимости она даже лучше.

11. Шина pci.

PCI (Peripheral Component Interconnect) local bus – шина соединения периферийных компонентов. Будучи локальной, эта шина занимает особое место в современной архитектуре PC, являясь мостом (mezzanine bus) между системной шиной процессора и шиной ввода/вывода ISA/EISA или МСА. Шина PCI разрабатывалась в расчете на Pentium-системы, но хорошо сочетается и с процессорами 486. Является четко стандартизованной высокопроизводительной и надежной шиной расширения. В настоящее время действует спецификация PCI 2.1. При частоте шины 33 МГц скорость теоретически достигает 132/264 Мбайт/с для 32/64 бит; при частоте синхронизации 66 МГц – в два раза выше (версия 2.1 допускает частоту до 66 МГц при согласии всех устройств на шине).

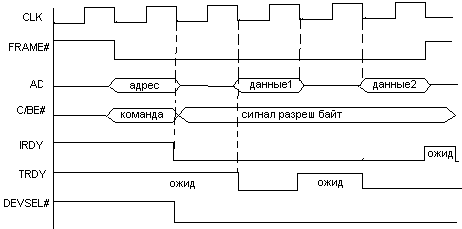

Шина является синхронной – фиксация всех сигналов выполняется по положительному перепаду (фронту) сигнала CLK. В каждой транзакции (обмене по шине) участвуют два устройства – инициатор обмена (Initiator или Master, инициирующее устройство, ИУ) и целевое устройство (Target или Slave, ЦУ).

Шина PCI все транзакции трактует как пакетные: каждая транзакция начинается фазой адреса, за которой может следовать одна или несколько фаз данных. Для адреса и данных используются общие мультиплексированные линии.

В начале транзакции ИУ активизирует сигнал FRAME#, по шине AD передает целевой адрес, а по линиям С/ВЕ# – информацию о типе транзакции (команде). Адресованное ЦУ отзывается сигналом DEVSEL#, после чего ИУ может указать на свою готовность к обмену данными сигналом IRDY#. Когда к обмену данными будет готово и ЦУ, оно установит сигнал TRDY#. Данные по шине AD могут передаваться только при одновременном наличии сигналов IRDY# и TRDY#. С помощью этих сигналов ИУ и ЦУ согласуют свои скорости, вводя такты ожидания.

Количество фаз (циклов) данных в пакете заранее не определено, но перед последним циклом ИУ при введенном сигнале IRDY# снимает сигнал FRAME#. После последней фазы данных ИУ снимает сигнал IRDY#, и шина переходит в состояние покоя (PCI Idle) – оба сигнала FRAME# и IRDY# наводятся в пассивном состоянии. Максимальное количество циклов данных в пакете может быть неявно ограничено таймером, определяющим максимальное время, в течение которого ИУ может пользоваться шиной.

ИУ завершает транзакцию одним из следующих способов:

1.Нормальное завершение выполняется по окончании обмена данными.

2.Завершение по тайм-ауту (Time-out) происходит, когда во время транзакции у ИУ отбирают право на управление шиной (снятием сигнала GNT#) или когда истекает время, указанное в его таймере MLT (медленное ЦУ или слишком длинная транзакция).

3.Транзакция отвергается (Abort), когда в течение заданного времени ИУ не получает ответа ЦУ (DEVSEL#).

Транзакция может быть прекращена и по инициативе ЦУ, для этого оно может ввести сигнал STOP#. Возможны три типа прекращения:

1.Отключение (Disconnect) – сигнал STOP# вводится во время активности TRDY#. В этом случае транзакция завершается после фазы данных.

2.Отключение с повтором (Disconnect/Retry) – сигнал STOP# вводится при пассивном состоянии TRDY#, и последняя фаза данных отсутствует. Является указанием ИУ на необходимость повтора транзакции.

3.Отказ (Abort) – сигнал STOP# вводится одновременно со снятием DEVSEL# (в предыдущих случаях во время появления сигнала STOP# сигнал DEVSEL# был активен). В этом случае последняя фаза данных тоже отсутствует, но повтор не запрашивается. Протокол квитирования обеспечивает надежность обмена – ИУ всегда получает информацию об отработке транзакции ЦУ. Средством повышения надежности (достоверности) является применение контроля паритета: линии AD[31:0] и С/ВЕ#[3:0] и в фазе адреса, и в фазе данных защищены битом паритета PAR (количество единичных бит этих линий, включая PAR, должно быть четным). Арбитражем запросов на использование шины занимается специальный узел, входящий в чипсет системной платы. В циклах обращения к памяти адрес, выровненный по границе двойного слова, передается по линиям AD[31:2], линии AD[1:0] задают порядок чередования адресов в пакете:

00 – линейное инкрементирование;

01 – чередование адресов с учетом длины строки кэш-памяти;

1х – зарезервировано.

В циклах обращения к портам ввода/вывода для адресации любого байта используются все линии AD[31:0]. В циклах конфигурационной записи/считывания устройство выбирается индивидуальным сигналом IDSEL#, конфигурационные регистры выбираются двойными словами по линиям AD[7:2], при этом AD[1:0]=00. на шинах PCI может быть не более 4-х устройств.