- •1. Интерфейсы, стыки, протоколы.

- •2 Основные понятия.

- •3 Классификация устройств (интер-сов)

- •4. Базовая эталонная модель взаимод-я открытых систем.

- •7. Шина расширения.

- •5. Пространство ввода-вывода.

- •6. Обработка прерываний

- •8. Шина isa.

- •9. Шина eisa.

- •10. Локальная шина vlb.

- •11. Шина pci.

- •12. Мосты на шине pci и конфигурирование устройств.

- •13. Разновидности шины pci.

- •14. Магистральный интерфейс agp.

- •17. Технология Hyper Transport.

- •18. Интерфейс lpc.

- •15. Шина pc mcia (pc Card).

- •18. Интерфейсы дисплея.

- •19. Интерфейсы нгмд

- •21. Scsi

- •22. Serial ata и sas

- •24. Сом порт

- •25. Интерфейсы клавиатуры и мыши.

- •26. Общие сведения о шине usb.

8. Шина isa.

ISA Вus (Industry Standard Architecture) – шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом. В компьютере XT использовалась шина с разрядностью данных 8 бит и адреса – 20 бит. В компьютерах AT ее расширили до 16 бит данных и 24 бит адреса. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разъемов с шагом выводов 2,54 мм (0.1 дюйма) Подмножество ISA-8 использует только 62-контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С, D). Шина обеспечивает возможность отображения 8- или 16-битныx регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью от 640к до 1Мб. Для шины ISA-16 опциями BIOS Setup может быть разрешено пространство между 15-м и 16-м мегабайтами памяти. Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0–FFh, зарезервированных под устройства системной платы. В PC была принята 10-битная адресация ввода/вывода, при которой линии адреса А[15:10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h–3FFh, то есть всего 758 адресов 8-битных регистров. На некоторые из адресов претендуют системные устройства . Впоследствии стали применять 12-битную адресацию (диапазон l00h-FFFh). При ее использовании необходимо учитывать возможность присутствия на шине старых 10-битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9:0] во всей допустимой области 12-битного адреса четыре раза (у каждого 10-битного адреса будет еще по три 12-битных псевдонима). Шина ISA-8 может предоставить до 6 линий запросов прерываний, ISA-16 – 11. Часть их могут «отобрать» устройства системной платы или шина PCI.

Шина позволяет использовать до трех 8-битных каналов DMA. На 16-битной шине доступны еще три 16-битных канала.

Все перечисленные ресурсы системной шины должны быть бесконфликтно распределены. Бесконфликтность подразумевает следующее:

Каждое устройство должно управлять шиной данных только при чтении по своим адресам или по используемому им каналу DMA. Области адресов для чтения не должны пересекаться. «Подсматривать» операции записи, «адресованные не ему», не возбраняется.

Назначенную линию IRQx или DRQx устройство должно держать на низком уровне и переводить в высокий уровень для активации запроса. Неиспользуемыми линиями запросов устройство управлять не имеет права, они должны быть электрически откоммутированы или подключаться к буферу, находящемуся в третьем состоянии. Одной линией запроса может пользоваться только одно устройство.

Затем появились программно конфигурируемые устройства, которые вытесняются автоматически конфигурируемыми платами PnP.

Набор сигналов 8 разрядной шины предльно прост он позволяет сформировать циклы обмена с памятью и устройств ввода вывода. При этом диаграмм всех циклов очень похожи между собой. 16 разр шина дает более широкие возможности.

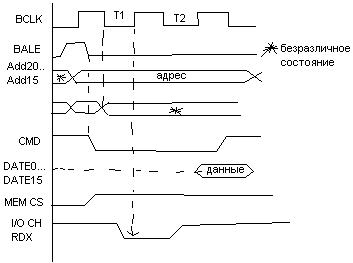

BCLK сигнал тактовой частоты. В цикле обмена необх 2 такта. Для работы с медленно действ устройствами вставл дополнит такты ожидания. В первом такте производится дешифрац адреса , первые 16 разр выдаются по сигнал Add0 Add2.16 след разряды адреса которые появл в ISA – 16 передаются по проводам LA17 .. LA23 . синхронизация происходит по заднему фронту сигнала BALE. Если устройству необх адрес в течении всего цикла обмена. Оно должно запомнить разряды LA17 .. LA23 в своем внутреннем регистре. Сигнал CMD в реальном цикле обмена представл собой 1 из 4 возм сигналов: 1. синхросигнал записи в память . 2. синхросигнал чтения из памяти. 3. синхросигнал записи в УЗВ. 4. синхросигнал чтения из УУЗВ.

Сами данные передаются по шине date , сигнал MEM CS необходим для разрешения работы памяти. Сигнал I/O CH RDX – сигнал готовности поступает от утрс когда оно готово выдать данные.

Длит цикла обмена определ чипсетом и может изм-ся опциями BIOS. При этом выставляются дополнительные такты ожидания. При этом обмен с увв происх длиннее чем обмен с памятью и обмен с 16 разр устр-вами, это учитывается в установках BIOS т.е. производится раздельная установка для памяти и устр ввода вывода а также разд 8разр 16 разр устр.

Логич эквивал шине ISA явл шина PCI04. она предназначена для построения небольших встраиваемых контроллеров. При использовании этой шины платы платы расширения имела и розетку и вилку 1-я шина устанавл вилкой в розетку на сист плате 2-я вилка в розетку первой и т.д. такая конструкция удобна для небольших систем с 2-мя – 3-мя платами.