- •1. Принцип программного управления

- •2. Принцип однородности памяти

- •3. Принцип адресности

- •2. Архитектурное особенности построение пк

- •3. Динамическая и статическая оперативная память

- •4. Конструктивная исполнения модуля оперативной памяти (смотри подробней записи лекций!!!!!)

- •5. Организация чтения записи в оперативную память

- •6. Характеристики модулей оперативной памяти

- •1 Объем

- •2 Тип корпуса

- •3 Тип памяти

- •5 Тайминги

- •8. Классификация вычислительных систем по Флинну

- •9 И 10. Прямой доступ к памяти (dma Direct Memory Access — прямой доступ к памяти)

- •11. Конвейерная обработка информации Оценка производительности идеального конвейера

- •12. Организация обработки прерываний в эвм

- •13. Понятие глубины прерывания, приоритет прерываний

- •14. Аппаратные и программные прерывания

- •15. Последовательность действий при выполнении запроса прерывания

- •16. Функциональная классификация микропроцессоров

- •17. Внутренняя структура мп. Назначение узлов, входящих в типовую структуру мп.

- •18. Процедура выполнения команд. Рабочий цикл процессора

- •19. Многоуровневая иерархическая структура запоминающих устройств

- •20. Логическое представление системной памяти вычислителя

5 Тайминги

Тайминги - это задержки при обращении к микросхемам памяти. Естественно, чем они меньше - тем быстрее работает модуль.

Дело в том, что микросхемы памяти на модуле имеют матричную структуру - представлены в виде ячеек матрицы с номером строки и номером столбца. При обращении к ячейке памяти считывается вся строка, в которой находится нужная ячейка.

Сначала происходит выбор нужной строки, затем нужного столбца. На пересечении строки и номера столбца и находится нужная ячейка. С учетом огромных объемом современной RAM такие матрицы памяти не целиковые - для более быстрого доступа к ячейкам памяти они разбиты на страницы и банки. Сначала происходит обращение к банку памяти, активизация страницы в нем, затем уже происходит работа в пределах текущей страницы: выбор строки и столбца. Все эти действия происходит с определенно задержкой друг относительно друг друга.

Основные тайминги RAM - это задержка между подачей номера строки и номера столбца, называемая временем полного доступа (RAS to CAS delay, RCD), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (CAS latency, CL), задержка между чтением последней ячейки и подачей номера новой строки (RAS precharge, RP). Тайминги измеряются в наносекундах (нс).

Эти тайминги так и идут друг за другом в порядке выполнения операций и также обозначаются схематично 5-5-5-15. В данном случае все три тайминга по 5 нс, а общий рабочий цикл - 15 нс с момента активизации строки.

Главным таймингом считается CAS latency, который часто обозначается сокращенно CL=5. Именно он в наибольшей степени "тормозит" память.

Основываясь на этой информации, вы сможете грамотно выбрать подходящий модуль памяти.

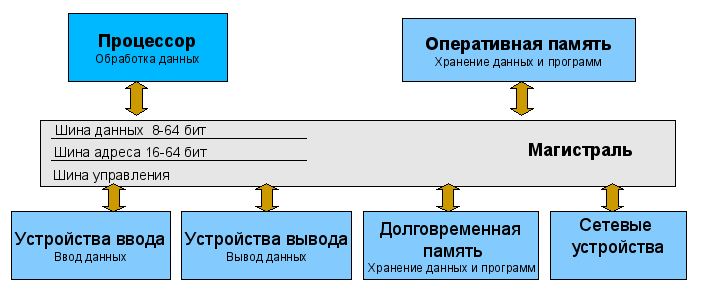

7. МАГИСТРАЛЬНО-МОДУЛЬНЫЙ ПРИНЦИП ПОСТРОЕНИЯ ЭВМ

Архитектура современных ПК основана на магистрально-модульном принципе.

Модульный принцип позволяет потребителю самому подобрать нужную ему конфигурацию компьютера и производить при необходимости его модернизацию. Модульная организация системы опирается на магистральный (шинный) принцип обмена информации. Магистраль или системная шина - это набор электронных линий, связывающих воедино по адресации памяти, передачи данных и служебных сигналов процессор, память и периферийные устройства.

Обмен информацией между отдельными устройствами ЭВМ производится по трем многоразрядным шинам, соединяющим все модули, - шине данных, шине адресов и шине управления.

Разрядность шины данных задается разрядностью процессора, т.е. количеством двоичных разрядов, которые процессор обрабатывает за один такт.

Данные по шине данных могут передаваться как от процессора к какому-либо устройству, так и в обратную сторону, т. е. шина данных является двунаправленной. К основным режимам работы процессора с использованием шины передачи данных можно отнести следующие: запись/чтение данных из оперативной памяти и из внешних запоминающих устройств, чтение данных с устройств ввода, пересылка данных на устройства вывода.

Выбор абонента по обмену данными производит процессор, который формирует код адреса данного устройства, а для ОЗУ - код адреса ячейки памяти. Код адреса передается по адресной шине, причем сигналы передаются в одном направлении, от процессора к устройствам, т. е. эта шина является однонаправленной.

По шине управления передаются сигналы, определяющие характер обмена информацией, и сигналы, синхронизирующие взаимодействие устройств, участвующих в обмене информацией.