- •Определение радиолокации, угла места и азимута цели

- •2. Взаимосвязь основных тактических и технических характеристик рлс

- •2.1. Определение высоты полета цели расчетным методом

- •1. Объединение информации в радиолокационной системе

- •1.1. Задачи, решаемые при объединении информации

- •1.2. Операции, выполняемые в процессе объединения информации

- •Состав св

- •Основные технические характеристики св

- •Принцип взаимодействия устройств св

- •Чтение информации из зу ( режим “ Чтение “).

- •Запись информации в зу ( режим “ Модифицированная запись”).

- •2.1 Назначение и состав зу-02.

- •2.2 Основные технические характеристики блока зу-02.

- •2.3 Взаимодействие элементов блока зу-02 в режимах записи и чтения информации.

- •3.1. Назначение, состав блока дзу-э-8к-м.

- •3.2. Взаимодействие элементов блока дзу-э-8к-м по структурной схеме.

- •1.2. Основные технические характеристики:

- •2. Структурная схема уо

- •4.1. Взаимодействие уо с ВчУ, ук и зу.

- •4.2. Взаимодействие уо с абонентами.

- •41) Органы индикации и оперативного управления поу св

- •1.2Состав арм

- •1.3Взаимодействие функциональных частей рм по структурной схеме в режиме приема информации из св

- •1.4Взаимодействие функциональных частей рм по структурной схеме в режиме выдачи информации в св

- •1.5Состав био

- •3.3. Взаимодействие элементов бив по функциональной схеме в режиме "Лупа х4"

- •1.1. Назначение пульта режимов и масштабов (прм)

- •1.2. Назначение клавишей прм

- •3. Пульт ввода команд (пв)

- •3.1. Назначение пульта ввода команд

- •3.3. Назначение клавишей пульта ввода команд (рм–10)

- •4. Пульт цифрового набора (цн)

2.1 Назначение и состав зу-02.

Запоминающее устройство ЗУ-02 предназначено для приема, временного хранения и выдачи информации в виде двоичных чисел. ЗУ-02 конструктивно выполнено в виде одного двухъярусного блока. Конструкция ЗУ-02 обеспечивает замену всех ТЭЗов и источников напряжения, а также доступ к монтажу блока. На лицевой панели блока расположены лампочки индикации, разъёмы для связи с другими устройствами. Лампочки индикации «Авария 1» и «Авария 2» служат для сигнализации исправности источников напряжения ВН-163, расположенных в блоке ЗУ-02.

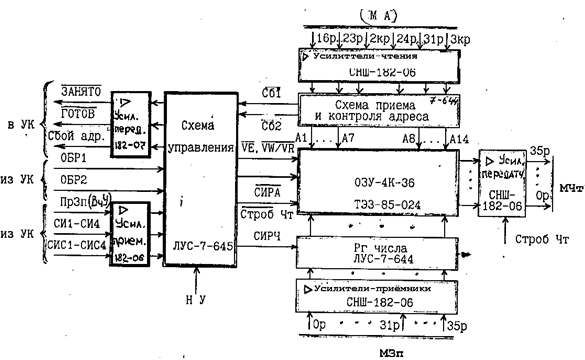

Структурная схема блока ЗУ–02 представлена на рис.3. Основными элементами структурной схемы ЗУ –02 являются:

Рис.3 Структурная схема блока ЗУ-02

магистральные усилители (приёмники и передатчики) (ТЭЗ СНШ – 182-06 (3), СНШ – 182-07 (4));

схема управления (ТЭЗ ЛУС – 7-645);

схема приёма и контроля кода адреса (ТЭЗ ЛУС – 7-644);

регистр числа (ТЭЗ ЛУС – 7-644);

оперативная память (ТЭЗ 85-024 ИЛИ 766 (4));

согласователи уровня (ТЭЗ ЛНС – 38-006 (2));

блоки питания ВН-163 (2).

Магистральные усилители – приёмники служат для приёма сигналов с магистрали адреса МА, магистрали записи МЗп, шины признака записи Пзп, синхроимпульсов СИ1…СИ4 и СИС1…СИС4 и передачи их в другие элементы ЗУ – 02.

Магистральные усилители – передатчики используются для передачи в процессоры (ВчУ, УО) кода числа по магистралям чтения, а сигналов «Занят», «Готов», «Сбой А» в устройство управления каналов (УК)

Схема управления в зависимости от принятых сигналов формирует необходимые сигналы для управления работой блока ЗУ-02. К этим сигналам относятся:

СИРА - сигнал занесения адреса в регистр оперативной памяти;

СТРОБ Чт - сигнал, по которому считанная информация выдаётся в магистраль чтения;

VE - сигнал разрешения выборки элементов памяти при чтении (записи) информации из оперативной памяти ;

VW\VR - признак чтения – записи;

СИРЧ - занесения кода числа на регистр числа.

Схема приёма и контроля адреса осуществляет приём адреса, размножение кода адреса, побайтный контроль адреса на нечётность и передачу его в оперативную память блока ЗУ-02. В случае несоответствия результата побайтного контроля коду контрольного разряда вырабатывается сигнал СБ1 или СБ2.

Регистр числа предназначен для приёма кода числа от процессоров (ВчУ, УО).

Оперативная память позволяет принимать, хранить и выдавать 4096 36- разрядных чисел. Оперативная память конструктивно оформлена в четырех ТЭЗах (ТЭЗ-766).

Согласователи уровня позволяют на выходе блока ЗУ-02 в промежутках между сигналами «Обращение-1 (2)» подавать в МЧт уровень логического «0», а при наличии сигнала «Обращение-1 (2)» уровень, выдаваемый в МЧт, в зависимости от считываемой из памяти информации.

Модуль оперативной памяти ОЗУ-4К-36 конструктивно выполнен в четырех ТЭЗах типа 766 или 85-024. Каждый ТЭЗ представляет собой оперативную память на 4096 9-ти разрядных слов со схемой управления.

В качестве элемента оперативной памяти в модулях ОЗУ-4К-36 применена микросхема К134РУ6 для ТЭЗ 766 и К541РУ1 для ТЭЗ 85-024. Микросхемы К134РУ6 и К541РУ1 представляют собой оперативную память статического типа на 1024бит одного разряда (К134РУ6) или 4096 бит одного разряда (К541РУ1).