- •Определение радиолокации, угла места и азимута цели

- •2. Взаимосвязь основных тактических и технических характеристик рлс

- •2.1. Определение высоты полета цели расчетным методом

- •1. Объединение информации в радиолокационной системе

- •1.1. Задачи, решаемые при объединении информации

- •1.2. Операции, выполняемые в процессе объединения информации

- •Состав св

- •Основные технические характеристики св

- •Принцип взаимодействия устройств св

- •Чтение информации из зу ( режим “ Чтение “).

- •Запись информации в зу ( режим “ Модифицированная запись”).

- •2.1 Назначение и состав зу-02.

- •2.2 Основные технические характеристики блока зу-02.

- •2.3 Взаимодействие элементов блока зу-02 в режимах записи и чтения информации.

- •3.1. Назначение, состав блока дзу-э-8к-м.

- •3.2. Взаимодействие элементов блока дзу-э-8к-м по структурной схеме.

- •1.2. Основные технические характеристики:

- •2. Структурная схема уо

- •4.1. Взаимодействие уо с ВчУ, ук и зу.

- •4.2. Взаимодействие уо с абонентами.

- •41) Органы индикации и оперативного управления поу св

- •1.2Состав арм

- •1.3Взаимодействие функциональных частей рм по структурной схеме в режиме приема информации из св

- •1.4Взаимодействие функциональных частей рм по структурной схеме в режиме выдачи информации в св

- •1.5Состав био

- •3.3. Взаимодействие элементов бив по функциональной схеме в режиме "Лупа х4"

- •1.1. Назначение пульта режимов и масштабов (прм)

- •1.2. Назначение клавишей прм

- •3. Пульт ввода команд (пв)

- •3.1. Назначение пульта ввода команд

- •3.3. Назначение клавишей пульта ввода команд (рм–10)

- •4. Пульт цифрового набора (цн)

Чтение информации из зу ( режим “ Чтение “).

При обращении к ЗУ в режиме чтения информации процессор устанавливает в МА адрес ячейки ЗУ, к которой осуществляется обращение, а по КШУ1 процессор выдаёт вУК сигнал ТрОБР1, который является заявкой процессора на обращении к ЗУ. Полный адрес ячейки ЗУ состоит из адреса модуля и адреса ячейки. Четыре старших разряда магистрали адреса (АМ0…АМ3) подключены к УК. По этим разрядам МА передаётся адрес модуля, где находится ячейка памяти, к которой осуществляется обращение.

Код, содержащийся в старших разрядах магистрали адреса АМ0…АМ3 – номер модуля определённого ЗУ, к которому процессор требует обращения, он передаётся в УК процессором, желающим обратиться к данному модулю памяти одновременно с сигналом ТрОбр1.

УК производит анализ этих сигналов с целью определения, свободен ли в данном такте работы УК требуемый модуль ЗУ, и нет ли в данном такте работы обращения более приоритетного процессора к незанятому модулю ЗУ.

Если требуемый модуль ЗУ свободен, и нет обращения к незанятому модулю со стороны более приоритетного процессора, то УК разрешает процессору, выставившему заявку на обращение к ЗУ, выдачу адреса ячейки ЗУ. Для этого УК выдает в процессор по КШУ1 сигнал ВдА и запускает в работу требуемый модуль ЗУ путём выдачи по КШУ2 сигнала ОБР1.

В результате выдачи этих сигналов производятся следующие действия:

процессор выдаёт в МА адрес требуемой ячейки ЗУ;

в ЗУ возбуждается (начинает работать) схема управления, куда заносится адрес ячейки памяти и формируется сигнал ЗАН, используемый для анализа занятости ЗУ при обращении к нему процессоров (исключается обращение к занятому модулю другого процессора).

примерно через 1 мкс после поступления сигнала ОБР1 сигнал ЗАН снимается, а через 1,2 мкс ЗУ по КШУ 2 выдаёт в УК сигнал готовности (ГОТ) и в МЧт считанную 36-ти разрядную информацию из ячейки с заданным адресом.

по сигналу ГОТ УК по КШУ1 выдаёт в процессор, требовавший обращения к ЗУ, сигнал приём слова (ПрС), по которому производится приём считанной информации из МЧт в процессор.

На этом взаимодействие процессора и модуля ЗУ в режиме “Чтение” завершается. Последовательность обмена сигналами управления при взаимодействии процессора с ЗУ в режиме “Чтение” представлена на рис 2.

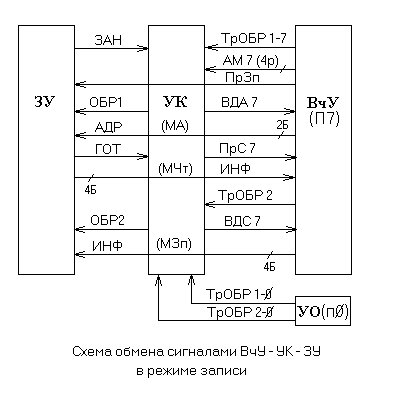

Рис.2. Схема обмена сигналами ВчУ-УК-ЗУ в режиме “Чтение”

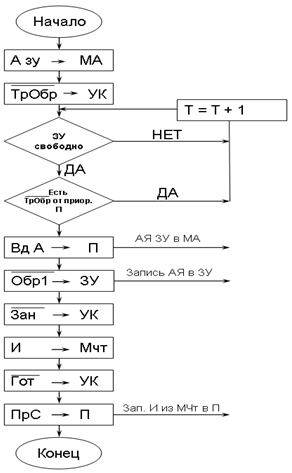

Алгоритм взаимодействия устройств СВ в режиме чтения информации представлен на рис 4.

Запись информации в зу ( режим “ Модифицированная запись”).

Режим записи можно разделить на две фазы. В первой фазе информация считывается из ЗУ, как и в режиме “Чтение”. Отличие от режима “Чтение” состоит в том, что одновременно с выдачей в МА адреса ячейки памяти, процессор выдаёт по специальной шине признак записи (ПрЗп), а в ЗУ момент снятия сигнала ЗАН отсчитывается не от сигнала Обр1, а от сигнала Обр2.

После получения информации из МЧт по сигналу ПрС и обработки её процессор по КШУ1 выдаёт в УК сигнал ТрОбр2.

Если в данном такте работы УК не поступил сигнал ТрОБР2 от более приоритетного процессора, то УК посылает в процессор по КШУ1 сигнал “выдача слова“ (ВдС), а в ЗУ по КШУ2 – сигнал Обр2.

В противном случае (если есть сигнал ТрОбр2 от более приоритетного процессора ) обслуживание процессора откладывается до следующего такта работы УК. По сигналу ВдС процессор выдаёт в МЗп сформированную для записи в ячейку памяти информацию. На этом процесс обмена информацией в режиме “Модифицированная запись” заканчивается. Последовательность обмена сигналами управления при взаимодействии процессора с ЗУ в режиме “Модифицированная запись” представлена на рис 3.

Рис.3. Схема обмена сигналами ВчУ-УК-ЗУ в режиме “Модифицированная запись”

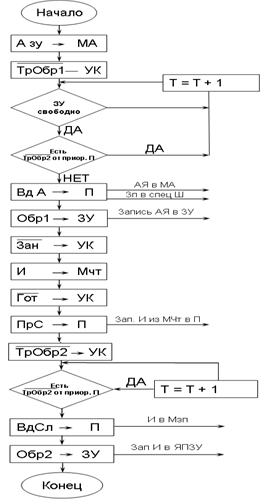

Алгоритм взаимодействия устройств СВ в режиме записи информации представлен на рис 5.

Рис.4. Алгоритм взаимодействия устройств СВ в режиме “Чтение”

Рис.5. Алгоритм взаимодействия устройств СВ в режиме “Модифицированная запись”

ВОПРОС №32

Запоминающее устройство (ЗУ) вычислительной машины – комплекс технических средств, предназначенных для записи, хранения и выдачи информации, представленной в виде цифровых кодов.

Ввиду наличия большого числа признаков, по которым можно классифицировать ЗУ, ограничимся лишь теми, которые характеризуют ЗУ с точки зрения особенностей их функционирования и назначения.

По методу поиска информации ЗУ подразделяются на адресные и безадресные.

В адресных ЗУ поиск информации осуществляется по адресу ячейки памяти, в которой она хранится.

Безадресные ЗУ можно разделить на ассоциативные и магазинные (стековые). В ассоциативных ЗУ поиск информации осуществляется по признакам самой информации (по содержанию ячейки). В магазинных (стековых) ЗУ (в отличие от адресных и ассоциативных) обращение к ячейкам возможно только в определённом порядке, при этом чтение производится в последовательности обратной записи.

По способу записи и считывания многоразрядных слов ЗУ делится на параллельные и последовательные.

В параллельных ЗУ n – разрядное слово записывается и считывается одновременно всеми своими разрядами. Устройство должно содержать n идентичных записывающих и считывающих элементов.

В последовательных ЗУ запись и считывание производится последовательно во времени – разряд за разрядом. Это увеличивает время обращения к ЗУ, однако объём оборудования уменьшается.

По способу хранения информации различают статические и динамические ЗУ.

В статических ЗУ хранимая информация фиксируется (неподвижна) по отношению к носителю в течение всего времени хранения. Примерами статических ЗУ являются устройства на ферритовых сердечниках, электронно–лучевых трубках и т. д.

В динамических ЗУ информация находится в непрерывном движении по отношению к запоминающей среде (ЗУ на линиях задержки).

По характеру обращения к ячейкам памяти различают ЗУ с последовательным и произвольным обращением.

В ЗУ с последовательным обращением считывание (запись) информации производится в строго определённом порядке при обязательном перемещении носителя относительно считывающих и записывающих элементов. Примерами ЗУ с последовательным обращением являются ЗУ на магнитных лентах, барабанах, дисках. В ЗУ с произвольным обращением время, необходимое для записи или считывания слова информации, является постоянной величиной, практически не зависящей от того, к какой ячейке ЗУ производится обращение, и определяется только быстродействием схем, осуществляющих выборку ( ЗУ на ферритовых сердечниках).

По характеру считывания информации ЗУ делятся на устройства со считыванием без разрушения и с разрушением информации.

По функциональному назначению общепринятой считается следующая классификация ЗУ: регистровые, сверхоперативные, оперативные, постоянные и полупостоянные, внешние, буферные запоминающие устройства.

Основу регистровой памяти составляют регистры.

Регистр (RG)- это узел вычислительной машины представляющий собой упорядоченную совокупность электронных запоминающих элементов с системой управления входными и выходными сигналами и предназначенный для выполнения следующих основных микроопераций над n- разрядным входным кодом X1 X2 X3…Xn-1Xn:

- установка (сброс) регистра в состояние 000 … 00;

- установка регистра в состояние 111 … 11;

- приём и хранение в регистре кода числа X1X2X3…Xn-1Xn, где Xi (i=1,2,3…n)- двоичное значение переменной данного разряда, равное «0» или «1»;

- передача числа из регистра в прямом или обратном коде;

- сдвиг хранимого в регистре кода на заданное число разрядов вправо или влево;

- преобразование представления кода из параллельной формы записи в последовательную и, наоборот, при приёме или выдаче n- разрядного кода.

В регистрах также могут выполняться поразрядные логические и арифметические микрооперации над кодами двух чисел X1X2X3…Xn-1Xn и Y1Y2Y3…Yn-1Yn.

Регистровая память используется обычно во всех устройства ЭВМ. Регистры современных ЭВМ выполняются на тех же элементах, что и логические схемы.

Сверхоперативные ЗУ (СОЗУ, RAM)- ЗУ, имеющие быстродействие, соизмеримое с быстродействием процессора, и служащие для хранения ряда чисел, необходимых для выполнения некоторой текущей последовательности команд программы.

Выборка и запись программ в СОЗУ может быть адресной (прямой), магазинной, ассоциативной.

Оперативные запоминающие устройства (ОЗУ, RAM)

ОЗУ – ЗУ, имеющие информационную ёмкость, достаточную для выполнения программ или их частей, и работающие с циклом, который в несколько раз больше цикла работы процессора. Разделение основного ОЗУ на ряд модулей (блоков, секций) позволяет увеличить его быстродействие, за счёт совмещения различных фаз временных циклов при параллельном обращении к различным блокам. ОЗУ служат для хранения исходных данных, программ, промежуточных и окончательных результатов решения. ОЗУ находится в функциональных отношениях с процессором при реализации процесса обработки данных, и является основным внутренним ЗУ машины. ОЗУ может работать в режимах записи, хранения и считывания информации. Функциональные возможности ОЗУ шире, чем ПЗУ: ОЗУ может работать в качестве ПЗУ, т.е. в режиме многократного считывания однократно записанной информации.

Основной составной частью микросхемы ОЗУ является массив элементов памяти (ЭП), объединённых в матрицу накопителя. Каждый ЭП имеет свой адрес. Для обращения к ЭП необходимо его «выбрать» с помощью кода адреса, сигналы которого подводят к соответствующим выводам микросхемы.

Разрядность кода адреса m, равная числу двоичных единиц в нём, определяет информационную ёмкость микросхемы ОЗУ, т.е. число ЭП в матрице, которое равно 2m. Например, микросхема, у которой число адресных входов равно m=10, содержит в матрице 210=1024 ЭП, т.е. имеет информационную ёмкость 1024 бит = 1 Кбит.

Для ввода (записи) и вывода (считывания) информации служит вход и выход микросхемы. Для управления режимом работы микросхемы ОЗУ на специальный вход подаётся сигнал «Запись-считывание». Если его значение равно единице, то устанавливается режим записи бита информации по адресу, указанному кодом адреса. Если же значение сигнала равно нулю, то устанавливается режим чтения информации.

Постоянные запоминающие устройства (ПЗУ,ROM), полупостоянные запоминающие устройства (ППЗУ,PROM)

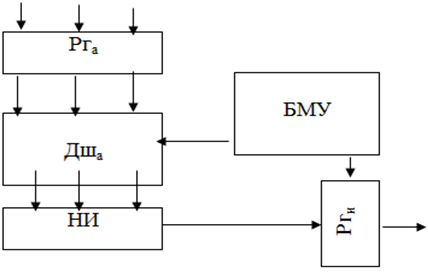

Постоянные и полупостоянные ЗУ предназначены для хранения информации, которая не изменяется в процессе решения задачи: различные константы, таблицы, программы специализированных ЭВМ. Постоянные (или долговременные) ЗУ предназначены только для считывания информации в процессе работы устройств ЭВМ. Скорость считывания в ПЗУ должна быть сравнима со скоростью работы узлов процессора. Структурная схема ПЗУ приведена на рис. 1.

Рис. 1. Структурная схема ПЗУ

Постоянная, не изменяемая в процессе работы ЭВМ информация записана в накопителе информации (НИ). Как правило, ПЗУ строятся по принципу внешней выборки. Код адреса числа принимается в регистр адреса Рга и дешифрируется дешифратором адреса Дша. Выходной сигнал с Дша используют для возбуждения одного из формирователей адресного тока Фта. Выходные сигналы с НИ усиливаются блоком усилителей считывания БУСч и заносятся в виде кода в выходной информационный регистр Рги. Необходимая последовательность управляющих сигналов формируется с помощью блока местного управления (БМУ).

Накопители информации строятся с использованием различных запоминающих элементов. По характеру занесения и возможностям замены информации, накопители информации ПЗУ можно разделить на накопители с фиксированной записью информации, электрической перезаписью информации, механической перезаписью информации.

В накопителях первой группы, невозможно изменить информацию. В накопителях второй и третьей группы, называемых иначе полупостоянными (перепрограммируемыми) ЗУ и ЗУ с неоперативной сменой информации, возможно изменение информации вне машины или при нахождении блока внутри машины, но со скоростью меньшей скорости работы машины.

Наибольший интерес представляют электрически программируемые ПЗУ, поскольку электрическая перезапись обеспечивает неоднократную перепрограммируемость содержимого накопителя ПЗУ.

Широкий диапазон применения ПЗУ (ROM) в вычислительной технике обусловлен тем, что они сохраняют данные при выключении питания. Побочным эффектом оказывается невозможность записи. Существует довольно много типов микросхем ROM. В обычные ROM запись осуществляется в ходе технологического процесса производства и в дальнейшем изменить их содержимое невозможно.

Микросхемы программируемых ROM (PROM) выпускаются «чистыми» и допускают запись с помощью программатора. После того как PROM запрограммировано, стереть его содержимое невозможно.

Микросхемы стираемых PROM (EPROM) имеют небольшое окно, через которое их содержимое можно стереть ультрафиолетовым светом. После стирания их можно перепрограммировать с помощью программатора. Эти EPROM получили широкое применение в вычислительной технике.

Буферные запоминающие устройства (БЗУ)

Буферные ЗУ – ЗУ, предназначенные для промежуточного хранения информации при её обмене между устройствами, работающими с разной скоростью. Роль буферных ЗУ, как правило, выполняют регистровые схемы (например, в унифицированных адаптерах сопряжения) или ОЗУ с малой ёмкостью памяти (например, в аппаратуре передачи данных).

ВОПРОС №33

Назначение, состав и основные технические характеристики блока ЗУ-02. Взаимодействие элементов блока ЗУ-02 по структурной схеме.