MSP430_Final

.pdf

15.3. Функционирование модуля USСI: режим UART 371

Для получения длительности импульса, равной 3/16 от длительности битово го интервала, как того требует стандарт IrDA, выбирается тактовый сигнал BITCLK16 (UCIRTXCLK = 1), а длина импульса задаётся равной шести полупе риодам тактового сигнала при UCIRTXPLx = 6 – 1 = 5.

При UCIRTXCLK = 0 длительность импульса tPULSE определяется частотой сигнала BRCLK и вычисляется из следующего выражения:

UCIRTXPLx = tPULSE 2 fBRCLK – 1.

В случае, когда длительность импульса определяется сигналом BRCLK, со держимое регистра предделителя UCBRx должно быть больше или равно 5.

Декодирование сигналов IrDA

При UCIRRXPL = 0 декодер осуществляет обнаружение положительных им пульсов, в противном случае — отрицательных. Установкой бита UCIRRXFE можно в дополнение к аналоговому помехоподавляющему фильтру включить программируемый цифровой фильтр. При установленном бите UCIRRXFE на вход декодера пропускаются только те импульсы, длительность которых больше заданной длины фильтра. Импульсы меньшей длительности игнорируются. Дли на фильтра UCIRRXFLx определяется из выражения:

UCIRRXFLx = (tPULSE – tWAKE) 2 fBRCLK – 4,

где: tPULSE — минимальная длительность принимаемых импульсов;

tWAKE — время выхода из режима пониженного энергопотребления. Оно рав но нулю, если ЦПУ находится в активном режиме.

15.3.6. Автоматическое обнаружение ошибок

Подавление импульсных помех позволяет предотвратить случайный запуск модуля USCI. Любые импульсы на выводе UCAxRXD, длительность которых меньше t (примерно 150 нс), будут игнорироваться. Точные значения параметра t приводятся в справочной документации на конкретные модели.

При появлении на выводе UCAxRXD сигнала НИЗКОГО уровня длитель ностью свыше t модуль USCI пытается определить наличие старт бита, исполь зуя мажорирование. Если по результатам мажорирования старт бит обнаружен не будет, то модуль USCI прекращает приём символа и снова переходит к ожиданию сигнала НИЗКОГО уровня на выводе UCAxRXD. Мажорирование также исполь зуется при чтении каждого бита слова.

При приёме символов модуль USCI автоматически обнаруживает ошибки кадра, ошибки чётности, ошибки переполнения, а также обрывы связи. Обнару жение тех или иных ошибок приводит к установке соответствующих битов UCFE, UCPE, UCOE и UCBRK. Одновременно с установкой любого из битов UCFE, UCPE или UCOE также устанавливается бит UCRXERR. Все ошибки приёма описаны в Табл. 15.1.

372 Глава 15. Универсальный последовательный коммуникационный интерфейс: режим UART

Таблица 15.1. Ошибки приёма

Ошибка |

Флаг |

Описание |

|

ошибки |

|||

|

|

||

|

|

|

|

Ошибка кадра |

UCFE |

Ошибка кадра возникает при обнаружении стоп бита с нулевым значе |

|

|

|

нием. Если используются два стоп бита, то проверяется значение обоих. |

|

|

|

При обнаружении ошибки кадра устанавливается бит UCFE |

|

|

|

|

|

Ошибка |

UCPE |

Ошибка чётности возникает при несоответствии числа единичных битов |

|

чётности |

|

в слове и значения бита чётности. Если бит адреса присутствует в симво |

|

|

|

ле, то он тоже участвует в определении чётности. При обнаружении |

|

|

|

ошибки чётности устанавливается бит UCPE |

|

|

|

|

|

Переполнение |

UCOE |

Ошибка переполнения возникает, если принятый символ помещается в |

|

приёмника |

|

регистр UCAxRXBUF до прочтения из него предыдущего. При обнару |

|

|

|

жении переполнения устанавливается бит UCOE |

|

|

|

|

|

Обрыв связи |

UCBRK |

Если не используется автоматическое определение скорости передачи, |

|

|

|

то состояние обрыва связи регистрируется тогда, когда все биты данных, |

|

|

|

бит чётности и все стоп биты принятого символа имеют нулевое значе |

|

|

|

ние. При обнаружении обрыва связи устанавливается бит UCBRK. Если |

|

|

|

установлен бит разрешения прерывания UCBRKIE, то при обнаружении |

|

|

|

обрыва связи также устанавливается флаг прерывания UCAxRXIFG |

|

|

|

|

Если бит UCRXEIE = 0, то при обнаружении ошибки кадра или ошибки чёт ности принятый символ не загружается в регистр UCAxRXBUF. При UCRXEIE = 1 все принимаемые символы помещаются в регистр UCAxRXBUF независимо от наличия ошибок.

При установке любого из битов UCFE, UCPE, UCOE, UCBRK и UCRXERR он остаётся в этом состоянии до тех пор, пока не будет сброшен программно или в результате чтения регистра UCAxRXBUF. Бит UCOE должен сбрасываться только путём чтения регистра UCAxRXBUF, в противном случае этот бит не бу дет работать правильно. Для надёжного обнаружения переполнения рекоменду ется следующая последовательность действий. После приёма символа и установ ки флага UCAxRXIFG сначала выполняется чтение регистра UCAxSTAT для про верки флагов ошибок, включая флаг переполнения UCOE. Затем выполняется чтение регистра UCAxRXBUF. При этом будут сброшены все флаги ошибок, за исключением UCOE, если между операциями чтения регистров UCAxSTAT и UCAxRXBUF в последний было записано новое значение. Для обнаружения та кой ситуации необходимо проверять состояние флага UCOE после чтения регис тра UCAxRXBUF. Обратите внимание — флаг UCRXERR в данном случае не ус танавливается.

15.3.7. Разрешение приёма USCI

После включения модуля USCI сбросом бита UCSWRST приёмник готов к работе и находится в состоянии ожидания. Контроллер скорости передачи нахо дится в состоянии готовности, но не генерирует никаких тактовых сигналов, пос кольку задающий тактовый сигнал на него не поступает.

По спадающему фронту старт бита разрешается работа контроллера скорости передачи, а конечный автомат UART проверяет наличие корректного старт бита. При отсутствии корректного старт бита конечный автомат переходит в состояние ожидания, а контроллер скорости передачи снова выключается. В случае обнару жения корректного старт бита будет принят очередной символ данных.

15.3.Функционирование модуля USСI: режим UART 373

Врежиме многопроцессорного обмена idle line (UCMODEx = 01) конечный автомат UART после приёма символа контролирует наличие активности на ли нии. При обнаружении старт бита осуществляется приём очередного символа.

Впротивном случае после приёма 10 подряд идущих единичных битов устанавли вается флаг UCIDLE, конечный автомат UART переходит в состояние ожидания, а контроллер скорости передачи выключается.

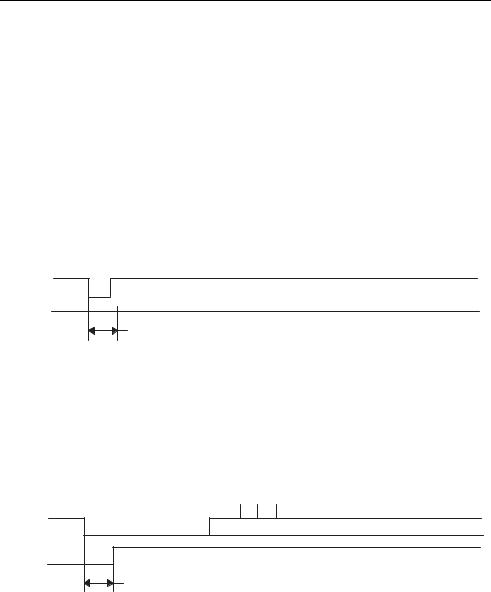

Подавление импульсных помех при приёме

Подавление импульсных помех позволяет предотвратить случайный запуск модуля USCI. Любые импульсы на выводе UCAxRXD, длительность которых меньше t (примерно 150 нс), будут игнорироваться модулем, как показано на Рис. 15.8. Точные значения параметра t приводятся в справочной документации на конкретные модели.

URXDx

URXS

tτ

Рис. 15.8. Подавление импульсной помехи, приёмник USCI не запускается.

При появлении на выводе UCAxRXD импульса длительностью больше t , приёмник модуля USCI пытается определить наличие старт бита, используя ма жорирование, как показано на Рис. 15.9. Если старт бит обнаружен не будет, то модуль USCI прекращает приём символа.

Мажорирование

URXDx

URXS

tτ

Рис. 15.9. Подавление импульсной помехи, модуль USCI активирован.

15.3.8. Разрешение передачи USCI

После включения модуля USCI сбросом бита UCSWRST передатчик готов к работе и находится в состоянии ожидания. Контроллер скорости передачи нахо дится в состоянии готовности, но не генерирует никаких тактовых сигналов, пос кольку задающий тактовый сигнал на него не поступает.

374 Глава 15. Универсальный последовательный коммуникационный интерфейс: режим UART

Передача инициируется записью значения в регистр UCAxTXBUF. При этом включается контроллер скорости передачи, а содержимое регистра пересылается в сдвиговый регистр передачи по следующему после опустошения сдвигового ре гистра такту сигнала BITCLK. После того как регистр UCAxTXBUF будет готов к получению новых данных, устанавливается флаг UCAxTXIFG.

Процесс передачи осуществляется до тех пор, пока имеются данные, загружа емые в регистр UCAxTXBUF до завершения передачи предыдущего значения. Если к моменту завершения передачи очередного значения регистр UCAxTXBUF оказывается пустым, то передатчик возвращается в состояние ожидания, а конт роллер скорости передачи выключается.

15.3.9. Контроллер скорости передачи UART

Контроллер скорости передачи модуля USCI обеспечивает стандартные ско рости обмена при использовании опорных тактовых сигналов нестандартных частот. Контроллер может работать в двух режимах, определяемых битом UCOS16.

Низкочастотный режим

Низкочастотный режим выбирается при UCOS16 = 0. Этот режим позволяет осуществлять обмен при использовании низкочастотного задающего сигнала (скажем, со скоростью 9600 бод при использовании кварцевого резонатора часто той 32 768 Гц). Использование задающего сигнала низкой частоты уменьшает потребление модуля. Данный режим можно использовать и с сигналами более высокой частоты при задании более высоких коэффициентов деления преддели теля, однако при этом для мажорирования будет использоваться временное окно гораздо меньшего размера, что сведёт на нет все преимущества, предоставляемые указанным методом.

В низкочастотном режиме контроллер скорости передачи использует один предделитель и один модулятор для формирования сигнала битовой синхрониза ции. Такое сочетание позволяет получать дробные коэффициенты деления для обеспечения заданной скорости обмена. Максимальная скорость обмена в этом режиме составляет одну треть от частоты тактового сигнала UART BRCLK.

Временные диаграммы для одного бита приведены на Рис. 15.10. Значение каждого принятого бита определяется путём мажорирования. Выборки осущест вляются в периоды N/2 – 1/2, N/2 и N/2 + 1/2 сигнала BRCLK, где N — число пе риодов BRCLK, укладывающихся в один период BITCLK.

Модуляция определяется содержимым битов UCBRSx, как показано в Табл. 15.2. Значение 1 в таблице говорит о том, что m = 1 и соответствующий пе риод сигнала BITCLK на один период BRCLK больше, чем при m = 0. Модуляция циклически повторяется после 8 бит и перезапускается при появлении очередно го старт бита.

15.3. Функционирование модуля USСI: режим UART 375

|

Мажорирование: (m = 0) |

|

|

|

|

|

Начало |

(m = 1) |

|

|

|

|

|

|

|

|

|

|

|

|

бита |

|

|

|

|

|

|

BRCLK |

|

|

|

|

|

|

Счётчик |

1 |

N/2 |

N/2–1 N/2–2 |

1 |

N/2 |

N/2–1 |

N/2 N/2–1 N/2–2 |

0 |

N/2 N/2–1 |

1 |

0 |

N/2 |

|

|

1 |

|||||

BITCLK |

|

|

|

|

|

|

|

INT(N/2) + m(= 0) |

|

NEVEN : INT(N/2) |

|

|

|

|

INT(N/2) + m(= 1) |

|

NODD |

: INT(N/2) + R(= 1) |

|

|

Битовый интервал

m — соответствующий бит модуляции R — остаток от деления N/2

Рис. 15.10. Тактовый сигнал BITCLK при UCOS16 = 0.

Таблица 15.2. Модуляция BITCLK

UCBRSx |

Бит 0 |

Бит 1 |

Бит 2 |

Бит 3 |

Бит 4 |

Бит 5 |

Бит 6 |

Бит 7 |

|

(старт бит) |

|||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

3 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

5 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

Высокочастотный режим

Высокочастотный режим выбирается при UCOS16 = 1. Этот режим поддер живает выборку битового потока UART при использовании задающего тактового сигнала большей частоты. В результате выборка сигнала для мажорирования всегда производится с интервалом, равным 1/16 периода сигнала битовой синх ронизации. Кроме того, при включённых кодере и декодере IrDA этот режим об легчает формирование и приём импульсов стандарта IrDA длительностью 3/16 битового интервала.

В данном режиме используется один предделитель и один модулятор для ге нерации сигнала BITCLK16, частота которого в 16 раз больше частоты BITCLK. Дополнительные делитель и модулятор используются для формирования из BITCLK16 сигнала BITCLK. Такое сочетание позволяет получать дробные коэф фициенты деления сигналов BITCLK и BITCLK16 для обеспечения заданной скорости обмена. Максимальная скорость обмена в этом режиме составляет 1/16 от частоты тактового сигнала UART BRCLK. Если биты UCBRx = 0 или 1, то пер

376 Глава 15. Универсальный последовательный коммуникационный интерфейс: режим UART

вая секция модулятора/предделителя не используется и сигнал BRCLK иденти чен сигналу BITCLK16.

Модуляция сигнала BITCLK16 определяется содержимым битов UCBRFx, как показано в Табл. 15.3. Значение 1 в таблице говорит о том, что m = 1 и соот ветствующий период сигнала BITCLK16 на один период BRCLK больше, чем при m = 0. Модуляция перезапускается в начале каждого битового интервала.

Модуляция сигнала BITCLK определяется содержимым битов UCBRSx (Табл. 15.3), как было описано выше.

Таблица 15.3. Модуляция BITCLK16

UCBRFx |

|

|

Число тактов BITCLK16 после последнего спадающего фронта BITCLK |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

||

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00h |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01h |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

02h |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

03h |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

04h |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

05h |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

06h |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

07h |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

08h |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

09h |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Ah |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Bh |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Ch |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Dh |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Eh |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0Fh |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15.3.10. Установка скорости обмена

Для данного тактового сигнала BRCLK используемая скорость обмена опре деляет требуемое значение коэффициента деления N:

N = fBRCLK .

Baud rate

Коэффициент деления N часто является дробным числом, поэтому для мак симально точного учёта значения N используется, как минимум, одна секция де лителя и модулятора.

Если N больше или равно 16, то можно использовать высокочастотный ре жим, установив бит UCOS16.

15.3. Функционирование модуля USСI: режим UART 377

Установки при использовании низкочастотного режима

В низкочастотном режиме целая часть коэффициента деления реализуется предделителем:

UCBRx = INT(N),

а дробная часть реализуется модулятором, установки которого определяются вы ражением:

UCBRSx = round((N – INT(N)) · 8).

Инкрементирование или декрементирование значения UCBRSx иногда поз воляет уменьшить максимальную частоту битовых ошибок для любого конкрет ного бита. Чтобы узнать, справедливо ли это в данном случае, необходимо опре делить величину ошибки для каждого бита при всех значениях UCBRSx.

Установки при использовании высокочастотного режима

В высокочастотном режиме установки пределителя определяются формулой:

UCBRx = INT(N/16),

а установки модулятора первой секции определяются выражением:

UCBRFx = round(((N/16) – INT(N/16)) · 16).

Если необходимо получить бkольшую точность, то можно дополнительно ис пользовать второй модулятор. Чтобы определить установки, обеспечивающие на именьшее значение максимальной частоты битовых ошибок, необходимо опре делить величину ошибки для всех значений UCBRSx из диапазона 0…7 при на чальных установках UCBRFx, а также при увеличенном и уменьшенном на 1 значениях UCBRFx.

15.3.11. Синхронизация при передаче

Синхронизация при передаче любого символа осуществляется отдельно для каждого бита. Использование модуляции позволяет уменьшить накопленную би товую ошибку. Значения битовых ошибок для отдельных битов можно вычислить по приведённым ниже формулам.

Синхронизация в низкочастотном режиме

В низкочастотном режиме время передачи i го бита Tbit,TX[i] определяется со держимым битов UCBRx и UCBRSx:

Tbit,TX[i] = |

1 |

(UCBRx + m UCBRSx[i]), |

|

||

|

fBRCLK |

|

где mUCBRSx[i] — значение модуляции для i го бита из Табл. 15.2.

Синхронизация в высокочастотном режиме

В высокочастотном режиме время передачи i го бита Tbit,TX[i] определяется содержимым битов UCBRx, UCBRFx и UCBRSx:

378 Глава 15. Универсальный последовательный коммуникационный интерфейс: режим UART

|

|

1 |

|

|

15 |

|

Tbit,TX |

[i] = |

|

|

(16 |

+ m UCBRSx[i]) UCBRx + ∑m UCBRFx |

|

|

|

[j] , |

||||

|

|

fBRCLK |

|

j=0 |

|

|

15

где ∑m UCBRFx[j] — сумма единичных значений соответствующей строки Табл. 15.3;

j=0

mUCBRSx[i] — значение модуляции для i го бита из Табл. 15.2.

Время завершения передачи очередного бита tbit,TX[i] равно сумме всех преды дущих и текущего битовых интервалов:

i

t bit,TX[i] = ∑Tbit,TX[j] . j=0

Для определения величины битовой ошибки это время сравнивается с иде альным значением битового интервала tbit,ideal,TX[i]:

t bit,ideal,TX[i] = |

1 |

(i +1) . |

|

||

|

Baud rate |

|

В конечном итоге ошибка, приведённая к величине идеального битового ин тервала (1/Baud rate), получается равной:

ErrorTX[i] = (tbit,TX[i] – tbit,ideal,TX[i])·Baud rate·100%.

15.3.12. Синхронизация при приёме

Существует два источника ошибок во время приёма. Первый источник — это побитовая ошибка, аналогичная ошибке битовой синхронизации при передаче. Второй источник ошибок — это задержка между появлением фронта старт бита и распознаванием этого фронта модулем USCI. На Рис. 15.11 показаны асинхрон ные ошибки синхронизации между сигналом на выводе UCAxRXD и внутренним тактовым сигналом, формируемым контроллером скорости передачи. Ошибка синхронизации tSYNC находится в пределах от –1/2 до +1/2 периода BRCLK неза висимо от выбранного режима работы контроллера скорости передачи.

Идеальным моментом выборки входного сигнала tbit,ideal,RX[i] является середи

на битового периода: |

1 |

|

|

t bit,ideal,RX[i] = |

(i + 0.5) . |

||

|

|||

|

|||

|

Baud rate |

||

Реальное же время выборки tbit,RX[i] равно сумме битовых интервалов для всех предыдущих битов (см. формулы предыдущего подраздела) плюс половина пери

ода BITCLK для текущего бита i, плюс ошибка синхронизации tSYNC.

Таким образом, для низкочастотного режима работы контроллера скорости передачи время выборки бита tbit,RX[i] определяется выражением:

|

|

|

i 1 |

1 |

(INT( |

|

UCBRx)+ m UCBRSx[i]), |

|

t bit,RX[i] = tSYNC + ∑Tbit,RX[j]+ |

1 |

|||||

|

|

2 |

|||||

|

|

|

j=0 |

fBRCLK |

|||

где |

Tbit,RX[i] = |

1 |

(UCBRx + m UCBRSx[i]); |

||||

|

|||||||

|

|

fBRCLK |

|

|

|

|

|

mUCBRSx[i] — значение модуляции для i го бита из Табл. 15.2.

15.3. Функционирование модуля USСI: режим UART 379

i |

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

||||||||

tideal |

|

|

|

|

|

|

|

|

|

|

t0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

9 10 11 12 13 14 1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

|

9 10 11 12 13 14 1 |

2 |

3 |

4 |

5 |

6 |

|

7 |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BRCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UCAxRXD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

RXD синхр. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

||||||||||||||

tactual |

|

|

|

|

|

|

|

|

|

|

|

|

t0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t2 |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

Ошибка синхронизации ±0.5xBRCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

Выборка |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

RXD синхр. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Мажорирование |

|

|

|

|

Мажорирование |

Мажорирование |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 15.11. Ошибка приёма. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

Для высокочастотного режима работы время выборки бита tbit,RX[i] определя ется выражением:

|

|

|

i 1 |

|

|

|

|

1 |

|

|

|

|

7+m UCBRSx [i] |

|

|

|

|

t bit,RX[i] = tSYNC + ∑Tbit,RX |

|

(8 |

+ m UCBRSx[i]) UCBRx + ∑m UCBRFx |

|

|||||||||||

|

[j] + |

|

|

|

, |

|||||||||||

|

|

|||||||||||||||

|

|

|

[j] |

|

||||||||||||

|

|

|

j=0 |

|

|

|

|

fBRCLK |

|

|

|

j=0 |

|

|

||

|

|

|

1 |

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

(16 |

+ m UCBRSx[i]) UCBRx + ∑m UCBRFx |

|

|

|

||||||||

где |

Tbit,RX |

[i] = |

|

|

|

|

; |

|

|

|||||||

|

fBRCLK |

|

[j] |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

j=0 |

|

|

|

|

||

7+m [i]

∑UCBRSx

m UCBRFx[j] — сумма единичных значений из столбцов 0…7 + mUCBRSx[i] соответствующей строки Табл. 15.3;

mUCBRSx[i] — значение модуляции для i го бита из Табл. 15.2.

В конечном итоге ошибка, приведённая к величине идеального битового ин тервала (1/Baud rate), получается равной:

ErrorRX[i] = (tbit,RX[i] – tbit,ideal,RX[i])·Baud rate·100%.

15.3.13. Типовые скорости обмена и величины ошибок

Установки битов UCBRx, UCBRSx и UCBRFx, необходимые для получения стандартных скоростей обмена при использовании тактового сигнала ACLK час тотой 32 768 Гц (от кварцевого резонатора) и тактового сигнала SCLK, имеющего типичные значения частоты, приведены в Табл. 15.4 и Табл. 15.5. Убедитесь, что частота выбранного источника BRCLK не превышает максимально допустимое значение частоты тактового сигнала для модуля USCI (см. справочную докумен тацию на конкретную модель).

380 Глава 15. Универсальный последовательный коммуникационный интерфейс: режим UART

Таблица 15.4. Установки и значения ошибок для типовых скоростей обмена, UCOS16 = 0

Частота |

Скорость |

|

|

|

Максимальная |

Максимальная |

||

BRCLK [Гц] |

обмена [бод] |

UCBRx |

UCBRSx |

UCBRFx |

ошибка передачи [%] |

ошибка приёма [%] |

||

|

|

|

|

|

|

|

|

|

32 768 |

1200 |

27 |

2 |

0 |

–2.8 |

1.4 |

–5.9 |

2.0 |

|

|

|

|

|

|

|

|

|

32 768 |

2400 |

13 |

6 |

0 |

–4.8 |

6.0 |

–9.7 |

8.3 |

|

|

|

|

|

|

|

|

|

32 768 |

4800 |

6 |

7 |

0 |

–12.1 |

5.7 |

–13.4 |

19.0 |

|

|

|

|

|

|

|

|

|

32 768 |

9600 |

3 |

3 |

0 |

–21.1 |

15.2 |

–44.3 |

21.3 |

|

|

|

|

|

|

|

|

|

1 048 576 |

9600 |

109 |

2 |

0 |

–0.2 |

0.7 |

–1.0 |

0.8 |

|

|

|

|

|

|

|

|

|

1 048 576 |

19 200 |

54 |

5 |

0 |

–1.1 |

1.0 |

–1.5 |

2.5 |

|

|

|

|

|

|

|

|

|

1 048 576 |

38 400 |

27 |

2 |

0 |

–2.8 |

1.4 |

–5.9 |

2.0 |

|

|

|

|

|

|

|

|

|

1 048 576 |

56 000 |

18 |

6 |

0 |

–3.9 |

1.1 |

–4.6 |

5.7 |

|

|

|

|

|

|

|

|

|

1 048 576 |

115 200 |

9 |

1 |

0 |

–1.1 |

10.7 |

–11.5 |

11.3 |

|

|

|

|

|

|

|

|

|

1 048 576 |

128 000 |

8 |

1 |

0 |

–8.9 |

7.5 |

–13.8 |

14.8 |

|

|

|

|

|

|

|

|

|

1 048 576 |

256 000 |

4 |

1 |

0 |

–2.3 |

25.4 |

–13.4 |

38.8 |

|

|

|

|

|

|

|

|

|

1 000 000 |

9600 |

104 |

1 |

0 |

–0.5 |

0.6 |

–0.9 |

1.2 |

|

|

|

|

|

|

|

|

|

1 000 000 |

19 200 |

52 |

0 |

0 |

–1.8 |

0 |

–2.6 |

0.9 |

|

|

|

|

|

|

|

|

|

1 000 000 |

38 400 |

26 |

0 |

0 |

–1.8 |

0 |

–3.6 |

1.8 |

|

|

|

|

|

|

|

|

|

1 000 000 |

56 000 |

17 |

7 |

0 |

–4.8 |

0.8 |

–8.0 |

3.2 |

|

|

|

|

|

|

|

|

|

1 000 000 |

115 000 |

8 |

6 |

0 |

–7.8 |

6.4 |

–9.7 |

16.1 |

|

|

|

|

|

|

|

|

|

1 000 000 |

128 000 |

7 |

7 |

0 |

–10.4 |

6.4 |

–18.0 |

11.6 |

|

|

|

|

|

|

|

|

|

1 000 000 |

256 000 |

3 |

7 |

0 |

–29.6 |

0 |

–43.6 |

5.2 |

|

|

|

|

|

|

|

|

|

4 000 000 |

9600 |

416 |

6 |

0 |

–0.2 |

0.2 |

–0.2 |

0.4 |

|

|

|

|

|

|

|

|

|

4 000 000 |

19 200 |

208 |

3 |

0 |

–0.2 |

0.5 |

–0.3 |

0.8 |

|

|

|

|

|

|

|

|

|

4 000 000 |

38 400 |

104 |

1 |

0 |

–0.5 |

0.6 |

–0.9 |

1.2 |

|

|

|

|

|

|

|

|

|

4 000 000 |

56 000 |

71 |

4 |

0 |

–0.6 |

1.0 |

–1.7 |

1.3 |

|

|

|

|

|

|

|

|

|

4 000 000 |

115 200 |

34 |

6 |

0 |

–2.1 |

0.6 |

–2.5 |

3.1 |

|

|

|

|

|

|

|

|

|

4 000 000 |

128 000 |

31 |

2 |

0 |

–0.8 |

1.6 |

–3.6 |

2.0 |

|

|

|

|

|

|

|

|

|

4 000 000 |

256 000 |

15 |

5 |

0 |

–4.0 |

3.2 |

–8.4 |

5.2 |

|

|

|

|

|

|

|

|

|

8 000 000 |

9600 |

833 |

2 |

0 |

–0.1 |

0 |

–0.2 |

0.1 |

|

|

|

|

|

|

|

|

|

8 000 000 |

19 200 |

416 |

6 |

0 |

–0.2 |

0.2 |

–0.2 |

0.4 |

|

|

|

|

|

|

|

|

|

8 000 000 |

38 400 |

208 |

3 |

0 |

–0.2 |

0.5 |

–0.3 |

0.8 |

|

|

|

|

|

|

|

|

|

8 000 000 |

56 000 |

142 |

7 |

0 |

–0.6 |

0.1 |

–0.7 |

0.8 |

|

|

|

|

|

|

|

|

|

8 000 000 |

115 200 |

69 |

4 |

0 |

–0.6 |

0.8 |

–1.8 |

1.1 |

|

|

|

|

|

|

|

|

|

8 000 000 |

128 000 |

62 |

4 |

0 |

–0.8 |

0 |

–1.2 |

1.2 |

|

|

|

|

|

|

|

|

|

8 000 000 |

256 000 |

31 |

2 |

0 |

–0.8 |

1.6 |

–3.6 |

2.0 |

|

|

|

|

|

|

|

|

|

12 000 000 |

9600 |

1250 |

0 |

0 |

0 |

0 |

–0.05 |

0.05 |

|

|

|

|

|

|

|

|

|

12 000 000 |

19 200 |

625 |

0 |

0 |

0 |

0 |

–0.2 |

0 |

|

|

|

|

|

|

|

|

|

12 000 000 |

38 400 |

312 |

4 |

0 |

–0.2 |

0 |

–0.2 |

0.2 |

|

|

|

|

|

|

|

|

|

12 000 000 |

56 000 |

214 |

2 |

0 |

–0.3 |

0.2 |

–0.4 |

0.5 |

|

|

|

|

|

|

|

|

|

12 000 000 |

115 200 |

104 |

1 |

0 |

–0.5 |

0.6 |

–0.9 |

1.2 |

|

|

|

|

|

|

|

|

|

12 000 000 |

128 000 |

93 |

6 |

0 |

–0.8 |

0 |

–1.5 |

0.4 |

|

|

|

|

|

|

|

|

|

12 000 000 |

256 000 |

46 |

7 |

0 |

–1.9 |

0 |

–2.0 |

2.0 |

|

|

|

|

|

|

|

|

|

16 000 000 |

9600 |

1666 |

6 |

0 |

–0.05 |

0.05 |

–0.05 |

0.1 |

|

|

|

|

|

|

|

|

|

16 000 000 |

19 200 |

833 |

2 |

0 |

–0.1 |

0.05 |

–0.2 |

0.1 |

|

|

|

|

|

|

|

|

|

16 000 000 |

38 400 |

416 |

6 |

0 |

–0.2 |

0.2 |

–0.2 |

0.4 |

|

|

|

|

|

|

|

|

|

16 000 000 |

56 000 |

285 |

6 |

0 |

–0.3 |

0.1 |

–0.5 |

0.2 |

|

|

|

|

|

|

|

|

|

16 000 000 |

115 200 |

138 |

7 |

0 |

–0.7 |

0 |

–0.8 |

0.6 |

|

|

|

|

|

|

|

|

|

16 000 000 |

128 000 |

125 |

0 |

0 |

0 |

0 |

–0.8 |

0 |

|

|

|

|

|

|

|

|

|

16 000 000 |

256 000 |

62 |

4 |

0 |

–0.8 |

0 |

–1.2 |

1.2 |

|

|

|

|

|

|

|

|

|