MSP430_Final

.pdf

15.4. Регистры модуля USCI: режим UART 391

UC1IFG, регистр флагов прерываний модуля USCI_A1

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Unused |

Unused |

|

Unused |

Unused |

|

|

UCA1TXIFG |

UCA1RXIFG |

|

|

|

|

|

|

|

|

|

rw–0 |

rw–0 |

|

rw–0 |

rw–0 |

|

|

rw–1 |

rw–0 |

Unused |

Биты |

Не используются. |

|

|

|

|

||

|

7…4 |

|

|

|

|

|

|

|

|

Биты |

Эти биты могут использоваться другими модулями USCI. См доку |

||||||

|

3…2 |

ментацию на конкретный микроконтроллер. |

|

|

||||

UCA1TXIFG Бит 1 |

Флаг прерывания передачи модуля USCI_A1. Бит UCA1TXIFG уста |

|||||||

|

|

навливается при опустошении регистра UCA1TXBUF. |

|

|||||

|

|

0 Не было запроса прерывания |

|

|

|

|||

1Есть запрос прерывания

UCA1RXIFG Бит 0 Флаг прерывания приёма модуля USCI_A1. Бит UCA1RXIFG уста навливается при копировании принятого символа в регистр UCA1RXBUF.

0 Не было запроса прерывания

1Есть запрос прерывания

392 Глава 16. Универсальный последовательный коммуникационный интерфейс: режим SPI

ГЛАВА 16

УНИВЕРСАЛЬНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ КОММУНИКАЦИОННЫЙ ИНТЕРФЕЙС:

РЕЖИМ SPI

Модуль универсального последовательного коммуникационного интерфейса (USCI) поддерживает несколько режимов обмена по последовательному каналу. В этой главе описывается работа модуля в режиме последовательного периферий ного интерфейса SPI.

16.1. Введение

Модули универсального последовательного коммуникационного интерфейса (USCI) поддерживают несколько режимов передачи данных по последовательно му каналу, при этом разные модули USCI поддерживают различные режимы. Мо дули USCI имеют уникальное обозначение. Так, модуль USCI_A отличается от модуля USCI_B и т.д. Если в конкретном устройстве имеется более одного моду ля USCI с идентичными функциями, то в обозначение таких модулей добавляет ся порядковый номер. Например, если в устройстве имеется два модуля USCI_A, то они имеют обозначения USCI_A0 и USCI_A1. Чтобы узнать, какие именно мо дули USCI реализованы и реализованы ли вообще в конкретном микроконтрол лере, обратитесь к справочной документации.

Модули USCI_A поддерживают:

режим UART;

формирование импульсов для обмена по протоколу IrDA;

автоматическое определение скорости обмена для поддержки протокола LIN;

режим SPI.

Модули USCI_B поддерживают:

режим I2C;

режим SPI.

16.2. Введение в модуль USCI: режим SPI

В синхронном режиме для связи микроконтроллеров семейства MSP430 с внешним устройствам используется три или четыре вывода: UCxSIMO, UCxSOMI, UCxCLK и UCxSTE. Включение режима SPI осуществляется установ кой бита UCSYNC, а разновидность интерфейса SPI (3 или 4 проводный) опре деляется битами UCMODEx.

16.2. Введение в модуль USCI: режим SPI 393

Режим SPI имеет следующие особенности:

7 или 8 битные данные;

изменяемый порядок передачи и приёма битов;

поддержка 3 и 4 проводного интерфейса SPI;

поддержка режимов ведущего и ведомого;

независимые сдвиговые регистры передачи и приёма;

раздельные буферные регистры передачи и приёма;

поддержка непрерывной передачи и приёма;

возможность выбора полярности и фазы тактового сигнала;

программируемая частота тактового сигнала в режиме ведущего;

независимые прерывания передачи и приёма;

работа в качестве ведомого в режиме LPM4.

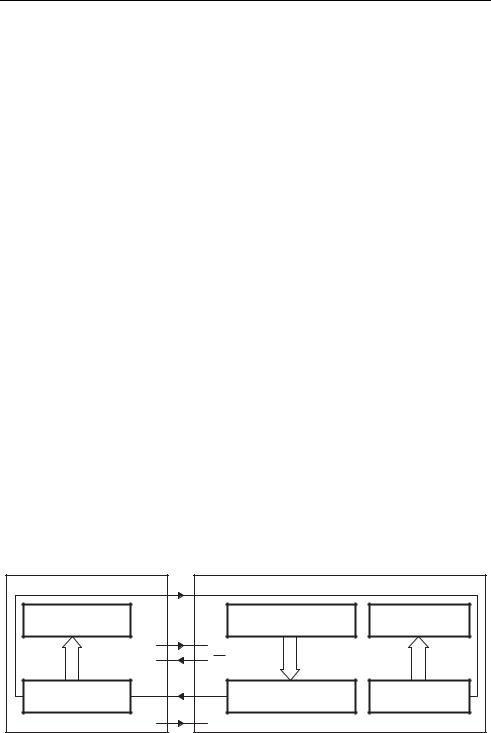

Блок схема модуля USCI, сконфигурированного для работы в режиме UART, |

||||||

приведена на Рис. 16.1. |

|

|

|

|||

|

|

|

Конечный автомат |

|

|

Установка UCOE |

|

|

|

приёмника |

|

|

Установка UCxRXIFG |

|

|

|

|

|

|

|

|

|

|

|

|

UCLISTEN |

UCMST |

|

|

|

Буфер приёма UCxRXBUF |

|

|

|

|

|

|

|

|

|

UCxSOMI |

|

|

|

|

|

0 |

1 |

|

|

|

Сдвиговый регистр |

|

0 |

|

|

|

|

|

|

||

|

|

|

приёма |

|

1 |

|

|

|

|

|

|

||

|

|

|

UCMSB |

UC7BIT |

|

|

|

UCSSELx |

Генератор тактового сигнала |

|

|

||

|

|

|

|

|

||

|

|

|

UCxBRx |

|

UCCKPH UCCKPL |

|

|

|

|

|

|

|

|

N/A |

00 |

BRCLK |

16 |

|

|

|

|

|

|

|

UCxCLK |

||

ACLK |

01 |

|

|

Направление, |

||

Предделитель/Делитель |

|

|||||

SMCLK |

10 |

|

фаза и полярность |

|

||

|

|

|

тактового сигнала |

|

||

|

|

|

|

|

|

|

SMCLK |

11 |

|

|

|

|

|

|

|

|

UCMSB |

UC7BIT |

|

|

|

|

|

Сдвиговый регистр |

|

|

UCxSIMO |

|

|

|

|

|

|

|

|

|

|

передачи |

|

UCMODEx |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

UCxSTE |

|

|

|

Буфер передачи UCxTXBUF |

|

||

|

|

|

|

|

||

|

|

|

|

|

Разрешение |

|

|

|

|

|

|

передачи |

|

|

|

|

Конечный автомат |

|

|

Установка UCFE |

|

|

|

|

|

|

|

|

|

|

передатчика |

|

|

Установка UCxTXIFG |

|

|

|

Рис. 16.1. Блок схема модуля USCI: режим SPI. |

|

||

394 Глава 16. Универсальный последовательный коммуникационный интерфейс: режим SPI

16.3. Функционирование модуля USСI: режим SPI

В режиме SPI последовательные данные передаются и принимаются различ ными устройствами с использованием общего тактового сигнала, генерируемого ведущим устройством. Дополнительный вывод UCxSTE, управляемый ведущим, используется, чтобы разрешать устройству приём и передачу данных.

Для обмена данными по интерфейсу SPI используются три или четыре сигнала:

UCxSIMO Вход ведомого, выход ведущего.

Режим ведущего: UCxSIMO — линия передачи данных Режим ведомого: UCxSIMO — линия приёма данных

UCxSOMI Выход ведомого, вход ведущего.

Режим ведущего: UCxSOMI — линия приёма данных Режим ведомого: UCxSOMI — линия передачи данных

UCxCLK Тактовый сигнал SPI.

Режим ведущего: UCxCLK — выход Режим ведомого: UCxCLK — вход

UCxSTE Разрешение передачи ведомым. Используется в 4 проводном режиме для поддержки нескольких ведущих устройств на одной шине. В 3 проводном ре жиме не используется. Разные варианты использования UCxSTE приведены в Табл. 16.1.

Таблица 16.1. Использование вывода UCxSTE

UCMODEx |

Активный уровень UCxSTE |

UCxSTE |

Ведомый |

Ведущий |

|

|

|

|

|

|

|

01 |

ВЫСОКИЙ |

0 |

Не активен |

Активен |

|

|

|

|

|||

1 |

Активен |

Не активен |

|||

|

|

||||

|

|

|

|

|

|

10 |

НИЗКИЙ |

0 |

Активен |

Не активен |

|

|

|

|

|||

1 |

Не активен |

Активен |

|||

|

|

||||

|

|

|

|

|

16.3.1. Инициализация и сброс модуля USCI

Модуль USCI сбрасывается по сигналу PUC или в результате установки бита USCSWRST. При появлении сигнала PUC бит USCSWRST автоматически уста навливается, переводя модуль в состояние сброса. При установке бита USCSWRST сбрасываются биты UCxRXIE, UCxTXIE, UCxRXIFG, UCOE, UCFE и устанавливается бит UCxTXIFG. Сброс бита USCSWRST переводит мо дуль USCI в рабочий режим.

Примечание. Инициализация и реконфигурирование модуля USCI

Инициализацию и реконфигурирование модуля USCI рекомендуется выполнять в

следующей последовательности:

1. Установить бит UCSWRST (BIS.B #UCSWRST,&UCxCTL1).

2.Инициализировать все регистры USCI установкой UCSWRST = 1 (включая ре гистр UCxCTL1).

3.Сконфигурировать порты ввода/вывода.

4. Сбросить в программе бит UCSWRST (BIС.B #UCSWRST,&UCxCTL1).

5.Разрешить прерывания (при необходимости) установкой битов UCxRXIE и/или UCxTXIE.

16.3. Функционирование модуля USСI: режим SPI 395

16.3.2. Формат символа

Врежиме SPI модуль USCI поддерживает 7 и 8 битные символы, что опреде ляется битом UC7BIT.

В7 битном режиме содержимое регистра UCxRXBUF выравнивается по младшему биту, а старший бит регистра всегда сброшен. Порядок передачи битов символа определяется битом UCMSB.

Примечание. Формат символа по умолчанию

По умолчанию, данные в режиме SPI передаются начиная с младшего значащего бита. Однако существуют реализации интерфейса SPI, требующие передачи дан ных начиная со старшего бита.

16.3.3. Режим ведущего

На Рис. 16.2 показано использование модуля USCI в качестве ведущего в обе их (3 и 4 проводной) конфигурациях. Передача данных инициируется модулем USCI при загрузке значения в регистр буфера передачи UCxTXBUF. Если сдви говый регистр передачи пуст, то содержимое буфера пересылается в него, запус кая побитовую выдачу символа на вывод UCxSIMO, начиная со старшего или младшего бита, в зависимости от значения бита UCMSB. Данные, поступающие на вывод UCxSOMI, вдвигаются в сдвиговый регистр приёма по противополож ному фронту тактового сигнала. После приёма заданного числа битов полученное значение пересылается из сдвигового регистра в буфер приёма UCxRXBUF. Од новременно устанавливается флаг прерывания приёма UCxRXIFG, сигнализиру ющий об окончании процесса приёма/передачи.

Установка флага прерывания передачи UCxTXIFG извещает о том, что дан ные были перемещены из буфера UCxTXBUF в сдвиговый регистр передачи и что буфер готов к приёму новых данных. Этот флаг никак не связан с завершением операции приёма/передачи.

Для приёма данных в режиме ведущего, необходимо записать что либо в регистр UCxTXBUF, поскольку операции приёма и передачи выполняются одновременно.

|

ВЕДУЩИЙ |

UCxSIMO |

SIMO |

|

ВЕДОМЫЙ |

|

|

|

|

|

|

||

Буфер приёма |

|

Буфер передачи |

|

|

Буфер приёма SPI |

|

UCxRXBUF |

|

UCxTXBUF |

|

|

||

|

|

|

|

|

||

|

|

|

Px.x |

STE |

|

|

|

|

UCxSTE |

SS |

|

|

|

|

|

Port.x |

|

|||

|

|

|

|

|

||

|

|

|

UCx |

SOMI |

|

|

Сдвиговый регистр |

|

Сдвиговый регистр |

SOMI |

Сдвиговый регистр |

||

приёма |

|

передачи |

|

|

|

данных (DSR) |

MSP430 USCI |

UCxCLK |

SCLK |

SPI устройство |

|||

|

|

|

|

|||

Рис. 16.2. Модуль USCI в режиме ведущего и внешнее ведомое устройство. |

||||||

396 Глава 16. Универсальный последовательный коммуникационный интерфейс: режим SPI

Работа ведущего в 4Cпроводном режиме

В4 проводном режиме вывод UCxSTE используется для предотвращения конфликтов с другими ведущими устройствами, подключёнными к шине, и уп равляет работой ведущего в соответствии с Табл. 16.1. Когда сигнал на выводе UCxSTE переводит ведущего в неактивное состояние:

выводы UCxSIMO и UCxSCLK переключаются на вход и не влияют на со стояние шины;

устанавливается флаг ошибки UCFE, сигнализирующий о нарушении целос тности процесса обмена, чтобы пользователь мог обработать эту ситуацию;

внутренний конечный автомат модуля сбрасывается и процесс сдвига прерывается.

Вслучае загрузки данных в регистр UCxTXBUF в то время, пока ведущий удерживается в неактивном состоянии сигналом UCxSTE, эти данные будут пе реданы сразу же, как только сигнал UCxSTE переведёт ведущего в активное со стояние. Если текущая пересылка была прервана сигналом UCxSTE, то для пов торной передачи этих данных после возврата модуля в активное состояние их не обходимо снова загрузить в регистр UCxTXBUF. При работе ведущего в 3 проводном режиме сигнал UCxSTE не используется.

16.3.4. Режим ведомого

На Рис. 16.3 показано использование модуля USCI в качестве ведомого в обе их (3 и 4 проводной) конфигурациях. Вывод UCxCLK является входом для так тового сигнала SPI, который должен генерироваться ведущим устройством. Ско рость пересылки данных определяется параметрами этого сигнала и не зависит от настроек внутреннего генератора тактового сигнала. При появлении сигнала UCxCLK данные, загруженные в регистр UCxTXBUF и перемещённые в сдвиго вый регистр передачи, побитно выдаются на вывод UCxSOMI. Данные, поступа ющие на вывод UCxSMO, вдвигаются в сдвиговый регистр приёма по противопо ложному фронту тактового сигнала. После приёма заданного числа битов полу ченное значение пересылается из сдвигового регистра в буфер приёма UCxRXBUF. Одновременно устанавливается флаг прерывания UCxRXIFG, сиг нализирующий о появлении новых данных. Если ранее принятые данные не бы ли считаны из регистра UCxRXBUF перед загрузкой в него новых данных из сдвигового регистра, то устанавливается флаг переполнения UCOE.

ВЕДУЩИЙ |

SIMO |

UCxSIMO |

|

ВЕДОМЫЙ |

Буфер приёма SPI |

|

|

Буфер передачи |

Буфер приёма |

|

|

UCxTXBUF |

UCxRXBUF |

|

|

|

|

||

|

Px.x |

UCxSTE |

|

|

|

STE |

SS Port.x |

|

|

|

|

UCx |

|

|

Сдвиговый регистр |

SOMI |

SOMI |

Сдвиговый регистр |

Сдвиговый регистр |

данных (DSR) |

|

|

передачи |

приёма |

SPI устройство |

SCLK |

UCxCLK |

MSP430 USCI |

|

Рис. 16.3. Модуль USCI в режиме ведомого и внешнее ведущее устройство. |

||||

16.3. Функционирование модуля USСI: режим SPI 397

Работа ведомого в 4Cпроводном режиме

В 4 проводном режиме вывод UCxSTE используется, чтобы разрешать или за прещать ведомому выполнение операций приёма/передачи данных. Управляется этот вывод ведущим устройством. Когда уровень сигнала UCxSTE соответствует активному состоянию ведомого, последний работает в обычном режиме. Когда же сигнал UCxSTE переводит ведомого в неактивное состояние:

приём данных, поступающих на вход UCxSIMO, прекращается;

вывод UCxSOMI переключается на вход;

операции сдвига прекращаются до тех пор, пока на линии UCxSTE не поя вится сигнал, соответствующий активному состоянию ведомого устройства.

При работе ведомого в 3 проводном режиме сигнал UCxSTE не используется.

16.3.5. Разрешение обмена по интерфейсу SPI

После включения модуля USCI сбросом бита UCSWRST приёмник и передат чик модуля готовы к работе. В режиме ведущего генератор тактового сигнала на ходится в состоянии готовности, но сигнал не генерирует, поскольку задающий тактовый сигнал на него не поступает. В режиме ведомого генератор тактового сигнала отключён, а сигнал синхронизации поступает от ведущего устройства.

Признаком выполнения операции приёма или передачи является установлен ный бит UCBUSY.

При появлении сигнала системного сброса PUC или при установке бита UCSWRST модуль USCI сразу же выключается, и текущая пересылка данных прерывается.

Разрешение передачи

Врежиме ведущего запись в регистр UCxTXBUF запускает генератор такто вого сигнала, в результате чего начинается передача данных.

Врежиме ведомого передача начинается при появлении тактового сигнала от ведущего и, в 4 проводной конфигурации, при наличии на выводе UCxSTE сиг нала, соответствующего активному состоянию ведомого.

Разрешение приёма

Приём данных по интерфейсу SPI осуществляется при включении передатчи ка. Операции приёма и передачи выполняются одновременно.

16.3.6. Управление тактовым сигналом

Тактовый сигнал на шине SPI формируется ведущим устройством. При UCMST = 1 сигнал от генератора тактового сигнала модуля USCI выводится на вывод UCxCLK. Исходный сигнал, из которого формируется тактовый сигнал SPI, задаётся битами UCSSELx. При UCMST = 0 тактовый сигнал для модуля USCI поступает на вывод UCxCLK от ведущего устройства. Генератор тактового сигнала модуля при этом не используется и состояние битов UCSSELx безразлич

16.3. Функционирование модуля USСI: режим SPI 399

энергопотребления. Если модуль USCI тактируется сигналом SMCLK, который неактивен по причине нахождения устройства в режиме пониженного энергопот ребления, то модуль автоматически активирует этот тактовый сигнал при необхо димости, независимо от значений управляющих битов выбора источника систем ного тактового сигнала. Данный тактовый сигнал будет активным до тех пор, по ка модуль USCI не вернётся в состояние ожидания. После этого контроль над источником тактового сигнала вернётся к модулю синхронизации. Автоматичес кая активация тактового сигнала ACLK не предусмотрена.

При активации модулем USCI неактивного источника тактового сигнала, этот источник становится доступным для всего устройства, так что его активация может затронуть любой периферийный модуль, сконфигурированный для ис пользования данного тактового сигнала. Например, значение таймера, использу ющего SMCLK, будет инкрементироваться в течение всего времени, пока модуль USCI будет находиться в активном режиме.

В режиме ведомого SPI наличие внутреннего тактового сигнала не требуется, поскольку сигнал синхронизации формируется внешним ведущим устройством. Это даёт возможность использовать модуль USCI в качестве ведомого SPI уст ройства даже при использовании режима пониженного энергопотребления LPM4, в котором выключены все источники тактовых сигналов.

16.3.8. Прерывания в режиме SPI

Модуль USCI имеет по одному вектору прерывания для передачи и приёма.

Прерывание SPI при передаче

Флаг прерывания UCxTXIFG, устанавливаемый передатчиком, показывает готовность регистра UCxTXBUF к загрузке нового символа. Если установлены биты GIE и UCxTXIE, то при установке флага UCxTXIFG генерируется запрос прерывания. Флаг UCxTXIFG автоматически сбрасывается при записи в регистр UCxTXBUF. Флаг UCxTXIFG устанавливается после сигнала сброса PUC или при UCSWRST = 1. Бит разрешения прерывания UCxTXIE сбрасывается после сигнала сброса PUC или при UCSWRST = 1.

Примечание. Запись в регистр UCxTXBUF в режиме SPI

Запись в регистр UCxTXBUF при UCxTXIFG = 0 может вызвать передачу некор ректных данных.

Прерывание SPI при приёме

Флаг прерывания UCxRXIFG устанавливается каждый раз при приёме сим вола и загрузке его в регистр UCxRXBUF. При установленных битах GIE и UCxRXIE генерируется запрос прерывания. Биты UCxRXIFG и UCxRXIE сбра сываются сигналом системного сброса PUC или при UCSWRST = 1. Флаг UCxRXIFG автоматически сбрасывается при чтении регистра UCxRXBUF.

400 Глава 16. Универсальный последовательный коммуникационный интерфейс: режим SPI

Использование прерываний модуля USCI

Модули USCI_Ax и USCI_Bx используют одни и те же векторы прерываний. Флаги прерываний приёма UCAxRXIFG и UCBxRXIFG связаны с одним векто ром прерываний, тогда как флаги прерываний передачи UCAxTXIFG и UCBxTXIFG связаны с другим вектором.

Примеры использования разделяемого вектора прерывания

В следующем примере содержится фрагмент процедуры обработки прерыва ния, отвечающей за обработку прерываний приёма модуля USCI_A0, работающе го в режиме UART или SPI, и модуля USCI_B0, работающего в режиме SPI.

USCIA0_RX_USCIB0_RX_ISR

BIT.B #UCA0RXIFG, &IFG2 ; Прерывание приёма USCI_A0? JNZ USCIA0_RX_ISR

USCIB0_RX_ISR?

; Читаем UCB0RXBUF (сбрасывается UCB0RXIFG)

...

RETI USCIA0_RX_ISR

; Читаем UCA0RXBUF (сбрасывается UCA0RXIFG)

...

RETI

В следующем примере содержится фрагмент процедуры обработки прерыва ния, отвечающей за обработку прерываний передачи модуля USCI_A0, работаю щего в режиме UART или SPI, и модуля USCI_B0, работающего в режиме SPI.

USCIA0_TX_USCIB0_TX_ISR

BIT.B #UCA0TXIFG, &IFG2 ; Прерывание передачи USCI_A0? JNZ USCIA0_TX_ISR

USCIB0_TX_ISR

; Пишем в UCB0TXBUF (сбрасывается UCB0TXIFG)

...

RETI USCIA0_TX_ISR

; Пишем в UCA0TXBUF (сбрасывается UCA0TXIFG)

...

RETI