MSP430_Final

.pdf

6.3. Регистры контроллера DMA 261

DMA Биты Инкремент конечного адреса. Эти биты разрешают автоматическое DSTINRx 11…10 декрементирование/инкрементирование адреса приёмника после пересылки очередного байта или слова. При DMADSTBYTE = 1 ад рес приёмника увеличивается/уменьшается на единицу. При DMADSTBYTE = 0 адрес приёмника увеличивается/уменьшается на два. Регистр DMAxDA копируется во временный регистр, содержи мое которого инкрементируется или декрементируется. Сам регистр

DMAxDA не изменяется.

00 Адрес приёмника не изменяется

01 Адрес приёмника не изменяется

|

|

10 |

Адрес приёмника декрементируется |

|

|

11 |

Адрес приёмника инкрементируется |

DMA |

Биты |

Инкремент исходного адреса. Эти биты разрешают автоматическое |

|

SRCINCRx |

9…8 |

декрементирование/инкрементирование адреса источника после пе |

|

|

|

ресылки очередного байта или слова. При DMADSTBYTE = 1 адрес |

|

|

|

источника увеличивается/уменьшается на единицу. При |

|

|

|

DMADSTBYTE = 0 адрес источника увеличивается/уменьшается на |

|

|

|

два. Регистр DMAxSA копируется во временный регистр, содержи |

|

|

|

мое которого инкрементируется или декрементируется. Сам регистр |

|

|

|

DMAxSA не изменяется. |

|

|

|

00 |

Адрес источника не изменяется |

|

|

01 |

Адрес источника не изменяется |

|

|

10 |

Адрес источника декрементируется |

|

|

11 |

Адрес источника инкрементируется |

DMA |

Бит 7 Формат приёмника DMA. Этот бит определяет разрядность приёмника. |

||

DSTBYTE |

|

0 |

Слово |

|

|

1 |

Байт |

DMA |

Бит 6 Формат источника DMA. Этот бит определяет разрядность источника. |

||

SRCBYTE |

|

0 |

Слово |

|

|

1 |

Байт |

DMALEVEL Бит 5 Уровень DMA. Этот бит определяет характер сигнала запуска. 0 Запуск по фронту (нарастающий фронт)

|

|

1 |

Запуск по уровню (ВЫСОКИЙ уровень) |

DMAEN |

Бит 4 |

Разрешение DMA. |

|

|

|

0 |

Выключен |

|

|

1 |

Включен |

DMAIFG |

Бит 3 Флаг прерывания DMA. |

||

|

|

0 |

Нет прерывания |

|

|

1 |

Есть прерывание |

DMAIE |

Бит 2 |

Разрешение прерывания DMA |

|

|

|

0 |

Запрещено |

|

|

1 |

Разрешено |

DMA |

Бит 1 |

Аварийный останов DMA. Этот бит показывает, была ли DMA пере |

|

ABORT |

|

сылка прервана немаскируемым прерыванием. |

|

|

|

0 |

DMA пересылка не прервана |

|

|

1 |

DMA пересылка была прервана NMI |

DMAREQ |

Бит 0 |

Запрос DMA. Программный запуск DMA. Бит DMAREQ сбрасыва |

|

|

|

ется автоматически. |

|

|

|

0 |

Не запускать DMA |

|

|

1 |

Запустить DMA |

262 Глава 6. Контроллер DMA

DMAxSA, регистр адреса источника канала x DMA

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

r0 |

r0 |

r0 |

r0 |

|

r0 |

r0 |

r0 |

r0 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

||

|

Reserved |

|

|

|

DMAxSAx |

|

||

|

|

|

|

|

|

|

|

|

r0 |

r0 |

r0 |

r0 |

|

rw |

rw |

rw |

rw |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

|

|

|

|

|

||

|

|

|

DMAxSAx |

|

|

|

||

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

|

rw |

rw |

rw |

rw |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

||

|

|

|

DMAxSAx |

|

|

|

||

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

|

rw |

rw |

rw |

rw |

DMAxSAx |

Биты |

Адрес источника DMA. Регистр адреса источника указывает на адрес ис |

||||||

|

15…0 ходного значения для режима одиночных пересылок или на адрес перво |

|||||||

|

|

го значения исходного блока данных для режимов пересылки блоков. |

||||||

Вмоделях, содержащих не более 64 КБ адресуемой памяти, в регист ре DMAxSAx используется одно слово. При записи в старшее слово с использованием команд, оперирующих 2 байтными операндами, это слово автоматически обнуляется.

Вмоделях, имеющих более 64 КБ адресуемой памяти, для хранения адреса источника используется дополнительное слово. Биты 15…4 этого слова зарезервированы и всегда читаются как 0. При операциях записи в регистр DMAxSAx с использованием команд, оперирующих 2 байтными операндами, это дополнительное слово автоматически обнуляется. При чтении дополнительного слова с использованием команд, оперирующих 2 байтными операндами, всегда возвращает ся нулевое значение.

6.3. Регистры контроллера DMA 263

DMAxDA, регистр адреса приёмника канала x DMA

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

|

|

Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

r0 |

r0 |

r0 |

r0 |

|

r0 |

r0 |

r0 |

r0 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

||

|

Reserved |

|

|

|

DMAxDAx |

|

||

|

|

|

|

|

|

|

|

|

r0 |

r0 |

r0 |

r0 |

|

rw |

rw |

rw |

rw |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

|

|

|

|

|

||

|

|

|

DMAxDAx |

|

|

|

||

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

|

rw |

rw |

rw |

rw |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

||

|

|

|

DMAxDAx |

|

|

|

||

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

|

rw |

rw |

rw |

rw |

DMAxDAx |

Биты |

Адрес приёмника DMA. Регистр адреса приёмника указывает на итого |

||||||

|

15…0 вый адрес значения для режима одиночных пересылок или на адрес пер |

|||||||

|

|

вого значения итогового блока данных для режимов пересылки блоков. |

||||||

Вмоделях, содержащих не более 64 КБ адресуемой памяти, для ре гистра DMAxDAx используется одно слово. При записи в старшее слово с использованием команд, оперирующих 2 байтными операн дами, это слово автоматически обнуляется.

Вмоделях, имеющих более 64 КБ адресуемой памяти, для хранения адреса источника используется дополнительное слово. Биты 15…4 этого слова зарезервированы и всегда читаются как 0. При операциях записи в регистр DMAxDAx с использованием команд, оперирую щих 2 байтными операндами, это дополнительное слово автомати чески обнуляется. При чтении дополнительного слова с использова нием команд, оперирующих 2 байтными операндами, всегда возвращается нулевое значение.

264 Глава 6. Контроллер DMA

DMAxSZ, регистр размера пересылки канала x DMA

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

|

|

|

DMAxSZx |

|

|

|

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

rw |

rw |

rw |

rw |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

DMAxSZx |

|

|

|

|

|

|

|

|

|

|

|

|

rw |

rw |

rw |

rw |

rw |

rw |

rw |

rw |

DMAxSZx Биты Размер пересылки DMA. Этот регистр определяет количество бай 15…0 тов/слов в пересылаемом блоке. Содержимое регистра DMAxSZx де крементируется после пересылки каждого слова или байта. При до стижении нулевого значения в регистр DMAxSZ автоматически

загружается его исходное содержимое. 00000h Пересылка запрещена

00001h Необходимо переслать один байт или слово

00002h Необходимо переслать два байта или слова

:

0FFFFh Необходимо переслать 65535 байтов или слов

DMAIV, регистр вектора прерывания контроллера DMA

15 |

14 |

|

13 |

12 |

|

11 |

|

10 |

|

9 |

8 |

|||||

0 |

0 |

|

|

0 |

0 |

|

0 |

|

0 |

|

0 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

r0 |

r0 |

|

r0 |

|

r0 |

|

r0 |

|

|

r0 |

|

r0 |

|

r0 |

||

7 |

6 |

|

5 |

4 |

|

3 |

|

2 |

|

1 |

0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

0 |

|

|

0 |

0 |

|

|

|

DMAIVx |

|

|

|

0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

r0 |

r0 |

|

r0 |

|

r0 |

|

r (0) |

|

r (0) |

r (0) |

|

r0 |

||||

DMAIVx |

Биты |

Значение вектора прерывания DMA |

|

|

|

|

|

|

|

|||||||

|

15…0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Содержимое |

|

Источник прерывания |

|

Флаг |

|

|

Приоритет |

|||||||

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

DMAIV |

|

|

прерывания |

|

|

прерывания |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

00h |

|

Нет прерывания |

|

— |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

02h |

|

Канал 0 DMA |

|

|

|

DMA0IFG |

|

|

Высший |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

04h |

|

Канал 1 DMA |

|

|

|

DMA1IFG |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

06h |

|

Канал 2 DMA |

|

|

|

DMA2IFG |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

08h |

|

Зарезервировано |

|

— |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

0Ah |

|

Зарезервировано |

|

— |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

0Ch |

|

Зарезервировано |

|

— |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

0Fh |

|

Зарезервировано |

|

— |

|

|

Низший |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7.1. Введение 265

ГЛАВА 7

КОНТРОЛЛЕР ФЛЭШCПАМЯТИ

В этой главе описывается функционирование контроллера флэш памяти микроконтроллеров семейства MSP430x2xx.

7.1.Введение

В микроконтроллерах семейства MSP430 флэш память может адресоваться и записываться побитно, побайтно или пословно. Модуль флэш памяти имеет собственный контроллер, управляющий операциями программирования и стира ния памяти. Контроллер имеет четыре регистра, тактовый генератор, а также ге нератор напряжения, формирующий напряжения, необходимые для выполнения операций записи и стирания.

Контроллер флэш памяти имеет следующие особенности:

встроенный генератор напряжения программирования;

побитовое, побайтовое или пословное программирование;

сверхмалое потребление;

поддерживается стирание сегментов и общее стирание;

два режима чтения при граничных условиях (опционально, см. документа

цию на конкретную модель).

Блок схема контроллера флэш памяти приведена на Рис. 7.1.

Примечание. Минимальное значение VCC при записи и стирании флэш памяти

Минимальное значение напряжения питания VCC во время операций записи или стирания флэш памяти составляет 2.2 В. Если в процессе записи или стирания флэш памяти напряжение VCC снизится ниже 2.2 В, результат операции будет не предсказуем.

7.2.Сегментная организация флэшCпамяти

В микроконтроллерах MSP430 вся флэш память поделена на сегменты. Запи сывать в флэш память можно отдельные биты, байты или же слова, однако наи меньшей единицей флэш памяти, которую можно стереть, является сегмент.

Кроме того, флэш память содержит две секции — основную и информацион ную. Обе секции функционируют совершенно одинаково. И программный код, и данные могут располагаться в обеих секциях. Различие между этими секциями заключается в разных значениях размера сегмента и физических адресов.

266 Глава 7. Контроллер флэш#памяти |

|

|

MAB |

|

MDB |

|

|

|

FCTL1 |

Защёлка адреса |

Защёлка данных |

FCTL2 |

Включение |

|

|

|

|

|

защёлки |

|

|

адреса |

|

FCTL3 |

|

|

|

|

Матрица |

|

|

флэш памяти |

FCTL4 |

|

|

Тактовый |

|

|

генератор |

Включение |

|

|

защёлки данных |

|

Генератор

напряжения

программирования

Рис. 7.1. Блок схема контроллера флэш памяти.

0x0FFFF |

|

0x0FFFF |

Сегмент 0 |

0x0FFFF |

Блок |

|

32 КБ |

0x0FB00 |

0x0FFC0 |

||

|

0x0FDFF |

Сегмент 1 |

0x0FFBF |

Блок |

|

|

основной |

0x0FC00 |

0x0FF80 |

||

|

флэш памяти |

|

Сегмент 2 |

0x0FF7F |

Блок |

|

|

|

0x0FF40 |

||

|

|

|

|

|

|

|

|

|

|

OxOFF3F |

Блок |

0x0F000 |

|

|

|

0x0FF00 |

|

|

|

|

|

||

|

|

|

|

0x0FEFF |

Блок |

0x010FF |

512 байт |

|

|

OxOFBC0 |

|

|

|

|

|||

|

информационной |

|

Сегмент 61 |

0x0FEBF |

Блок |

|

|

OxOFE80 |

|||

|

флэш памяти |

|

|

|

|

0x01000 |

|

Сегмент 62 |

OxOFE7F |

Блок |

|

|

|

||||

|

|

|

OxOFE40 |

||

|

|

|

|

|

|

|

|

|

Сегмент 63 |

0x0FE3F |

Блок |

|

|

0x08000 |

0x0FE00 |

||

|

|

0x010FF |

Сегмент A |

|

|

|

|

|

Сегмент B |

|

|

Сегмент C

0x01000 Сегмент D

Рис. 7.2. Сегментная организация флэш памяти (для модуля объёмом 32 КБ).

7.3. Функционирование флэш#памяти 267

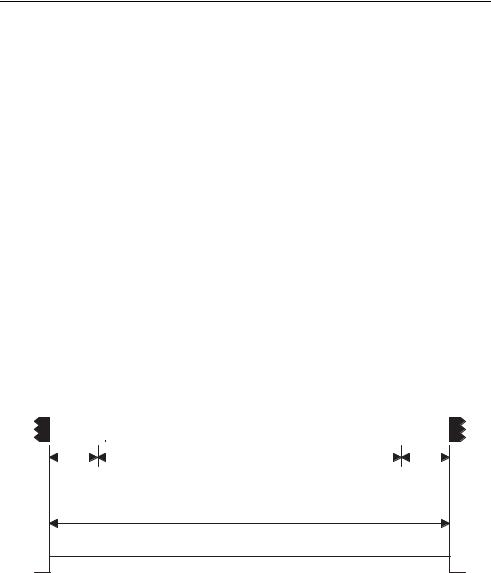

Информационная секция содержит четыре 64 байтных сегмента, в то время как основная секция содержит два или более сегментов размером 512 байт. Пол ная карта памяти конкретного устройства приводится в его справочной докумен тации.

Сегменты, в свою очередь, поделены на блоки.

На Рис. 7.2 показана сегментная организация модуля флэш памяти объёмом 32 КБ, который имеет 8 основных и четыре информационных сегмента.

7.2.1. Сегмент A

Сегмент A информационной секции флэш памяти может быть заблокирован независимо от остальных секций посредством бита LOCKA. При LOCKA = 1 за пись или стирание сегмента A запрещены, а всё содержимое информационной секции защищено от стирания при выполнении операции общего стирания или при программировании микроконтроллера. При LOCKA = 0 запись и стирание сегмента A осуществляются наравне с любыми другими секциями флэш памяти, а содержимое информационной секции при выполнении общего стирания или при программировании микроконтроллера стирается.

Состояние бита LOCKA изменяется записью в него 1. Запись 0 в бит LOCKA не изменяет его состояния. Это позволяет использовать без изменений существу ющие процедуры программирования флэш памяти.

; Разблокировать сегмент A |

|

|

BIT |

#LOCKA,&FCTL3 |

; Проверяем LOCKA |

JZ |

SEGA_UNLOCKED |

; Уже разблокировано? |

MOV |

#FWKEY+LOCKA,&FCTL3 |

; Нет, разблокируем сегмент |

SEGA_UNLOCKED |

; Да, продолжаем |

|

;Сегмент A разблокирован

;Заблокировать сегмент A

BIT |

#LOCKA,&FCTL3 |

; Проверяем LOCKA |

JNZ |

SEGALOCKED |

; Уже заблокировано? |

MOV |

#FWKEY+LOCKA,&FCTL3 |

; Нет, блокируем сегмент |

SEGA_LOCKED |

; Да, продолжаем |

|

; Сегмент A заблокирован |

|

|

7.3.Функционирование флэшCпамяти

По умолчанию флэш память находится в режиме для чтения. В этом режиме стирание или запись флэш памяти заблокированы, а тактовый генератор и гене ратор напряжения выключены — память работает подобно ПЗУ.

Флэш память семейства MSP430 поддерживает внутрисхемное программиро вание (ISP) и не требует дополнительного источника напряжения. Центральный процессор может осуществлять программирование собственной флэш памяти. Посредством битов BLKWRT, WRT, MERAS и ERASE могут быть выбраны сле дующие режимы записи/стирания флэш памяти:

запись байта/слова;

запись блока;

268Глава 7. Контроллер флэш#памяти

стирание сегмента;

общее стирание (стирание всех сегментов основной секции памяти);

полное стирание (стирание всей памяти).

Чтение или запись флэш памяти во время её программирования или стира ния запрещены. Если во время записи или стирания памяти требуется выполне ние программы, то исполняемый код должен располагаться в ОЗУ. Процесс из менения флэш памяти может быть инициирован как из флэш памяти, так и из ОЗУ.

7.3.1. Тактовый генератор контроллера флэшCпамяти

Операции записи и стирания управляются тактовым генератором контролле ра, блок схема которого приведена на Рис. 7.3. Рабочая частота тактового генера тора fFTG должна находиться в диапазоне от ~257 кГц до ~476 кГц (см. документа цию на конкретный микроконтроллер).

|

FSSELx |

FN5 ........... |

|

|

|

|

|

|

|

|

|

||||

ACLK |

|

|

|

|

FN0 |

PUC |

EMEX |

||||||||

|

|

|

|

||||||||||||

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

00 |

|

|

|

|

|

fFTG |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

MCLK |

|

01 |

|

Делитель, 1…64 |

|

Сброс |

|||||||||

|

|

||||||||||||||

SMCLK |

|

10 |

|

|

Тактовый генератор контроллера |

||||||||||

|

|

|

|

|

|

|

|||||||||

SMCLK |

|

11 |

|

|

|

|

|

|

флэш памяти |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUSY |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

WAIT |

|||||

Рис. 7.3. Блок схема тактового генератора контроллера флэш памяти.

Выбор опорного сигнала тактового генератора контроллера флэшCпамяти

Тактовый генератор контроллера флэш памяти может тактироваться от любо го из тактовых сигналов ACLK, SMCLK или MCLK. Из выбранного сигнала пос редством делителя, коэффициент деления которого задаётся битами FNx, фор мируется тактовый сигнал контроллера fFTG. Если во время операции записи или стирания частота этого сигнала будет отличаться от указанной в спецификации, то результат операции может оказаться непредсказуемым или же рабочие пара метры флэш памяти могут выйти за пределы, гарантирующие надёжную работу.

При обнаружении неисправности тактового генератора во время операции за писи или стирания данная операция прерывается и устанавливается флаг FAIL. Результат операции при этом будет непредсказуемым.

Во время выполнения операции записи или стирания выбранный источник тактового сигнала нельзя выключить, переведя MSP430 в режим пониженного энергопотребления. Этот источник останется в активном состоянии до заверше ния операции, после чего будет выключен.

270 Глава 7. Контроллер флэш#памяти

программы, расположенной в флэш памяти, все временные параметры опреде ляются контроллером флэш памяти, а работа ЦПУ приостанавливается до окон чания операции. После завершения цикла стирания центральный процессор во зобновляет выполнение программы, начиная с команды, следующей за командой фиктивной записи.

При инициации цикла стирания из программы, расположенной в флэш па мяти, возможно стирание фрагмента кода программы, который должен был вы полняться после стирания. При возникновении такой ситуации поведение ЦПУ после завершения операции стирания будет непредсказуемым.

Последовательность операций, требуемая для запуска цикла стирания из про граммы, находящейся в флэш памяти, показана на Рис. 7.5.

Запретить сторожевой таймер

Настроить контроллер флэш памяти и задать режим стирания

Выполнить фиктивную запись

Установить LOCK = 1, разрешить сторожевой таймер

Рис. 7.5. Запуск цикла стирания из флэш памяти.

;Стирание сегмента из флэш$памяти. 514 кГц < SMCLK < 952 кГц

;Предполагается, что ACCVIE = NMIIE = OFIE = 0.

MOV #WDTPW+WDTHOLD,&WDTCTL |

; Запрещаем WDT |

MOV #FWKEY+FSSEL1+FN0,&FCTL2 |

; SMCLK/2 |

MOV #FWKEY,&FCTL3 |

; Сбрасываем LOCK |

MOV #FWKEY+ERASE,&FCTL1 |

; Разрешаем стирание сегмента |

CLR &0FC10h |

; Фиктивная запись, стираем сегмент 1 |

MOV #FWKEY+LOCK,&FCTL3 |

; Выполнено, устанавливаем LOCK |

... |

; Повторно разрешаем WDT? |

Запуск процедуры стирания из программы, расположенной в ОЗУ

Любой цикл стирания может быть инициирован из программы, расположен ной в ОЗУ. В этом случае ЦПУ не останавливается, а продолжает исполнять код программы из ОЗУ. Обращение ЦПУ по любому адресу флэш памяти допускает ся только после завершения цикла стирания, что определяется по состоянию би та BUSY. Попытка обращения к флэш памяти при BUSY = 1 приведёт к наруше нию доступа с последующей установкой флага ACCVIFG, а результат стирания окажется неопределённым.

Последовательность операций, требуемая для запуска цикла стирания из про граммы, находящейся в ОЗУ, показана на Рис. 7.6.