КЛ_АВС

.pdfПри динамическом предсказании переходов принимается решение, которое было принято при выполнении прошлых команд, и эта информация используется для предсказания вероятного поведения следующей команды перехода. Направление для снижения за двумя ближайшими во времени переходами, может быть использован прямой конечный автомат четырьмя состояниями. Более распространённый подход принятый в современных процессорах, заключается использовании специального буфера – Branch Target Buffer. Этот буфер хранит адрес каждого перехода и счётчик, отражающий историю его поведения. Обычно эта история записывается при помощи 2ух бит, был ли принят переход. Когда команда ветвления встречается первый раз, оба бита равны нулю (нет знаний о её поведении), если один из битов равен единице, то выбран один из типов поведения команды. Если оба бита равны единице, то команда имеет предсказуемое поведение и должно применяться статическое предсказание переходов.

Другой подход заключается в использовании 2ух потоков команд. Тогда слоты задержки могут заполняться независимыми командами из разных потоков.

Ещё один подход заключается в совместном использовании статического и динамического предсказания переходов, путём использования статистики выполнения переходов во время выполнения программы и передачи этой информации компилятору. Повторная компиляция даёт эффективный код.

Обработка исключительных ситуаций

Обработка исключительных ситуаций более сложная задача, чем обработка ветвлений. Такие события, как переполнение, ввод/вывод, остановка, подкачка новых страниц кеш-памяти, могут возникать в случайный момент времени, причём некоторые из этих событий возникают асинхронно. Но распознавание их часто откладывается до момента окончания очередного такта работы. Некоторое исключительные ситуации могут возникать, непосредственно, во время выполнения команд. Например, команда загрузки из памяти может порождать исключения, говорящие о необходимости подкачки новой страницы. Типичный способ обработки такой ситуации заключается в откате выполнения команды, т.о., что загрузка значений из памяти, так же, как и следующая за ней команда должны быть выполнены заново, после того, как произойдёт обработка исключительной ситуации. Однако если последовательность выполнения команд была изменена в процессе обработки, то простой откат назад не позволит восстановить состояние конвейера для искомой последовательности. В связи с этим необходимо сохранить дополнительную информацию о состоянии процессора, который позволит восстановить исходную последовательность команд. В частности для этого требуется больше одного счётчика команд. Для других типов прерываний, например, для прерывания по

71

исключительной ситуации плавающей точки, команда вызывающая прерывание на некоторых машинах записывает свои результаты ещё до того момента, когда прерывание может быть обработано. В этих случаях аппаратура должна быть готова для восстановления операндов источников, даже если местоположение результата команды совпадает с местоположением одного из операндов. Вообще если конвейер может быть остановлен так, что команды непосредственно предшествующие вызвавшей прерывание команде завершаются, а следующие за ней могут быть заново запущены для выполнения, то это говорит о том, что конвеер обеспечивает точное прерывание.

Выполнение команд Существует 2 способа выполнения команд на одноядерном процессоре:

1.По средствам организации конвейера.

2.Путём использования нескольких функциональных блоков, выполняющих одну и ту же операцию над несколькими командами

одновременно.

Когда число событий обработки в конвейере превышает обычные 5-6, которые мы рассматриваем такой процессор называют –

суперконвейерным.

Если процессор выполняет больше одной операции в 1 время, его называют – суперскалярным.

Сочетание этих двух подходов приводит к суперконвейерной архитектуре

Суперконвейерный процессор.

Т=n-N*C; Tn= (N-n-1)*C

Если выполнение первой операции конвейера = С, то возможно добиться наибольшей частоты выполнения команд, путём их запуска через интервал времени (С/N).

Это достигается 2мя способами:

1.Дальнейшее разделение стадий обработки конвейера на N операции;

2.Построение N конвейеров, которые могут перекрываться; Суперконвейерные процессоры имеют естественные ограничения

выполнения операций, определённой скоростью работы логических элементов и частотой появления конфликтов, которые не удаётся разрешить.

Суперскалярные процессоры

Суперскалярная обработка впервые была применена в суперкомпьютерах Cray. Параллельная организация обработки команд позволяет преодолеть ограничения быстродействия, свойственные

72

суперконвеерным процессам, Однако, суперконвейерная параллельная обработка требует меньшего времени для выбора из памяти и т.о. возникает необходимость в параллельном выборе команд. Одним из технологических достижений позволяющих этого добиться было размещение кеш 1го уровня на одном кристалле с процессором, что позволило разработчикам, организовать выполнение команд с меньшими расходами. В некоторых случаях суперскалярный компьютер использует одно устройство для выборки, декодирования и распределения команд между устройствами обработки. Например процессор Spark использует параллельную обработку, лишь после 3ей стадии конвейера. Вообще использование конвейера с параллельной обработкой команд требует:

1.Возможность выборки команд для всех конвейеров одновременно

2.Согласование работы отдельных конвейеров между собой

3.Переупорядочивание потоков команд сразу для нескольких конвейеров

4.Несколько дополнительных записей данных

5.Многопоточного кеша данных и разделение файлов регистров

Переупорядоченная команда может быть статической или динамической. Сочетание этих подходов затруднительно, т.к. компилятор не всегда имеет возможность предсказать механизм аппаратного переупорядочивания.

Суперскалярные операции ограничиваются количеством независимых команд , которые могут быть выбраны из памяти. Как показывают исследования, количество этих операций достаточно мало. Например, если алгоритм специально не предназначен для параллельной обработки данных, то параллельно могут быть выполнены не более шести команд, и не более четырёх для целочисленных операций.

73

10. Шины

Расширение линий шины.

К транзанция на шине начинается с выставления ведущим устройством адресной инф. Адрес позволяет выбрать ведомое устройство и установить соединение между ним и ведущим устройством. Для передачи адреса используется часть сигнальных линий шины, которые часто называют шиной адреса. На шину адреса могут выдаваться:

адреса ячеек памяти;

номера регистров;

Адреса портов в\в и т. д.

Многообразие типов адресов предполагает наличие дополнительной информации, уточняющей вид адреса, использующегося в данной транзанции. Такая информация может косвенно содержаться в самом адресе, а может передаваться отдельно по специальным упр-им линиям шин. Разнообразной может быть и структура адреса. Например старшие биты могут указывать на модуль оперативной памяти, а младшие на ячейку внутри этого модуля. В шинах предусмотрены адреса специального вида, позволяющие выбрать определенную группу ведомых устройств или все ведомые устройства сразу. Такие адреса называют широковещательными (broadcast). Такая возможность обычно используется в транзациях записи от ведущих к ведомому. Однако существует специальный вид транзакций чтения, т. е. одновременно от нескольких ведомых к ведущим, который называется широковещательный опрос (broadcаll). Информация,

возвращающаяся ведущему, представляет собой результат побитового сложения данных, поступивших от всех адресуемых ведомых. Число сигнальных линий, выделенных для передачи адреса, т. е. ширина шины адреса, определяет максимально возможный объем адресного производства. Это одна из базовых характеристик шины, т.к. от нее зависит потенциальная емкость адресуемой памяти и число обслуживаемых портов в\в.

[ линий, служащих для пересылки данных между модулями системы называют шиной данных. Важнейшими ее характеристиками являются:

Ее ширина;

Пропускная способность.

Ширина шины данных определяется количеством битов информации, которая может быть передана по шине за одну транзакцию, т.е. цикл шины. Одна транзакция шины может занимать несколько периодов. Обычно это 32,64 или 128 бит. В случае ширину данных выбирают целому числу байтов. Причем это число – целая степень 2. Элементы данных, задействовавших всю ширину обмена данных называют словом. В большинстве шин используются адреса, позволяющие указать отдельный байт слова. При передачи по шине данных части слова пересылка обычно производится по тем линиям, что и пересылка полного слова. Однако в ряде шин урезанное слово

74

передается по младшим линиям шины данных, что может оказаться особо удобно при расширении шин.

Ширина шин данных существенно влияет на производительность ВМ. Например, если ширина шины данных в 2 раза меньше длины команды, то ЦП в течение каждого цикла должен осуществлять доступ к памяти дважды.

Пропускная способность шины характеризуется количеством единиц информации (байт, бит), которую допускается передавать по шине за единицу времени (сек). Пропускная способность определяется физическим построением шины и природой подключения к ней устройств. Очевидно, чем шире шина, тем выше ее пропускная способность. Рассмотрим последовательность событий, происходящих по шине данных в пределах одной тринзанции.

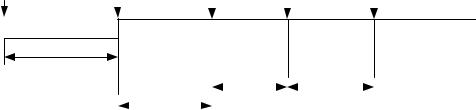

Пусть устройство А на одном конце шины передает данные устройству В из другого конца.. Устройство А ведущее, В – ведомое. Для начала устройство А должно получить управление шиной. При этом сигнал на А и В равны нулю. Данные появляются на шине с некоторой задержкой, следовательно на А сигнал равен 1. Эта задержка fзад. Интервал tзад может составлять 1-4 нс. На В→0. Скорость распространения данных по шине реально не в состоянии превысить 70% скорости света. Поэтому на В данные появляются с задержкой: tрс (распространения). Единственный способ снизить tрс – сокращение длины шины (или изменение типов проводников). Захват данных устройством В может быть произведен только по прошествии tст ( стабилизации). tст – это время, в течение которого данные на входе В должны стабилизироваться с тем, чтобы их можно было однозначно распознать. Необходимо упомянуть tудержания т.е. вр. в течение которого информация должна оставаться на шине после того как они были зафиксирован устройством В. tуд – время удаления.

Сигналы на устройстве А

А получет |

Данные появл. |

Данные появл. |

Данные появл. |

Данные появл. |

||

Могут быть |

||||||

упр. |

На шине |

На B |

Могут быть счит. |

|||

удалены. |

||||||

|

|

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

tзад |

Сигналы на |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

устройстве В |

|

|

|

|

|

tст |

|

|

tуд |

|||

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tрс |

|

|

|

|

|

О |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

бщее время передачи данных по шине tп = tзад+ tрс+ tст+ tуд Например, 4+1,5+2+0=7,5нс 133 мГц (частота шины).

На практике передача данных осуществляется с задержкой на инициализацию транзакций. Учитывая эту задержку, максимальная

vпередачи данных =1/(tп + tтр). Некоторые шины данных содержат дополнительные линии, применяемые для коррекции ошибок, возникших в процессе передачи. Выделение по одной

75

дополнительной линии на каждый байт данных. позволяет контролировать. Могут быть др. варианты коррекции ошибок, когда дополнительные линии используются совместно. По ним передается специальный корректировочный код, по которому он может быть не только обнаружен, но и скорректирован. Если адрес и данные в системе шины передаются по независимым сигнальным линиям, то ширина шины адреса и шины данных обычно выбирают независимо. Наиболее распространены комбинации 16 – 8, 16 – 16, 20 – 8, 20 – 16, 24 – 32, 32 – 32, 64 – 64. Во многих шинах адрес и данные передаются по одним и тем же линиям, но в разных тактах цикла шины – это прием

– временное мультиплексирование. Кроме адреса и данных,

непременным атрибутом шины являются линии, по которым передается управляющая информация и информация о состоянии. Сумма таких линий называют шиной управления. Сигнальные линии, входящие в шину управления, можно разделить на несколько групп.

I. Линии, по которым передаются сигналы управления транзикциями, т.е. сигналы, определяющие:

1.Тип выполнения транзикции;

2.Количество байт, передавшихся по шине данных, и если передается часть слова, то какие именно байты;

3.Какой тип адреса выставляется на шину адреса;

4.Какой протокол передачи должен быть применен.

В эту группу обычно входят 2 – 8 сигнальных линий.

II. Линии передачи информации о состоянии (статусе устройств, участвующих в данной транзакции). В эту группу входят 1 – 4 линии, по которым ведомое устройство сообщает ведеущему свое состояние или передает сигналы ошибок.

III. Линии арбитража. Арбитраж необходим в тех случаях, когда несколько ведущих претендуют на доступ к шине. Число линий арбитража в разных шинах 3 – 11. В зависимости от типа шины могут применятся разные типы арбитража. При централизованном арбитраже только 1 устройство (например, ЦП) имеет соответствующую аппаратную поддержку арбитража. Этот «центральный арбитр» может определять приоритеты и обладает правом прерывать транзикции в случае необходимости Централизованный арбитраж является достаточно простой схемой, часто применяемой в однопроцессорной конфигурации.

В распределенной схеме каждое из потенциально ведущих устройств может выступать в качестве арбитра, и все ведущие устройства имеют равные права. Схема арбитража основана на заранее определенных приоритетах устройств, которые могут быть изменены программой.

Последовательный арбитраж (daisy chaining) – это комбинация централизованной и распределенной систем. Устройства,

76

подключенное к шине запрашивает доступ, посылая сигнал к своему непосредственному соседу, находящемуся ближе к центральному арбитру. Если более близкое устройство также запрашивает управление шиной, то запрос более дальнего устройства блокируется. Центральный арбитр передает управление устройству, которое находится ближе всего к нему. Т. о. приоритет каждого устройства определяется его физическим положением на шине и не может быть изменено программой. Иногда может использоваться несколько дополнительных сигнальных линий, которые позволяют обойти ближайшее устройство и т. о. получить схему распределения приоритетов, частично управляемую программно.

IV. Линии прерывания – по ним передаются запросы на обслуживание, посылаемых от ведомых устройств к ведущим. Под сами запросы обычно отводят 1 – 2 линии. Однако при одновременном возникновении запросов от нескольких ведомых, могут возникнуть проблемы арбитража. Для этого выделяют дополнительные линии, если только для этих целей не используют линии (III).

V. Линии для организации последовательных локальных сетей. Наличие 1 – 4 таких линий стало общепринятой практикой в современных шинах. Это обусловлено тем, что последовательная передача данных протекает значительно медленнее, чем II. И сети выгоднее строить не загружая выгодные линии основных шин адреса и данных. Кроме того, линии этой группы могут быть использованы как полноценный, хотя и медленный тракт для замены шины адреса и шины данных в случае их отказа.

VI. В некоторых шинах управления есть (VI) группы сигнальных линий, 4 – 5 линий позиционного кода, подключенным к специальным выводам разъема. При помощи перемычек на этих выводах можно задать уникальный позиционный код разъема на материнской плате или вставленной в этот разъем дочерней плате. Такой код может быть использован для индивидуальной инициализации каждой отдельной платы при включении / перезапуске системы.

В каждой шине обязательно присутствуют линии, входящие в VII группу.

VII. Линии тактирования и синхронизации. При проектировании таким линиям уделяется особое внимание. В состав данной группы в зависимости от протокола шины (синхронный / асинхронный) входят 2

– 6 линий.

VIII. Линии для подвода питающего напряжения и линии заземления. Большое количество линий системы шины предполагают использование разъемов со значительным числом контактов. В некоторых шинах разъемы имеют сотни контактов, где предусмотрено подключение вспомогательных шин специального назначения. Свободные линии для локального обмена между дочерними платами,

77

множественные параллельно расположенные контакты для размножения питаний и заземлений.

78

11. Организация подсистем памяти.

Иерархия памяти.

Существует множество технологий для хранения данных. Например, память на магнитных сердечниках, перфокарты, магнитные ленты, оптические дики, полупроводниковые запоминающие устройства и т. д. Каждая из этих технологий имеет свое место на рынке, т.к. покрывает соответствующий диапазон времени доступа с обратно пропорциональной стоимостью хранения 1 данных, которая в свою очередь пропорциональна стоимости записи.

Тип записывающего |

Время выборки |

Типичный объем |

|

устройства |

|

|

|

Сверхоперативные |

0,01 – 1 нс |

32/64/128 бит |

|

записывающие |

|

|

|

устройства (регистры) |

|

|

|

Быстродействующие |

0,5 – 2 нс |

32 Кб – 2 Мб |

|

буферное |

|

2,5 – 30 нс |

|

записывающее |

|

|

|

устройство (КЭШ) |

|

|

|

(основная память) |

2 – 20 нс |

128 Мб – 4 Гб |

|

Оперативные |

|

|

|

запоминающие |

|

|

|

устройства |

|

|

|

Вторичные |

|

5 -20 мс |

30 Гб – 1 Тб |

запоминающее |

|

|

|

устройство |

(жесткие |

|

|

диски) |

|

|

|

Накопители |

на |

100 – 50 мс |

600 Мб – 40 Гб |

оптических дисках |

|

|

|

On – line (магнитные |

1 с -10 мин |

∞ |

|

ленты и т.д.) |

|

|

|

В основе иерархии памяти РС лежат 2 принципа:

1.Принцип локальных обращений.

2.Соотношение «стоимость – производительность».

1. говорит о том, что большинство программ не выполняет обращений ко всем своим командам и данным равновероятно, а оказывает предпочтения некоторой части своего адресного производства.

Свойство локальности определяются исключительно свойством программы, а не аппаратом обеспечения. Например, программы, написанные на языке hisp, имеют локальность, которая не соответствует локальности физических адресов. Тем не менее при организации иерархической памяти обычно учитывают 3 разных вида локальности:

79

1. временная локальность, т. е. данные, к которым был осуществлен доступ, будут задействованы снова в ближайшее время;

2. пространственная локальность, т. е. доступ к данным осуществляется в ограниченной области адресного пространства;

3. последовательная локальность, т.е доступ к командам осуществляется по последовательным адресам памяти в современном компьютере строится из нескольких уровней, причем более высокий уровень меньше по объему, быстрее меняет большую стоимость в пересчете на байт, чем более низкие уровни. Уровни иерархически взаимосвязаны, т. е. все данные на одном уровне могут быть также найдены на более низком уровне, все данные на этом – на следующем более низком и т. д.

Иерархия памяти обычно состоит из многих уровней, но в каждый момент времени мы имеем дело только с двумя близлежащими уровнями. Минимальная единица информации, которая может либо присутствовать, либо отсутствовать в иерархии, называется блоком. Размер блока может быть фиксированным или переменным. Если размер фиксированный, то объем памяти является кратным размеру блока. Успешное или не успешное обращение к более высокому уровню называется соответственно попаданием (hit) или промахом (miss). Попадание – это обращение к объему памяти, который найден на более высоком уровне. Промах – не найден. Соответствующая доля попаданий hit rabe – это доля обращений, найденных на более высоких уровнях, miss rabe – доля обращений, которые не найдены на более высоких уровнях.

Т. к. повышение производительности является одной из причин появления иерархической памяти, частота попаданий и промахов является важнейшей характеристикой. Время обращений при попадании hit time – это время, обращения к более высокому уровню иерархии, которое включает в себя в частности время, необходимое для определения того, является ли обращение попаданием / промахом. Потери на промах – это время для замещения блока в более высоком уровне с более низкого уровня плюс время для пересечения этого блока в требуемое устройство. кроме этого, потери на промах включают в себя.

Время доступа – время обращения к первому слову блока при

Время пересылки – время для оставшихся слов в блоке.

Время доступа связано с задержкой памяти более низкого уровня, в то время, как время пересылки связаныс полосой пропуска, как и между устройствами памяти нашли 2-х смежных уровней.

Чтобы понять некоторые уровни иерархии памяти необходимо ответить на некоторые вопросы.

1.Где может размещаться блок на верхнем уровне иерархии;

2.Как найти блок, когда он находится на верхнем уровне;

3.Какой блок должен быть замещен в случае промаха;

4.Что происходит во время записи ( какова стратегия записи).

80