КЛ_АВС

.pdf

IJVM. К сожалению, в какой-то момент компания Intel исчерпала запасы кодов операций, и один код операции, OxFF, стал кодом смены алфавита и использоваться для разрешения второго байта команды.

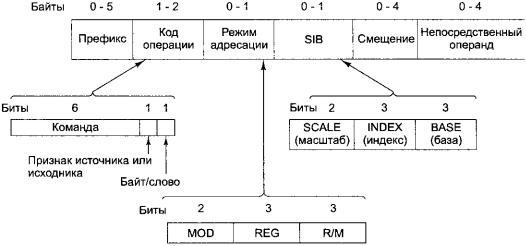

Рис. 5.10. Форматы команд процессора Pentium 4

Отдельные биты в кодах операций процессора Pentium 4 дают довольно мало информации о команде. Единственной структурой такого рода в поле кода операции является младший бит в некоторых командах, который указывает, что именно вызывается — слово или байт, а также соседний бит, который указывает, является ли адрес памяти (если он вообще есть) источником или приемником. Таким образом, в большинстве случаев код операции нужно полностью декодировать, чтобы установить, к какому классу относится выполняемая операция и, следовательно, какова длина команды. Это значительно снижает производительность, поскольку необходимо производить декодирование еще до того, как определено, где начинается следующая команда.

В большинстве команд вслед за байтом кода операции, который указывает местонахождение операнда в памяти, следует второй байт, несущий всю информацию об операнде. Эти 8 бит распределены в 2- разрядном поле MOD и двух 3-разрядных регистровых полях REG и R/M. Иногда первые 3 бита этого байта используются в качестве расширения для кода операции, давая в сумме 11 бит для кода операции. Тем не менее 2- разрядное поле означает, что существуют только 4 способа обращения к операндам и один из операндов всегда должен быть регистром. Логически должен идентифицироваться любой из регистров: ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, EBP, ESP, но правила кодирования команд запрещают некоторые комбинации, которые отводятся для особых случаев. В некоторых типах команд требуется дополнительный байт, называемый SIB (Scale,

Index, Base — масштаб, индекс, база), который дает дополнительную спецификацию. Эта схема не идеальна, она является компромиссом между требованием обратной совместимости и желанием учесть новые особенности, которые не были предусмотрены изначально.

51

Добавим еще, что некоторые команды имеют 1, 2 или 4 дополнительных байта для определения адреса команды (смещение), а иногда еще 1, 2

или 4 байта, содержащих константу (непосредственный операнд).

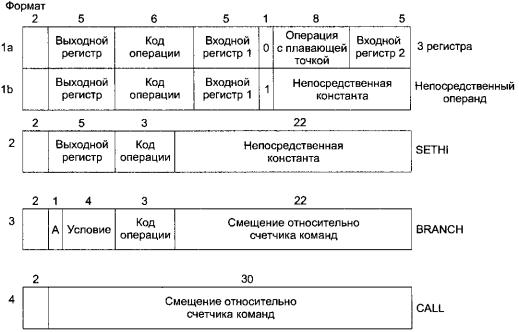

Форматы команд процессора UltraSPARC III

Архитектура команд процессора UltraSPARC III состоит из 32разрядных команд, выровненных в памяти. Команды очень просты. Каждая из них выполняет только одно действие. Типичная команда задает два регистра, в которых находятся исходные операнды, и один выходной регистр. Вместо одного из регистров команда может использовать константу со знаком. При выполнении команды LOAD два регистра (или один регистр

и13-разрядная константа) складываются вместе для определения считываемого адреса памяти. Данные оттуда записываются в другой указанный в команде регистр.

Изначально машина SPARC имела ограниченное число форматов команд (рис. 5.11). Со временем добавлялись новые форматы. Большинство новых вариантов были получены за счет отъема нескольких битов у какогонибудь поля. Например, изначально для команд перехода использовался вариант 3 формата (с 22-разрядным смещением). Когда были добавлены команды прогнозируемых ветвлений, из 22 бит было изъято 3: один из них стал использоваться для прогнозирования (совершать или не совершать переход), а два оставшихся определяли, какой набор битов условного кода нужно использовать. В результате получилось 19-разрядное смещение. Приведем другой пример. Существует много команд преобразования типов данных (целых чисел — в числа с плавающей точкой и т. д.). Для большинства этих команд используется вариант lb формата, в котором поле непосредственной константы разбито на 5-разрядное поле, указывающее входной регистр, и 8-разрядное поле, предоставляющее дополнительные биты кода операции. Однако в большинстве команд все еще используются форматы, показанные на рисунке.

Первые 2 бита каждой команды помогают определить формат команды

исообщают аппаратному обеспечению, где найти оставшуюся часть кода операции, если она есть. В варианте 1а формата оба источника операндов представляют собой регистры; в варианте lb один источник — регистр, второй — константа в промежутке от -4096 до +4095. Бит 13 определяет один из этих двух форматов. (Биты нумеруются с 0.) В обоих случаях местом сохранения результатов всегда является регистр. Достаточный объем пространства имеется для 64 команд, некоторые из которых зарезервированы на будущее.

Поскольку все команды 32-разрядные, включить в команду 32разрядную константу невозможно. Команда SETHI устанавливает 22 бита, оставляя пространство для другой команды, чтобы установить оставшиеся 10 бит. Это единственная команда такого необычного формата.

52

Рис. 5.11. Исходные форматы команд процессора SPARC

Для непрогнозируемых условных переходов используется вариант 3 формата, в котором поле условия определяет, что проверяется. Бит А нужен для того, чтобы избегать пустых операций при определенных условиях. Формат команд прогнозируемых ветвлений тот же, только с 19-разрядным смещением, как было сказано ранее.

Последний формат используется для команды вызова процедуры CALL. Эта команда особая, поскольку только в ней для определения адреса требуется 30 бит. В данной архитектуре существует один 2-разрядный код операции. Требуемый адрес — это целевой адрес, разделенный на четыре. Таким образом, относительно текущей команды диапазон составляет примерно 231 байт.

53

7. Методы адресации

Вопрос, каким образом в адресном поле команды может быть указано место нахождения операнда, считается одним из центральных при разработке архитектуры вычислительной машины. С одной стороны разработчики стремятся уменьшить длину адресного поля при сохранении возможности доступа ко всему адресному пространству, с целью аппаратных затрат, с

другой способ задания адреса должен способствовать max. сближению конструкций знаков при программировании высокого уровня и машинных команд.

Для того, чтобы рассматривать методы адресации введем определение –

исполнительным адресом операнда называется двоичный код номера ячейки памяти, служащий источником или преемником операнда по которому происходит фактическое обращение к указанной ячейке. Если операнд хранится не в основной памяти, а в реестре процессора, то его исполнительным адресом будет номер регистра.

Адресный код команды – это двоичный код в адресном поле команды из которого необходимо сформировать исполнительный адрес. В операторах ассемблера могут использоваться операции следующих типов:

1.регистр;

2.адрес памяти;

3.сегментный регистр;

Всовременных вычислительных машинах исполнительный адрес и адресный код, как правило, не совпадают и для доступа к данным требуются соотношения преобразования.

Способ адресации – это способ формирования исполнительного адреса операнда по адресному коду команд.

Чтобы устройство управления вычислительной машины могло определить, какой именно способ адресации принят в данной команде, в

разных вычислительных машинах используются различные приемы. Часто

54

разным способам адресации соответствуют и разные коды операции. Другим вариантом является добавление в состав команды специального поля,

содержимое которого определяет, какой из способов адресации применен.

Иногда, в команде несколько таких полей, по 1-ому на каждый операнд.

Отметим также, что иногда в команде вообще отсутствует адресная операция, т.е. имеет место неявная адресация. При неявной адресации адресное поле либо отсутствует, либо содержит не все необходимые адреса.

Отсутствующий адрес в данном случае определяется кодом операции.

Непосредственная адресация

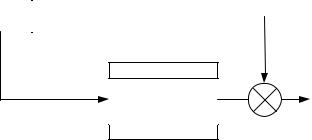

При непосредственной адресации в адресном поле команды вместо адреса содержится сам операнд. Этот способ может применяться в арифметических операциях, операциях сравнения, а также для разгрузки данных в регистр. Формат команды:

КОП СА значение

add R4,#3 – в регистр 4 помещается его предыдущее значение,

сложенное с 3. move R5,4Ch

где КОП – кол-во операций, СА – способ адресации. Когда появляется число оно обычно представлено дополнительным кодом. При записи в регистр, имеющий разрядность, превышающую длину непосредственного операнда, операнд помещается в младшей части регистра, а остающиеся свободные позиции заполняются значением знакового бита операции.

Помимо того, что в адресном поле указаны только константы, еще один недостаток непосредственного способа адресации заключается в том, что длина операнда ограничена длиной адресного поля команды, который

обычно меньше длины машинного слова.

55

Достоинства – сокращение время выполнения команды, кроме того,

экономится память, т.к. не требуется специальной ячейки для хранения операнда.

Прямая адресация

При прямой адресации (абсолютной) адресный код прямо указывает номер ячейки памяти, к которой производится обращение.

КОП |

СА |

АК |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Операнд

add R4,(1001) – R4 ← R4 + Mem[1001]

где АК – исполнительный адрес команды.

Недостаток – нужно длинное адресное поле. Кроме того, указанный в команде адрес не может быть изменен в процессе вычислений.

Косвенная адресация

Одним из способов преодоления проблемы прямой адресации является косвенная адресация, когда с помощью ограниченного кода адреса указывается адрес ячейки панели, в свою очередь содержащей адрес операндов.

КОП |

СА |

АК |

|

|

|||

|

|

|

|

АИСП

Операнд

add R1,@(R3) – R1 ← R1 + Mem[Mem[R3]]

56

где АИСП – исполнительный адрес.

Недостаток – необходимость в двукратном обращении к памяти,

сначала для извлечения адреса операнда, затем обращение к самому операнду. Также используется дополнительная ячейка памяти.

Регистровая адресация

Эта адресация подобна прямой адресации за исключением того, что адресное поле команды указывает не на ячейку памяти, а на номер регистра.

Обычный размер адресного поля в данном случае составляет 3 или 4 бита,

что позволяет указать соответственно на 1 из 8 или 16 регистров общего назначения.

КОП |

СА |

R |

|

|

|||

|

|

|

|

Операнд

add R4,R3

где R – АИСП.

Косвенная регистровая адресация

Представляет собой косвенную адресацию, при которой исполнительный адрес операнда хранится не в ячейке основной памяти, а в регистре процессора. Соответственно адресное поле команды содержит не ячейку памяти, а регистр.

КОП |

СА |

R |

|

|

|

Регистры

Память

Адрес

Операнд

57

add R4,(R1)

Достоинства и ограничения косвенной регистровой адресации те же, что и у обычной косвенной адресации, но благодаря тому, что косвенный адрес хранится не в памяти, а в регистре, для доступа к операнду требуется на одно обращение к памяти меньше.

Адресация со смещением

При адресации со смещением исполнительный адрес формируется в результате тестирования содержимого адресного поля команды с содержимым одного или нескольких регистров процессора. Адресация со смещением предполагает, что адресная часть команды включает в себя как минимум 1 поле, в котором содержится константа, смысл которой в разных вариантах адресации со смещением может меняться. Константа может представлять собой некоторый базовый адрес, к которому добавляется хранящееся в регистре смещение. Допустим и противоположный подход:

базовый адрес находится в регистре процессора, а в соответствующем поле указывается смещение относительно этого адреса. В некоторых процессорах для реализации адресации со смущением, предусмотрены специальные регистры (направленные базовые или индексные).

КОП |

СА |

R |

Ак |

|

|

||||

|

|

|

|

|

Регистры

Составляющий

адрес

Такая адресация может быть еще более сложной.

Обычно использование специальных регистров предполагается по умолчанию, поэтому адресная часть команды может содержать только одно поле – Aк (адрес команды). Если же составляющая адреса может

58

располагаться в произвольном регистре общего назначения, то для указания конкретного регистра в команду включают дополнительное поле.

В рамках адресации со смещением имеется еще один вариант, при котором адрес вычисляется не суммированием, а конкатенацией составляющих адреса.

Относительная адресация

Применяется для получения исполнительного адреса операнда.

Содержимое поля Ак команды складывается с содержимым счетчика команды. Таким образом, адресный код Ак в команде представляет собой смещение относительно адреса текущей команды.

Достоинства – программа становится перемещаемой в памяти.

Базовая регистровая адресация

В этом случае регистр называемый базовым, содержит полноразрядный адрес, а поле Ак – смещение относительно этого адреса. Ссылка на базовый регистр может быть явной или неявной, если в ВМ имеется специальный базовый регистр. Такой способ обычно используется для доступа к элементам массива, положение которых в памяти может меняться походу вычислений.

Достоинства – смещение имеет меньшую длину, чем полный адрес, что позволяет сократить длину адресного поля команды.

Индексная адресация

59

Поле Ак содержит название регистра, указывающего на адрес ячейки памяти, а регистр указный явно или неявно – смещение относительно этого адреса.

Иногда базовую индексацию адресации объединяют в 1 тип, при этом в коде команды указываются регистры, содержащие базовые и индексные адреса.

add R4,(R1+R2)

После (или до) выполнения команды содержимое индексного регистра может быть увеличено или уменьшено на 1. Индексирование с увеличением содержимого индексного регистра называется автоинкрементной адресацией, а индексирование с уменьшением - автодекрементной

адресацией.

Вкрайнем случае может быть индексная адресация с масштабированием

исмещением – содержимое индексного регистра умножается на масштабный коэффициент и суммируется с Ак. При этом может осуществляться автоинкрементная или автодекрементная индексация регистра.

Страничная адресация

Эта адресация предполагает разбиение всего адресного пространства на страницы. Каждая страница характеризуется своим начальным адресом,

выступающим в качестве базы. Старшая часть этого адреса хранится в специальном регистре адреса страницы. В адресном коде команды указывается смещение внутри страницы, рассматриваемое как часть адреса.

Используемый адрес образуется конкатенацией адресного кода команды и регистра страницы.

60