КЛ_АВС

.pdf

Основные цели, которые преследовали его разработчики заключались в создании недорогого интерфейса , более высокопроизводительного, чем интерфейс ATA , полностью с ним программно совместимого; более удобное подключение дисков к компьютеру и большую длину кабеля; низковольтную и экономичную в энергопотреблении. Скорость передачи данных по этому интерфейсу в первоначальном варианте стандарта150 Mб/с, предположительно max 600 Mб/с. Интерфейсный кабель содержит 2 пары сигнальных проводов и 3 экранных провода. Его длина должна быть<1 м. Предполаг. возможности горячего отключения и переключения устройства.

В интерфейсе Serial ATA к каждому кабелю подключено только 1 устройство. Различие дисков на ведущее и ведомое нет, но при необходимости контроллер интерфейса может эмулировать поведение 2-х независимых дисков как пары ведущий-ведомый.

II. Интерфейс SCSI (Small Computer System Interface) – для малых вычислительных систем. Появился приблизительно тогда, когда и ATA, но предназначен для связи различных устройств, а не только дисков. Данный интерфейс имеет две модификации по разрядности передаваемых данных:

-узкую (8 бит) – возможно подключение до 8 устройств.

-широкую (16 бит) - возможно подключение до 16 устройств.

Подключаемые устройства бывают 2 – х типов:

1.контролер периферийных устройств;

2.хост – адаптер.

Устройства 1-го вида могут управлять работой до 8 – ми логических устройств, а хост – адаптер используется для связи шины SCASI с шиной расширения компьютера.

За время существования Интернета были созданы различные его модификации, отличающиеся пропускной способностью. В начале 2000г. пропускная способность 320 Мб/сек.

Еще 2 варианта: Fast (быстрый) и Ultra (сверхбыстрый).

Кроме того, существует спецификация последовательного варианта интерфейса для оптического канала связи, которые относятся к этому семейству. Электрические параметры интерфейса SCASI также имеют несколько модификаций, отличающихся способом передачи сигнала и уровнем напряжения при допустимой длине шин до 25 м.

Выполнение операций обмена по шинам SCASI осуществляется управлением контролера, инициализирующего устройства и предполагающее передачу сообщений, команд и данных плюс информацию о состоянии. Сообщения в основном указывают на необходимость каких – либо действий, либо информируют об их выполнении. Команды указывают на то, какие операции необходимо выполнить (чтение, запись, поиск и т.д.). Учитывая это, интерфейс разработан для связи различных устройств, все команды разделены на группы: есть группа команд для устройств прямого доступа (диски и т.д.); группа СДкоманд; группа сканеров и т.д.

91

Для установления связи с целым устройством инициализатор обменивается с ним сообщением. После установки связи он посылает устройству команды, в процессе выполнения которых осуществляется обмен данными, дополняющийся по мере необходимости сообщениями. Для адресации данных на дисках команды SCASI используют 32–х разрядные адреса , что ограничивает объем дисков 2 терабайтами. Интерфейс SCASI считается более надежным и производительным, чем АТА, но и более дорогим. Он применяется в серверных системах.

Управление диском.

Обычно операционная система поддерживает очередь запросов к жесткому диску. Это создает возможность изменять порядок запросов с тем, чтобы сделать обращение к диску более организованными и вносящими минимальные задержки в работу системы. Если очередь работает по принципу «1 пришел, 1 ушел», это может привести к крайне неэффективной работе диска. В частности при этом повышается время поиска информации на диске и повышается износ его механической части. В связи с этим разработаны специальные алгоритмы доступа к дискам. В настоящее время используют 3 варианта алгоритма доступа:

I. Алгоритм работает по кратчайшему времени доступа ( SSTF – shortest Suck Time First). Данный алгоритм работает так: когда заканчивается очередная операция доступа к диску, следующим обрабатывается запрос к данным, расположенным на минимальном расстоянии от текущего положения считывающей головки. Данный алгоритм минимализирует задержку и дает общее увеличение производительности. Однако время ответа на запрос зависит от того, насколько запрос близок к предыдущему, и теоретически ответ на некоторые запросы может быть получен на ∞ - большое время.

II. Алгоритм подъемника. Elevator Algorithm. При использовании этого алгоритма считывающие головки преимущественно в одном направлении (от центра диска к краю (наоборот)), каждый раз обрабатывая ближайший запрос в данном направлении. Когда запросы в одном направлении оказываются исчерпаны, головка движется в обратном направлении. Этот алгоритм обеспечивает более равномерное время отклика, но он не гарантирует выполнение запроса. Однако, если осуществляются непосредственные запросы к одному и тому же цилиндру, то считывающая головка может находится над ним ∞ долго. Данная проблема решается ограничением, которое может располагать блок головок над одним цилиндрам. Еще одно простое решение заключается в том, что обслуживаются только те запросы, которые уже были на момент перемещения головки.

III. Односторонний алгоритм подъемника. One way Elevator Algorithm. Обычный двусторонний алгоритм медленнее обрабатывает запросы к внешней и внутренней стороне диска, чем запросы, приходящиеся на его середину. Эта проблема может быть решена следующим образом:

92

допускается движение головки только в одном направлении. Когда запросы исчерпаны, блок головки возвращается на исходное положение и начинает новый проход. В этом случае возникает дополнительное время на возврат головок в исходное положение. Но если обращение к диску происходит достаточно часто, то возврат головок будет происходить редко и больших различий по скорости доступа с I. не будет, но вопросы обрабатываются равномерно.

Дисковый КЭШ.

Концепция КЭШ – памяти применима к дисковым записывающим устройствам. Принцип кэширования дисков во многом схож с принципом кэширования основной памяти, несмотря на то, что способы доступа к диску и основнай памяти существенно различаются. Дисковая КЭШ – память представляет собой память с произвольным доступом, размещается между диском и основной памятью. Емкость такой памяти велика от 8 Мб и более. Пересылка информацию между дисками основной памяти осуществляется контролером КЭШ – памяти.. Изготавливают диски КЭШ – памяти по той же технологии, что и основную. Основная память или основная память системы может использоваться в качестве дискового КЭШа. В качестве 1 пересылки (блока) может выступать сектор, несколько секторов или 1/несколько дорожек диска. В случае пересылки секторов КЭШ – память заполняется не только текущим сектором, но и секторами, расположенными за ним – это называют опережающим чтением (Read Ahead). В дисковых КЭШах используют а.п.совокупной записи. Обычно дисковая КЭШ – память включает в себя средство коррекции ошибок и архитектура КЭШ – памяти. На современных магнитных дисках обычно реализуют полностью ассоциативное отображение.

93

12. Многопроцессорные системы.

Классификация систем параллельной обработки данных.

Можно выделить 4 основных типа архитектур систем параллельной обработки.

I. Конвейерная и векторная обработка. Основу конвейерной обработки составляет раздельное выполнение некоторых операций в несколько этапов с передачей данных от одного этапа к другому. Рост производительности при этом обеспечивается за счет того, что одновременно на различных ступенях конвейера выполняется несколько операций. При выполнении векторной команды одна и та же операция применяется ко всем элементам вектора. Для настройки конвейерного выполнения операций при этом может потребоваться некоторое время, однако затем операнды могут поступать в конвейере с максимальной скоростью, которая способна обеспечить аппаратура. При этом не возникает пауз в связи с выборкой новой команды или определением адреса перехода при условных вычислениях. Т. о., главный принцип операций на векторной машине состоит в выполнении комбинаций из нескольких элементарных операций, которые должны повторно применяться к некоторому блоку данных.

II. Машина типа SIMD (Single Instruction Multiple Date). Машина типа

SIMD состоят из большого числа идентичных процессорных элементов, имеющих собственную память. Все процессорные элементы в такой машине выполняют одну и ту же программу. Очевидно, что такая машина эффективна лишь при решении задач, которые позволяют процессорам выполнять одну и ту же работу. Модель вычисления для машины SIMD очень похожа на модель вычислений для векторного процессора, т. е. одиночная операция выполняется над большим блоком данных. В отличие от ограничения конвейерного функционирования векторного процессора матричный процессор может быть более гибким, т. к. обрабатывающие элементы таких процессоров представляют собой универсальные программирующие ЭВМ, так, что задача, решаемая параллельно, может быть достаточно сложной и содержать ветвления. Модели вычисления на векторных и матричных настолько схожи, что часто объединяются в один класс.

III. Машины типа MIMD (Multiple Instruction). Подобно тому как термин матричный процессор применяют к машинам типа SIMD, термин мультипроцессор является практически применимо для машины типа MIMD.

Вмультипроцессорной системе каждый процессорный элемент выполняет свою программу, достаточно независимо от других процессорных элементов.

Вмультипроцессоре с общей памятью (сильно связанные мультипроцессоры) имеется КЭШ – данных и КЭШ – команд, доступные всем процессорным элементам. С общей памятью процессорные элементы связаны при помощи общей шины или сети обмена. В противоположность этому варианту в

94

слабосвязанных мультипроцессорных системах (система с локальной памятью) вся память разделена между процессорными элементами, и каждый блок памяти доступен только связанному с ним процессору. Процессорные элементы соединены друг с другом при помощи сети обмена. Базовой моделью вычислений в мультипроцессоре является независимых процессоров, который эпизодически обращается к разделяемым данным. Существует большое количество вариантов этой модели. На одном конце спектра модель распределенных вычислений, в которой программа делится на довольно большое число параллельных задач, состоящих из множества подпрограмм. Модель потоковых вычислений, в которых каждая операция в программе может рассматриваться как отдельный процессор.

IV. Многопроцессорные машины с SIMD (MSIMD). Многие современные суперкомпьютеры представляют собой многопроцессорные системы, в которых в качестве процессоров используют векторные процессоры или процессоры типа SIMD. Машины такого типа дают возможность использовать векторные операции для некоторых частей программы и гибкие возможности архитектуры MIMD для других частей программы. Одной из отличительных особенностей многопроцессорных вычислительных систем, при помощи которых процессоры соединяются друг с другом и с памятью. Многие характеристики производительности выражаются отношением времени обработки к времени обмена, что придает сети обмена важное значение в обеспечении производительности. Существует 2 основные модели межпроцессорного обмена: 1) основана на передачи сообщений; 2) на использовании общей памяти. В многопроцессорной системе общей памяти один процессор осуществляет запись в конкретную ячейку, а другие производят считывание из этой ячейки.

Чтобы обеспечить согласование данных и синхронизировать процесс обмена часто реализуют по принципу взаимного исключения доступа к общей памяти. В архитектурах с локальной памятью непосредственное распределение памяти невозможно. Вместо этого процессоры получают доступ к совместно используемым данным по средствам передачи сообщений по сети обмена. Эффективность системных коммуникаций зависит от протокола обмена и пропускной способности каналов обмена и памяти. Т. о., существующие многопроцессорные машины распадаются на 2 основных класса в зависимости от количества объединяемых процессоров, которая определяет и способ организации памяти и межпроцессорных соединений. К 1 – й группе относятся машины с общей, реже разделяемой основной памятью, объединенных до нескольких десятков (более 32) процессоров. сравнительно небольшое количество процессоров в таких машинах позволяет иметь одну централизованную общую память и объединение процессора с помощью одной общей шины. При наличии у процессоров КЭШ – памяти достаточного объема. Высокопроизводительная шина и общая память могут удовлетворять обращение к памяти, поступающей от нескольких процессоров. Т. к. имеется единственная память

95

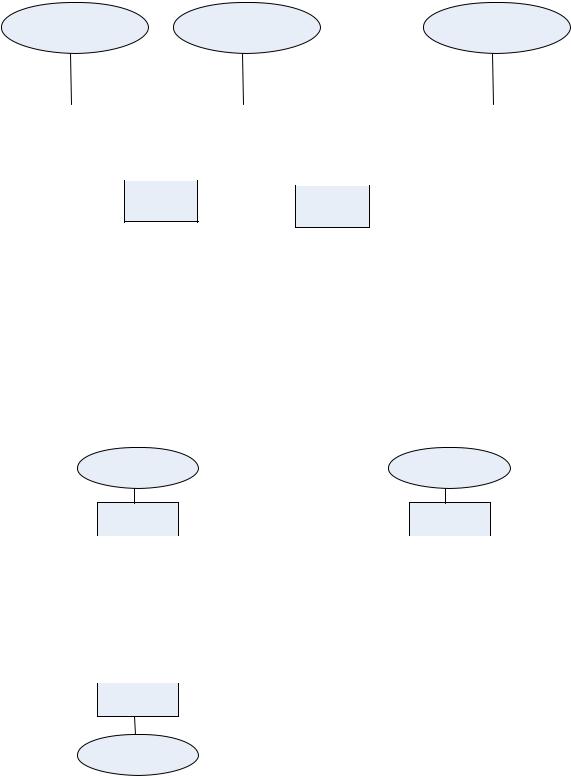

с одним и тем же временем доступа, эти машины иногда называются ИМА (Uniform memory Access). Такой способ организации является в настоящее время наиболее популярным для серверов малого и среднего класса. Типовая архитектура

Процессор |

|

|

Процессор |

. |

Процессор |

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

. |

|

|

||

|

|

|

|

|

. |

|

|

||

|

|

|

|

|

. |

|

|

||

|

|

|

|

|

. |

|

|

||

Кэш-п |

|

|

Кэш-п |

Кэш-п |

|||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ОП |

Устр. В/в |

|

2 - ую группу машин составляют крупномасштабные системы с распределенной памятью. Чтобы поддерживать большое количество процессоров, приходится распределять основную память между ними. Иначе полосы пропускания памяти может не хватать для удовлетворения запросов. Модель, которая при этом получается, фактически представляет собой объединение машин ↑ при помощи сети:↓

Процессор

Кэш-п

Процессор

Кэш-п

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Локальная |

|

|

|

|

|

|

Подсист. |

|

Локальная |

|

|

|

|

Подсист. |

|

|

память |

|

|

|

|

|

|

В/в |

|

память |

|

|

|

|

В/в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Высокопроизводительная сеть |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Локальная |

|

|

|

|

|

|

Подсист. |

|

|

|

|

|

|

|

|

|

память |

|

|

|

|

|

|

В/в |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Кэш

Процессор

96

С ростом |

числа процессоров |

просто невозможно обойти |

|||

необходимость |

реализации |

модели. |

Распределение |

памяти |

с |

высокопроизводительной сетью для связи процессоров . |

Распределение |

||||

памяти мужду узлами системы имеет 2 главных преимущества: |

|

||||

1.Это эффективный способ повышения полосы пропускания памяти;

2.Это снижает задержку обращения к локальной памяти.

Обычно устройства в/в также кА Ки память распределяется по узлам и в действительности узлы могут содержать небольшое число процессоров, соединенных между собой другим способом. Основная разница в архитектуре, которую следует выделять в машине с распределенной памятью, заключается в том, как осуществляется связь и какова логическая модель памяти.

Модели связи и архитектуры памяти.

Имеется 2 альтернативы организации устройств памяти и связанные с этим 2 альтернативных метода для передачи данных между процессорами. Физически отдельные устройства памяти могут адресоваться, как логически единое адресное пр-во. Это означает, что проц.-р может выполнять обращение к ячейкам памяти, предполагая, что он при этом имеет соответствующие права доступа. Такие машины называются машинами с распределенной распределяемой памятью DSM (Distributed Shared Memory) или NUMd т. к. время доступа в таких системах зависит от расположения ячейки памяти. В альтернативном случае адресное производство состоит из отдельных логически несвязанных адресных пр-в. В этом случае, каждый модуль «Процессор – память» представляет собой отдельную ВМ, поэтому такие системы называют многомашинными. С каждой из этих организаций адресного производства связан свой механизм обмена. В 1–м случае используется разделяемая общая память, а во 2-м – механизм передачи сообщений. Каждый из этих механизмов обмена имеет свои плюсы и минусы.

1. Для обмена в общей памяти:

«+» а) совместимость с хорошо изученными механизмами, использующихся в однопроцессорной системе;

б) простота программирования, особенно если модели обмена между процессорами достаточно сложны или динамически смешиваются в процессе использования;

в) более низкая задержка обмена и лучшее использование полосы пропускания при обмене малыми порциями данных;

г) возможность использования аппаратно – управляемого кэширования для снижения частоты уделенного обмена, допускающая кэширование всех данных, как разделяемых, так и не разделяемых.

97

Для обмена при помощи передачи сообщений: «+» а)аппаратура может быть более простой;

б) понятные модели обмена, позволяющие сократить число передаваемых данных при написании или оптимизации программы. Требуемая модель обмена может быть надстроена над аппаратной, моделью, которая использует из этих механизмов. Поддержку передачи сообщения над общей памятью реализовать намного проще, если предположить, что полосы пропускания канала связи достаточно. Трудности, возникают при рабате с сообщениями произвольной длины и с выровненными сообщениями. Эти трудности можно преодолеть программным способом с некоторой потерей производительности, либо без потерь с использованием соответствующей аппаратной поддержки. Построение механизмов реализации разделяемой памяти над механизма передачи сообщений намного сложнее. Без поддержки со стороны аппаратуры все обращения к разделяемой памяти потребует привлечения ОС, как для обеспечения преобразованных адресов и защиты памяти, так и для преобразования обращений к памяти в передачу и прием сообщений. Т. к. операции чтения / записи обычно работают с небольшим объемом данных, то большие накладные расходы на поддержку такого обмена делают невозможной чисто программную реализацию. При оценке механизма обмена критичными являются 3 характеристики производительности:

1.Полоса пропускания.

2.Задержка.

3.Скрытие задержки. Насколько хорошо механизм обмена скрывает задержку путем перекрытия обмена с вычислениями или с другими обменами.

Каждый из этих параметров производительности воздействует на характеристики отдельно.

Мультипроцессорная когерентность КЭШ – памяти.

Значение элемента данных, хранящимся в 2-х различных процессорах, доступно этим программам только через их индивидуальный КЭШ. Это способствует возникновению проблем согласования между собой содержимого КЭШа разных процессоров. Обычно в малых мультипроцессорах используется механизм – протокол, позволяющий решить эту проблему. Такие протоколы называются протоколами когерентности КЭШ памяти. Существует 2 класса таких протоколов.

I. Протоколы на основе справочника (Directory Based). Информация о состоянии блока физической памяти при этом содержится только в одном месте – справочник. (Физический справочник может быть распределен).

II. Протоколы наблюдения (Snooping). При их использовании каждый КЭШ, который содержит копию данных некоторого блока физической памяти, имеет собственную служебную информацию о его состоянии. Централизованная система записи отсутствует. Обычно КЭШ расположена

98

на общей разделяемой шине, и контролеры КЭШ – памяти всех процессоров наблюдают за шиной для определения того, не содержат ли они копии передаваемого блока.

В мультипроцессорных системах, используются микропроцессоры с КЭШ – памятью, подключенные к централизованной общей памяти, протоколы наблюдения приобрели популярность, т. к. для обзора состояния КЭШа могут быть использованы заранее существующие физические соединения – шина памяти. Проблема когерентности памяти состоит в необходимости гарантировать, что считывание элемента данных возвращает последние по времени записанное в него значение. Вопрос о том, когда записываемое значение должно быть доступно процессору, выполняемому чтение, определяется выбранной моделью непротиворечивого состояния памяти и связан с реализацией синхронизации параллельных вычислений. Поэтому с целью упрощения предположим, что требование только, чтобы записанное операция записи значения было доступно операции чтения, возникшей немного позже записи, и что операция записи данного процессора всегда видны в порядке их выполнения. С данным определением согласно состоянию памяти, мы можем гарантировать когерентность путем обеспечения 2-х свойств.

1.Операция чтения ячейки памяти одним процессором, который следует за операцией записи в ту же ячейку памяти другим процессором, получит записанное значение, если чтение / запись достаточно отделены друг от друга по времени.

2.Операция записи в одну и ту же ячейку памяти выполняется строго последовательно, т. е. 2 подряд идущие операции записи в одну и ту же ячейку памяти будут наблюдаться другими процессорами именно в том порядке, в котором они появлялись в программе процессора, выполняющего эти операционные записи.

Это свойство называется последовательным выполнением или

сериализацией операционной записи.

Имеются 2 методики, поддерживающие описанную выше когерентность.

1.Заключается в том. Чтобы гарантировать процессору исключительные права доступа к элементу данных перед выполнением записи в этот элемент. Этот тип протоколов называется протоколом записи

саннулированием (write invalidate protocol), т. к. при выполнении записи он аннулирует другие копии. Это наиболее часто встречающийся протокол, как в схемах на основе справочников, так и в схемах наблюдения. Исключительное право доступа означает, что во время выполнения записи не существует никаких других копий элемента данных, в которые можно писать или из которых можно читать. Все другие копии элемента аннулированы.

2.Альтернативой (1) является обновление всех копий элемента данных в случае записи в этот элемент. Этот тип протокола называется протоколом записи с обновлением (write update protocol или write broadcast protocol). В

99

этом протоколе для снижения требований к полосе пропускания полезно отслеживать, является ли слово в КЭШ – памяти разделяемым объектом (нет). Разница в производительности между протоколами записи с обновлением и аннулированием определяется 3-мя характеристиками.

1.Несколько последовательностей оперативной записи в одно и то же слово не перемещающихся с оперативного чтения требует несколько трансляций при использовании протокола записи с обновлением, но только одной начальной операции аннулирования при использовании протокола записи с аннулированием.

2.При наличии многословных блоков в КЭШ – памяти каждое слово, записывающееся в блок КЭШа, требует трансляции при исполнении протокола с обновлением в то время, как только первая запись в слово блока нуждается в генерации операции аннулирования при использовании соответствующего протокола. Протокол записи с аннулированием работает на уровне блоков КЭШ – памяти в то время, как протокол записи с обновлением должен работать на уровне отдельных слов.

3.Задержка между записью слова в одном процессоре и чтения записанного слова другим процессором обычно меньше при использовании схемы записи с обновлением , т.к. записанные данные немедленно транслируются в процессор выполнения чтений, если этот процессор имеет копию данных, следовательно промаха при обращении к КЭШу не возникает. Эти 2 схемы во многом похожи на схему работы КЭШ – памяти со сквозной

иобратной записью.

100