3. Синтез входного преобразователя (шифратора).

Составляется таблица истинности входного преобразователя (табл. 14)

Таблица 14.

-

X1

X2

X3

x1

x0

0

0

0

-

-

0

0

1

1

0

0

1

0

0

1

0

1

1

-

-

1

0

0

0

0

1

0

1

-

-

1

1

0

-

-

1

1

1

-

-

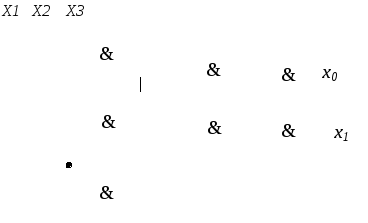

Диаграмма вейча для функции х0.

Таблица 15

|

Х1 |

Х2 Х3 | |||

|

00 |

01 |

11 |

10 | |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

Записывается выражение логической функции

![]() .

.

Диаграмма вейча для функции х1.

Таблица 16

|

Х1 |

Х2 Х3 | |||

|

00 |

01 |

11 |

10 | |

|

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

Записывается выражение логической функции

![]() .

.

Составляется принципиальная схема входного преобразователя в заданном базисе И-НЕ (рис. 2).

Рисунок 2 – Принципиальная схема входного преобразователя

4. Синтез выходного преобразователя (дешифратора).

Составляется таблица истинности выходного преобразователя (табл. 17)

Таблица 17.

-

y1

y0

Y1

Y2

Y3

Y4

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

0

1

Записываются логические выражения для каждого выходного сигнала

![]()

![]()

![]()

![]()

Составляется принципиальная схема выходного преобразователя в базисе И-НЕ (рис. 3).

Рисунок 3 – Принципиальная схема выходного преобразователя