Konspekt_lektsionnykh_zanyaty_MKvSU

.pdf

Таким образом, возможно обращение каждой процедуры к 32 регистрам. Соседние регистровые банки, используемые вызывающей и вызываемой процедурами, перекрываются, так что параметры могут быть переданы процедуре без какого-либо перемещения данных. На каждое обращение к процедуре назначается новый набор регистров R10...R31. При этом нижние регистры вызывающей процедуры становятся верхними вызываемой, поскольку они совмещены физически.

Таким образом, без перемещения информации параметры, хранящиеся в регистрах 10—15 вызывающей процедуры, появляются в регистрах 26—31 вызываемой. Рис. 1.3 иллюстрирует этот подход для случая, когда процедура А вызывает процедуру В, а та, в свою очередь, вызывает С.

Рис. 1.5.1

Во многих программах глубина вложенности процедур превышает число регистровых окон, поэтому в МП с берклийской архитектурой освобождение регистровых банков при переполнении регистрового файла осуществляется путем передачи их содержимого в память. Если глубина вложенности выходит за пределы логических наборов регистров, содержащихся в регистровом файле, то начинается программная или аппаратная обработка прерывания. Содержимое нескольких регистров передается в память, в отдельной области которой организован стек переполнения регистров. Сигналы переполнения/недополнения перемещают указатель стека на его вершину.

Эффективность такой организации обращения к процедурам зависит от частоты появления переполнений/недополнений, в большей степени связанной с логическими изменениями глубины стека, нежели с его абсолютной глубиной.

Исследования показали, что при восьми регистровых банках переполнения/недополнения возникают менее чем в 1% обращений к процедурам. Для того, чтобы к переменным в регистрах можно было обращаться с помощью указателей, все регистры отображаются в адресное пространство регулярной памяти.

Станфордская архитектура. Скорость обработки инструкций в МП с конвейерной архитектурой существенно снижается из-за возникновения конфликтных ситуаций следующего типа:

-программа осуществляет переход, для которого требуются очистка конвейера и загрузка его новыми инструкциями (зависимость по адресу);

-инструкции запрашивают информацию, которая еще не получена от обрабатываемых в конвейере инструкций (зависимость по данным);

21

-инструкциям в конвейере одновременно требуются обращения к одному и тому же ресурсу — шине памяти, регистру или АЛУ.

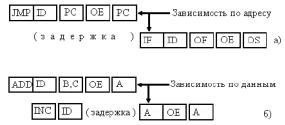

Возможны различные случаи задержки конвейера, содержащего пять ступеней обработки инструкции (рис. 6): выборку инструкции (IF), дешифрацию инструкции (ID), выборку операнда (OF), вычисление (ОЕ) и запоминание результата (OS). В первом случае (см. рис. 1.5.2,а) выполняется инструкция безусловного перехода JMP, что задерживает конвейер до тех пор, пока не завершится ее обработка, включающая четыре этапа:

-дешифрацию инструкции JMP,

-выборку операнда из программного счетчика PC,

-модификацию содержимого PC,

-запись результата обратно в программный счетчик; задержка в этом случае длится четыре такта.

Во втором случае (рис. 1.5.2,б] инструкция INC А не может выбрать операнд А, пока предыдущая инструкция ADD B, C, A не завершит запись результата операции в регистр А; задержка длится два такта.

Рис. 1.5.2

Такие конфликтные ситуации - зависимость по адресу и по данным, свойственны всем МП с конвейерной обработкой инструкций. Традиционно эти проблемы решаются аппаратно за счет опережающей выборки инструкций в точке перехода или за счет блокировки конвейера в случае возникновения конфликтной ситуации.

Станфордская архитектура предусматривает устранение задержек конвейера при помощи оптимизирующего компилятора, переупорядочивающего инструкции так, чтобы они не зависели одна от другой при обработке их в конвейере. При этом вводится инструкция задержанного перехода (табл. 2), которая применяется также и в некоторых RISC МП с берклийской архитектурой. Задержанный переход выполняется так, что инструкция, следующая за инструкцией перехода, выполняется до передачи управления в точку перехода. В это время процессор имеет возможность выбрать инструкцию по адресу перехода и загрузить ее в конвейер.

Традиционные МП реализуют этот фрагмент программы как обычный переход - инструкции выполняются в последовательности: 100, 101,102, 105 и т.д. Чтобы получить такой эффект в RISC МП, необходимо ввести в

задержанный переход инструкцию NOP, не выполняющую операций. Тогда последовательность станет такой: 100, 101, 102, 103, 106 и т.д.; обрабатывается она оптимизирующим компилятором, который по возможности переупорядочивает ее так чтобы максимально использовать цикл после задержанного перехода. Последовательность исполнения инструкций

22

принимает вид: 100, 101, 102, 105 и т.д. Поскольку инструкция, следующая за инструкцией перехода ,выполняется всегда и переход по адресу 101 не зависит от выполнения инструкции ADD по адресу 102, последовательность эта эквивалентна исходному фрагменту программы.

Таблица 2

Концепция задержанного перехода применяется в ряде случаев для выполнения инструкций обращения в память за один такт. Непосредственный способ выполнения этих инструкций требует двух тактов: один необходим для вычисления адреса, второй — собственно для обращения в память. Модифицированные инструкции обращения в память называются задержанными загрузками и предполагают некоторые изменения аппаратуры: память и регистры МП должны быть оснащены дополнительными портами. Зависимость по данным, которая может возникнуть при выполнении задержанной загрузки, устраняется при помощи оптимизирующего компилятора.

Для RISC МП со станфордской архитектурой характерно небольшое число регистров общего назначения, используемых для хранения локальных переменных и параметров процедур. Распределение регистров между переменными выполняется оптимизирующим компилятором.

Применение RISC - архитектуры в 32-разрядных МП

Каждой из рассмотренных разновидностей архитектуры присущи как достоинства, так и недостатки, поэтому обе они получили примерно одинаковое развитие и распространение.

Первые МП с архитектурой RISC (RISC I и RISС II) были разработаны и изготовлены в начале 80-х годов в Калифорнийском университете (г. Беркли). Они имели небольшой набор инструкций и простые режимы адресации. Все арифметические и логические инструкции выполнялись над регистровыми операндами, и только две — LOAD и STORE — использовались для обращения в память. На площади кристалла, освободившейся от схемы дешифрации сложных команд и формирователя последовательности микрокоманд, присущих традиционной архитектуре МП, размещен большой регистровый файл. Организация его в виде перекрывающихся регистровых окон позволяла каждой процедуре назначать новый набор регистров и передавать данные от

23

одной процедуры к другой простым изменением аппаратного указателя. Регистровые окна, впервые примененные в берклийских МП обеспечивают эффективную поддержку вложенных процедур, сокращают число обращений в память и значительно повышают производительность МП.

В 1983 г. в Станфордском университете был разработан и из-готовлен МП

MIPS (Microprocessor without Interlocked Pipeline Stages - микропроцессор без блокировок конвейера) . Целью проекта MIPS было создание МП, свободного от задержек конвейера, связанных: с выполнением переходов, зависимостью инструкций по данным и одновременным обращением нескольких инструкций, обрабатываемых в конвейере, к одному ресурсу. Благодаря разработке и применению оптимизирующего компилятора в МП MIPS удалось преодолеть недостатки берклийсиой архитектуры, обусловленные, прежде всего, необходимостью использования большого регистрового файла, занимающего до 60% площади кристалла.

Архитектура МП SOAR (Smalltalk On A RISC) является развитием берклийской ветви RISC. Он предназначен для поддержки языка высокого уровня Smalltalk-80 и функционирования в составе рабочей станции Sun. SOAR поддерживает два типа данных: 31-разрядные переменные со знаком и 28разрядные указатели. Каждое слово данных содержит признак типа (тег), который проверяется одновременно с выполнением арифметических операций. Если оба операнда оказываются целыми, то через один такт получается правильный результат. В противном случае SOAR обращается к программам обработки указателей. Другой особенностью его является использование инструкций групповой загрузки—хранения, позволяющих передавать содержимое восьми регистров за девять тактов вместо шестнадцати (один такт тратится на выборку инструкции и восемь — на обращения в память).

МП ARM (Acorn RISC Machine) разработан специально для персонального компьютера модели В фирмы Acorn Computers и воплощает основные принципы станфордской архитектуры. Он обладает небольшим набором аппаратно-реализованных инструкций, имеющих одинаковый 32-разрядный формат. Для обеспечения быстрой реакции на прерывания разработчики ARM исключили из его набора команд длинные операции, которые невозможно прервать. Как и МП SOAR, ARM поддерживает инструкции групповой загрузки—хранения, позволяющие повысить скорость обмена между МП и памятью. В отличие от других RISC МП, в ARM не используются задержанные переходы. Для устранения задержек конвейера при выполнении переходов в каждую инструкцию введено 4-разрядное поле кода условия; выполняется оно только в том случае, если установлен код соответствующего условия.

МП ROMP (Research/Office division Microprocessor) - микропроцессор отделения по автоматизации научных и Учрежденческих работ) корпорации IBM. Он предназначен для работы в качестве центрального процессора в персональном компьютере RT PC (RISC Technology Personal Computer),

реализует станфордскую архитектуру и оснащен развитым оптимизирующим компилятором.

24

Особенностью ROМР является длинное 40 - разрядное адресное слово и соответствующее ему адресное пространство 1Tбайт.

При разработке ROMP большое внимание уделялось повышению скорости обмена между процессором и памятью. Для этого используется аппаратно управляемый буфер преобразованных адресов, применявшийся в ранних моделях IBM. Он выполняет эффективное преобразование виртуальных адресов в физические. Кроме того, каждое слово данных в RОМР снабжается тегом, по которому определяется получатель данных, поэтому любой элемент данных может перебраться, как только он будет готов.

Центральный процессорный элемент (ЦПЭ) R2000 фирмы Mips Computer Systems составляет основу для построения супермини компьютеров этой фирмы. Он имеет станфордскую архитектуру, работает в программной среде ОС Umips, совместимой с ОС Unix, языков высокого уровня Си, Фортран-77 и Паскаль. Для управления внешней кэш-памятью используется буфер преобразованных адресов. R2000 работает в составе трехкристального набора, в который входят также сопроцессор для операций с плавающей точкой и буфер записи, предназначенный для согласования скоростей работы ЦПЭ и динамической памяти.

ЦПЭ MD 484 фирмы McDonnell Douglas изготавливается по GaAsтехнологии и имеет расчетную производительность 100 млн. инструкций в 1 с. Благодаря станфордской архитектуре, MD 484 содержит небольшое число компонентов (23,2 тыс. транзисторов и 10,4 тыс. резисторов) и поддерживает набор инструкций МП MIPS. Он имеет развитую систему прерываний, включающую прерывания из-за неправильной адресации, внутреннего переполнения и системных обращений. Для передачи инструкций и данных используются три двунаправленные 32-разрядные шины, каждая линия которых заряжается с помощью большого n-канального транзистора. Высокая производительность ЦПЭ обеспечивается за счет сопроцессора для операций с плавающей точкой и устройства управления памятью, входящих в МП набор.

МП SPARC (Scalable Processor ARChitecture) фирмы Sun Microsystems

воплощает основные принципы берклийской архитектуры: он содержит большой регистровый файл емкостью 120 32-разрядных регистров и использует задержанные переходы. МП реализован на вентильной матрице фирмы Fujitsu, выполненной по 1,5 мкм КМОП-технологии и содержащей 20 тыс. вентилей. МП SPARC предназначен для работы в программной среде ОС Unix в составе рабочей станции Sun-4.

МП Аm29000 фирмы AMD отличается наивысшей производительностью среди серийных RISC МП и реализует усовершенствованную версию берклийской архитектуры. В него входит регистровый файл емкостью 192 регистра, разделенный на банки по 16 регистров; использует он задержанные переходы для устранения задержек конвейера, вызванных зависимостью по адресу, и выполняет команды обращения в память за один такт благодаря применению концепции задержанной загрузки. Кроме того, для ускорения обмена между МП и внешней памятью в Аm29000 введен буфер преобразованных адресов.

25

Трехкристальный МП набор Clipper С100 корпорации Fairchild позволяет реализовать суперЭВМ на одной плате. Архитектура Clipper С100 имеет некоторые черты RISC, например аппаратную реализацию большинства инструкций, однако ее нельзя отнести ни к одному из рассмотренных выше классов. Этот МП способен выполнять все арифметические операции с плавающей точкой по стандарту IEEE 754, он поддерживает десять типов данных и девять режимов адресации, а его система прерываний включает 256 векторных прерываний и 128 системных обращений.

Набор инструкций Clipper С100 содержит 101 аппаратно-реализованную инструкцию и 67 макроинструкций, выполняющих преобразование чисел из формата с фиксированной точкой в формат с плавающей точкой и обратно, обработку символьных строк, хранение - восстановление регистров, обработку прерываний и другие операции. Для поддержки макроинструкций используется микропрограммное ПЗУ емкостью 1К 48-разрядных слов. Вычислительный модуль Clipper С100 работает в программной среде ОС Unix и языков высокого уровня Си, Фортрая и Паскаль.

МП система МС88000 фирмы Motorola включает процессор МС88100 и два кристалла памяти МС88200.

МС88100 содержит регистровый файл небольшой емкости, блоки обработки чисел в формате с фиксированной и плавающей точкой, а также до шести заказных блоков специальных функций.

МП имеет четыре порта ввода - вывода и поэтому может быть использован для построения мультипроцессорных систем.

Однокристальные МП. Однокристальные МП (ОМП) - функционально законченные процессоры с фиксируемыми разрядностью и набором инструкций. При этом инструкциями процессора являются инструкции ОМП. Обычно архитектура систем, построенных непосредственно на основе таких МП, повторяет архитектуру МП. Для построения системы достаточно подключить к ОМП блоки ОЗУ, ПЗУ, управления вводом-выводом информации и тактового генератора. ОМП различаются типом шин [типом набора проводников, функционально предназначенных для передачи информац. и (или) управляющих сигналов] адреса и данных: раздельные шины адреса и данных позволяют одновременно передавать по ним коды адреса и данных; совмещённые шины адреса и данных позволяют передавать адрес и данные в разные моменты времени, причём сначала производится адресация, т. е. выбор источника или получателя информации, а затем обмен данными. Такой способ, несмотря на большую сложность, позволяет сократить кол-во проводников шины и уменьшить кол-во выводов ОМП, что весьма существенно при увеличении его разрядности.

ОМП различаются также по способу синхронизации при выдаче адреса и обмена данными. В синхронных системах все сигналы строго определены во времени и обмен ведётся без подтверждения факта получения или выдачи информации абонентом.

В синхронно-асинхронных системах передача адреса осуществляется синхронно, а обмен происходит при взаимном обмене источника информации и

26

её получателя сигналами подтверждения приёма (передачи) информации по след, схеме:

-источник начинает цикл обмена, выставляя данные на шины, и с временной задержкой, необходимой для надёжной установки данных на линиях связи, выставляет сигнал данные на шине;

-получатель по сигналу данные на шине производит их запись и только после этого выставляет сигнал данные получены на соответствующую линию связи;

-источник, получив сигнал данные получены, снимает сигнал данные на шине и сами данные;

-получатель после снятия сигнала данные на шине снимает сигнал данные получены;

-источник после снятия сигнала данные получены завершает текущий цикл обмена.

Этот способ обеспечивает высокую надёжность обмена, т. к. менее чувствителен к помехам, сбоям и временным характеристикам как узлов, участвующих в обмене, так и линий связи.

Литература: 1 осн.[236-241]; 2 осн.[151-155].

Контрольные вопросы:

1. Основные понятия и определения.

2. Этапы развития МП и МП-систем.

3. Назовите основные компоненты, достоинства и недостатки различных архитектур МП.

4. Для чего нужен оператор?

5. Что показывает операнд?

6. Назначение АЛУ (арифметико-логическое устройство). 7. Что такое дешифратор команд?

8. Каковы функции блока управления?

9. Каковы функции блока управления?

10. Для микропроцессоров характерна трехшинная структура, что она содержит.

11. Что представляет собой программа для магазинного процессора.

12. Что такое шина данных?

Тема лекции 2: ПРИНЦИПЫ ОРГАНИЗАЦИИ ПРОЦЕССОВ ОБРАБОТКИ ИНФОРМАЦИИ.

Содержание темы: Организация шин в микропроцессорах (МП). Организация памяти в МП. Организация подсистем ввода/вывода. Базовая структура микропроцессорной системы. Основные характеристики МПС и их классификация. Отличия и общие черты PLC, RTU, РСУ, резервируемых систем.

Принципы организации процессов обработки информации.

Микропроцессорной системой (МПС) называется система цифровой обработки информации и управления, содержащая в своем составе, по крайней мере, один микропроцессор (МП), один или несколько модулей основной (ОЗУ и ПЗУ) и дополнительной памяти, устройства ввода и вывода, блоки сопряжения

27

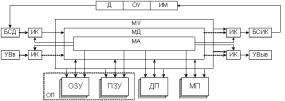

(контроллеры) с устройствами ввода и вывода, которые связаны друг с другом с помощью системной магистрали, состоящей, в общем случае, из магистралей (шин) адресов (МА, ША), магистралей (шин) данных (МД, ШД) и магистралей (шин) управления (МУ, ШУ).

Логическая структура МПС приведена на рис.1.1, где ОУ – объект управления, Д – датчики, ИМ – исполнительные механизмы, ИК – информационные контроллеры, БСД – блок сопряжения с датчиками, БСИК – блок сопряжения с информационными контроллерами, ОП – основная память, ДП – дополнительная память.

Рис. 1.1. Логическая структура МПС ОЗУ МПС обеспечивает чтение и запись информации и реализуется как

энергозависимая память, содержимое которой стирается при выключении МПС. ПЗУ обеспечивает только чтение информации и реализуется в виде энергонезависимой памяти. Контроллеры представляют собой устройства сопряжения аппаратуры ввода-вывода с системной магистралью и реализуют определенный интерфейс. Магистраль обеспечивает коммуникацию аппаратных средств МПС и представляет собой набор проводников и усилителей сигналов.

В зависимости от областей применения МПС подразделяются на специализированные и универсальные, встроенные и автономные.

Основой любой МПС является микроЭВМ - вычислительная или управляющая система, выполненная на основе МП, в состав которой, как правило, входят: постоянная (программируемая) память программ (ПЗУ), память данных (ОЗУ), генератор тактовых импульсов и информационный контроллер, построенные на основе БИС или СБИС.

По способу реализации микроЭВМ подразделяются на однокристальные, одноплатные и многоплатные. В одноплатных микроЭВМ МП выполняется в виде кристалла БИС (СБИС), на котором кроме самого МП могут располагаться и другие компоненты микроЭВМ (ПЗУ, ОЗУ, контроллеры и т.п.).

По назначению микроЭВМ разделяются на универсальные и специализированные (проблемно-ориентированные).

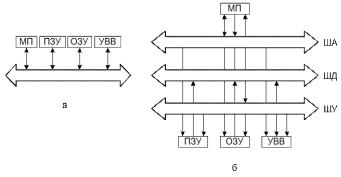

По организации структуры различают одно- и многомагистральные микроЭВМ (рис. 1.2).

28

Рис. 1.2. Общая структура ЭВМ: а – одномагистральная;

б– многомагистральная

Водномагистральных микроЭВМ все устройства имеют одинаковый интерфейс и подключены к единой информационной магистрали, по которой передаются данные, адреса и управляющие сигналы. В многомагистральных микроЭВМ устройства группами подключаются к своей информационной магистрали, что позволяет осуществить одновременную передачу по нескольким (или всем) магистралям и тем самым увеличить быстродействие системы.

Центральной частью МПС является микропроцессор - обрабатывающее устройство, выполненное с использованием технологии БИС (часто на одном кристалле) и обладающее способностью выполнять под программным

управлением обработку информации (включая |

ввод-вывод), принятие |

решений, арифметические и логические операции. |

|

Литература: 1 осн.[236-241]; 2 осн.[151-155]. |

|

Контрольные вопросы: |

|

1.В каком режиме работает ОЗУ?

2.В каком режиме работает ПЗУ?

3.Что называется микрокомпьютером?

4.Назовите основные характеристики шины?

5.Из каких основных блоков состоит микропроцессор?

6.Назначение блока программной памяти (БПП).

7.Назначение счетчика команд.

Тема лекции 3: БАЗОВАЯ СТРУКТУРА МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ.

Содержание темы: Основные характеристики МПС и их классификация. Отличия и общие черты PLC, RTU, РСУ, резервируемых систем.

характеристики МП. Развитие технологии и микроэлектронных схем привело к созданию БИС и СБИС, представляющих собой универсальные по назначению функционально-законченные устройства и по своим функциям и структуре напоминающие упрощенный вариант процессора обычных ЭВМ, но имеющие несравнимо меньшие размеры. Такие БИС получили название микропроцессора.

МП – это микросхема или совокупность небольшого числа микросхем (соответственно 1 или несколько кристаллов БИС), выполняющая над данными арифметические и логические операции и осуществляющая программное управление вычислительным процессом.

29

Микропроцессорные средства выпускаются в виде наборов совместимых по уровню напряжения питания, сигналом и представлением информации БИС и СИС, включающих МП, микросхемы оперативной постоянной памяти, управления вводов выводом, генератора тактовых сигналов и др.

МП служат основой для создания различных универсальных и специализированных микроЭВМ, микропроцессорных информационных управляющих систем, программируемых микроконтроллеров, разнообразных микропроцессорных приборов и устройств контроля, управления и обработки данных.

Микрокомпьютеры с небольшими вычислительными ресурсами и упрощенной системой команд ориентированы не на производство вычислений, а на выполнение процедур логического управления различным оборудованием, называют программируемым микроконтроллером или просто контроллером.

К основным характеристикам МП можно отнести следующие показатели:

Тип микроэлектронной технологии, используемой при изготовлении микропроцессорных БИС;

Длину слова (количество разрядов), обрабатываемого МП;

Быстродействие МП (тактовая частота, время выполнения команд основных операций);

Емкость адресуемой памяти;

Тип управляющего устройства (схемное или микропрограммное управление);

Эффективность системы команд (количество команд, выполняемые операции, возможные способы адресации, наличие команд работы со стековой памятью, команд операций с битами, десятичными числами, числами с плавающей точкой и т.п.);

Число уровней прерывания;

Пропускная способность интерфейса ввода вывода;

Номинальные параметры используемых сигналов;

Число входящих в микропроцессорный набор дополнительных микросхем и выполняемые ими функции;

Наличие и доступность для пользователя программных средств поддержки проектирования программ для МП и отладки микропроцессорных устройств и систем.

Все многообразие МП удобно делить на два различных типа:

1.Однокристальные МП с фиксированной разрядностью слова, с фиксированной системой команд и, как правило, с управляющим устройством со схемной логикой;

2.Многокристальные (секционные) программируемые МП с изменяемой разрядностью слова и с фиксированным набором микроопераций.

МП первого типа имеют логическую организацию, напоминающую организацию процессов обычных ЭВМ. Однокристальные МП выполняются с использованием различных МОП-технологий микроэлектроники, позволяющих

30