- •3.Дифференцирующие и интегрирующие цепи

- •5.Стабилизатор напряжения

- •6.Усилительный каскад на биполярном транзисторе с общим эмиттером.

- •7.Усилители мощности

- •8.Дифференциальные усилители

- •9.Операционный усилитель. Основные характеристики.

- •Простейшее включение оу

- •Классификация оу По типу элементной базы

- •10. Отрицательная обратная связь. Свойства оу с отрицательной обратной связью

- •11.Инвертирующий усилитель на оу

- •12.Неинвертирующий усилитель на оу

- •13.Суммирующий усилитель на оу

- •15.Дифференциатор

- •Идеальный дифференциатор

- •Реальный дифференциатор

- •Компараторы

- •16.Логарифмические и экспоненциальные преобразователи на оу

- •17.Активные фильтры на оу

- •14.Интегрирующие усилители Интеграторы

- •Реальный интегратор

- •18.Генератор синусоидальных колебаний

- •19.Триггер Шмитта

- •20.Генератор прямоугольных импульсов

- •21. Основные логические элементы и, или, не. Примеры схемотехнической реализации.

- •22. Логич. Элементы и-не.Пример схемотехнической реализации. Реализация логических функций и, или, не.

- •23. Логич. Элементы или-не.Пример схемотехнической реализации. Реализация логических функций и, или, не.

- •24. Входы и выходы цифровых микросхем.

- •25. Асинхронный rs тригер

- •26.Синхронный crs триггер

- •29. Jk триггер

- •30. Параллельные регистры Стробируемые регистры

- •4.2.2. Тактируемые регистры

- •31.Регистры сдвига

- •32.Суммирующие счетчики

- •33.Вычитающие счетчик

- •34. Сумматор

- •35. Сложение двоичных чисел со знаком

- •40.Цап с матрицей резисторов r-2r

- •42.Ацп последовательного счета

23. Логич. Элементы или-не.Пример схемотехнической реализации. Реализация логических функций и, или, не.

Схемы отличаються от 22 вопроса только тем что используються элементы ИЛИ-НЕ вместо И-НЕ. Логические выражение меняються для:

НЕ: x+0=x x+x=x

ИЛИ: y=x1+x2=не(не(x1+x2))

И: y=x1x2=не(не(x1*x2))=не(нех1+нех2)

24. Входы и выходы цифровых микросхем.

Интегральные схемы изгоавливаются в виде отдельного корпуса который имеет набор выводов: входы, выходы, заземление, питание.

Каждая цифровая схема преобразует последовательность входных сигналов в последовательность выходных. Способ преобразования обычно описывают с помощью логической функции, таблиц истинности в виде временных диаграм

Входы и выходы микросхемы ТТЛ (в конспекте только про нее написано)

Входы: |

1)

|

2)

|

|

Не используемые входы: |

|

||

Выходы: |

|

2с - обычный, на вых либо 0 либо 1 0К – открытый коллект. Не подключаеться к общему источнику питания. 3с – выход с тремя сост. (Z state). Имеет состояния 0 и 1, либо отключен. Если используеться 3 состояния то имееться доп. вход Ez и если он 0 то Z state, если 1 то Z=2C |

|

25. Асинхронный rs тригер

Триггер в котором при поочередном поступлении импульсов на установочные входы изменяеться состояние тригера.

S (set) – вход установки триггера в 1.

R (reset) – вход установки триггера в 0

При подаче активного уровня на R триггер = 0, акт. Уровень на S триггер = 1, два активных уровня – триггер не работает, два низких уровня – режим хранения памяти.

Таблица истиности:

Qn |

R |

S |

Qn+1 |

Не Qn+1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

- |

- |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

- |

- |

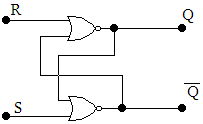

Схема тригера в базисе ИЛИ-НЕ

|

|

26.Синхронный crs триггер

На Рис.3.15. представлено условное обозначение (а), схема (б), и диаграмма работы (в) синхронного RS триггера.

Как видно из диаграммы до прихода тактовых триггер находится в состоянии 1 (выход Q=1). В момент времени t1 на вход С поступает импульс синхронизации, в этот момент времени на входе R триггера присутствует сигнал логической 1, а на входе S сигнал логического 0, что вызывает переключение триггера в состояние «0» по прямому выходу Q.

В момент времени t2 на вход С поступает следующий импульс синхронизации, в этот момент времени на входе S триггера присутствует сигнал логической 1, а на входе R сигнал логического 0, что вызывает переключение триггера в состояние «1» по прямому выходу Q.

В момент времени, когда на входах R и S триггера присутствует одновременно сигнал логической 1 переход триггера в запрещенную комбинацию не осуществляется в связи с тем, что отсутствует импульс синхронизации на входе С.

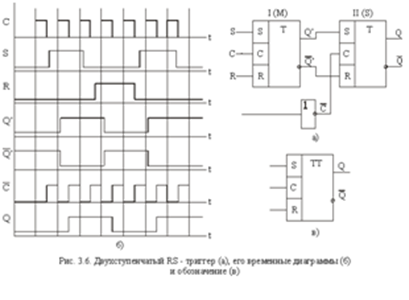

27.Двухступенчатый СRS - триггер. Применение одноступенчатых RS-триггеров в качестве самостоятельных запоминающих элементов ограничено. Это связано с неустойчивой работой последовательностной схемы (цифрового автомата), память которой выполнена на одноступенчатых RS-триггерах. Сигналы переключения триггера S(t), R(t) формируются в цифровом автомате комбинационной схемой, в их формировании участвуют, наряду с внешними логическими сигналами, сигналы Q(t) и Q(t)(c инверсией). Переключение одноступенчатого триггера под действием сигналов S(t) и R(t) вызывает изменение значений сигналов Q(t) и Q(t)(c инверсией), а их изменение может привести к изменениям сигналов S(t) или R(t) в том же такте времени t и, как следствие, к ложному срабатыванию триггера. Для устойчивой работы триггера необходимо, чтобы сигналы Q(t) и Q(t)(c инверсией)изменялись только после прекращения действия входного сигнала S(t) или R(t). Это требование выполняется в двухступенчатых триггерах (MS-триггерах). Базовыми схемами для построения двухступенчатых триггеров являются одноступенчатые RS-триггеры. Двухступенчатый триггер состоит из двух секций (ступеней), соединенных каскадно, как показано на рис. 3.6 а, причем, каждая секция содержит по синхронному RS-триггеру. Первая секция, ведущая или М-секция (М происходит от английского MASTER) принимает информацию со входных линий S и R. Состояние выходов ведущей секции подается на вторую секцию, ведомую, или S-секцию (S происходит от английского SLAVE).

Для ведущего триггера используется обычная синхронизация, в то время как для ведомого триггера импульс синхронизации инвертируется. Изменение состояния выхода ведущего триггера будет происходить в момент появления положительного импульса синхронизации, и эти изменения будут переданы на входы ведомого триггера. Однако, никакие изменения на выходе ведомого триггера не будут происходить до тех пор, пока не появится положительный сигнал инвертированного импульса синхронизации, т.е. отрицательный (задний фронт) фронт исходного синхроимпульса. Следовательно, изменения на выходах Q и Q(t)(c инверсией) не произойдет до тех пор, пока не завершится импульс синхронизации. На рис. 3.6, б показаны временные диаграммы работы триггера.

28.D-Триггер

D-триггер (иначе триггер задержки) является самым распространенным триггером. Он имеет один информационный вход D (вход данных) и один тактовый вход C.

Тактируется триггер (то есть меняет свое состояние) по положительному фронту сигнала С (по его переходу из нуля в единицу) в зависимости от состояния входа данных D. Если на входе D единичный сигнал, то по фронту сигнала С прямой выход триггера устанавливается в единицу (инверсный — в нуль). Если же на входе D - нулевой сигнал, то по фронту сигнала С прямой выход триггера устанавливается в нуль (инверсный - в единицу).

Остановимся на работе D-триггера чуть подробнее, так как он наиболее часто используется.

Ранее говорилось, что RS и -R-S триггера редко используются как самостоятельные, но могут быть использованы для построения триггеров с установочными входами. Условное обозначение такого триггера представлено на Рис. 3.17(а), диаграмма его работы на Рис. 3.17(б).

Как следует из диаграммы (Рис.3.17) в момент t1 работа триггера определяется установочным сигналом на входе – R (логический «0») – триггер перебрасывается в состояние «0». Нулевое состояние триггера сохраняется до момента t2, когда сигналы на установочных входах неактивны, на входе D присутствует сигнал «1», а на входе С – положительный фронт, что обеспечивает переключение триггера из состояние «0» в состояние «1».

В момент t2 работу триггера определяет вход D (логический «0») и положительный фронт сигнала С (триггер переходит в состояние «0»).

В момент t3работу триггера определяет установочный вход –S, который обеспечивает его переключение в состояние «1».

Следует отметить, что согласно схемотехнической организации триггера с установочными входами при одновременном действии сигналов на один из установочных входов, на информационный и вход С, состояние триггера определяет установочный вход.

На установочные входы –R–S активные сигналы (–R=–S=0) одновременно поданы быть не могут (согласно схеме –R–S триггера это запрещенная комбинация).

Все приведенные временные диаграммы относятся к первому уровню представления, к уровню логической модели. Конечно же, в реальности все триггеры имеют временные задержки установки выходных сигналов, а также предъявляют определенные временные требования к входным сигналам, при нарушении которых любой триггер будет работать неустойчиво или же не будет работать вообще. Это учитывается на втором уровне представления (в модели с временными задержками).

Длительность тактового сигнала C (как положительного, так и отрицательного импульса) не должна быть слишком малой, иначе триггер может переключаться неустойчиво. Это требование универсально для всех микросхем, срабатывающих по фронту входного сигнала.

Принципиально важна и величина временного сдвига (задержки) между установлением сигнала D и рабочим (положительным) фронтом сигнала C. Этот сдвиг тоже не должен быть слишком малым.

Не должен быть чрезмерно малым и сдвиг между окончанием сигналов –R и –S и рабочим фронтом сигнала С.

Повышенные требования предъявляются также к длительности фронта тактового сигнала С, которая не должна быть слишком большой. Это требование также универсально для всех микросхем, срабатывающих по фронту входного сигнала.

Т.е., чем сложнее микросхема, тем важнее для нее становятся ограничения второго уровня представления, тем выше требования к разработчику цифрового устройства по учету временных задержек и длительностей сигналов.

Следует обратить внимание на то, что цифровые схемы не любят слишком коротких входных сигналов и слишком малых задержек между входными сигналами, функционально связанными между собой. Ориентир здесь очень простой — величина задержки логического элемента данной серии. Поэтому для более быстрых серий ограничения будут менее жесткими, а для более медленных серий — более жесткими.

Несмотря на свою достаточно сложную внутреннюю структуру, микросхемы триггеров являются одними из самых быстрых. Задержка срабатывания триггера обычно не превышает 1,5–2 задержки логического элемента. (причем задержки по входам –R и –S чуть меньше, чем по тактовому входу С.) В некоторых сериях JK-триггеры несколько быстрее, чем D-триггеры, в других — наоборот.

Важный параметр триггера — максимальная частота тактового сигнала С. Для ее приблизительной оценки можно придерживаться следующего простого правила: период тактового сигнала С не должен быть меньше величины задержки переключения триггера по входу С.