- •3.Дифференцирующие и интегрирующие цепи

- •5.Стабилизатор напряжения

- •6.Усилительный каскад на биполярном транзисторе с общим эмиттером.

- •7.Усилители мощности

- •8.Дифференциальные усилители

- •9.Операционный усилитель. Основные характеристики.

- •Простейшее включение оу

- •Классификация оу По типу элементной базы

- •10. Отрицательная обратная связь. Свойства оу с отрицательной обратной связью

- •11.Инвертирующий усилитель на оу

- •12.Неинвертирующий усилитель на оу

- •13.Суммирующий усилитель на оу

- •15.Дифференциатор

- •Идеальный дифференциатор

- •Реальный дифференциатор

- •Компараторы

- •16.Логарифмические и экспоненциальные преобразователи на оу

- •17.Активные фильтры на оу

- •14.Интегрирующие усилители Интеграторы

- •Реальный интегратор

- •18.Генератор синусоидальных колебаний

- •19.Триггер Шмитта

- •20.Генератор прямоугольных импульсов

- •21. Основные логические элементы и, или, не. Примеры схемотехнической реализации.

- •22. Логич. Элементы и-не.Пример схемотехнической реализации. Реализация логических функций и, или, не.

- •23. Логич. Элементы или-не.Пример схемотехнической реализации. Реализация логических функций и, или, не.

- •24. Входы и выходы цифровых микросхем.

- •25. Асинхронный rs тригер

- •26.Синхронный crs триггер

- •29. Jk триггер

- •30. Параллельные регистры Стробируемые регистры

- •4.2.2. Тактируемые регистры

- •31.Регистры сдвига

- •32.Суммирующие счетчики

- •33.Вычитающие счетчик

- •34. Сумматор

- •35. Сложение двоичных чисел со знаком

- •40.Цап с матрицей резисторов r-2r

- •42.Ацп последовательного счета

4.2.2. Тактируемые регистры

Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера.

По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

На Рис.4.11. представлена схема регистра на D триггерах, в котором данные в прямом коде подаются на входы D1,D … Dm.

Запись информации осуществляется фронтом сигнала Тзап (тактовый командный импульс) одновременно поступающего на входы С всех триггеров.

|

Рис.4.11. Запись информации параллельным кодом |

На Рис.4.12. представлена схема регистра на JK триггерах. В данной схеме данные подаются парафазным кодом (прямой код D1,D … Dm – на вход J, обратный кода – на вход К).

|

Рис.4.12. Запись информации парафазным кодом |

Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0 . . . Dm новой цифровой комбинации (информации) при поступлении определенного уровня (регистр на асинхронных триггерах или запись осуществляется по установочным входам триггера) или фронта синхросигнала (синхроимпульса) Тзап=С на вход «С» регистра (синхронные триггера с записью по информационным входам).

31.Регистры сдвига

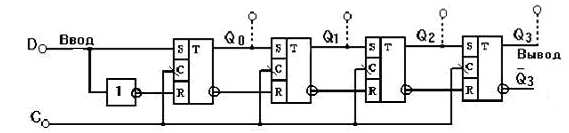

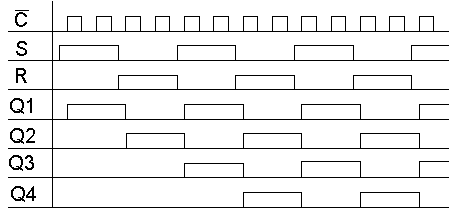

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, последовательно соединенную цепочку триггеров.

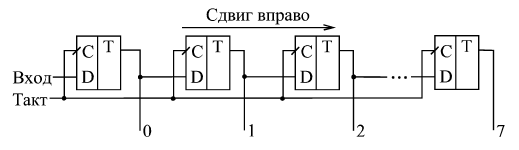

Т.е. в сдвиговых регистрах все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа.

На схемах символом регистра служат буквы RG. Для регистров сдвига указывается также направление сдвига:

→ вправо (основной режим, который есть у всех сдвиговых регистров);

← влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров);

↔ реверсивный (двунаправленный), т. е. записанную информацию можно сдвигать по линейке триггеров вправо или влево. Для включения режима сдвига предусматривают специальный управляющий вход.

Направление сдвига отражают внутреннюю структуру регистров сдвига (Рис. 4.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до 8) для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево - это сдвиг в сторону разрядов, имеющих меньшие номера.

Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа - младшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево - сдвигом в сторону старших разрядов. О такой особенности необходимо помнить разработчику цифрового прибора.

Рис. 4.14. Направление сдвига в сдвиговых регистрах

Регистры сдвига могут выполнять функции хранения и преобразования информации.

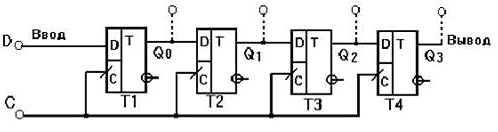

Регистры сдвига чаще все6го реализуются на D-триггерах (Рис.4.15, а) или на RS-триггерах (Рис.4.15, б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер).

Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса.

Регистры сдвига могут быть построены и на триггерах одноступенчатой структуры. В этом случае в каждом разряде регистра нужно использовать два триггера, которые управляются двумя сдвинутыми во времени тактовыми импульсами. Если бы в регистре были применены одноступенчатые триггеры по одному на разряд, то правило работы регистра было бы нарушено: при первом же импульсе сдвига информация, записавшись в первый разряд, перешла бы во второй, затем в третий и т.д.

Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав.

Работу регистра сдвига рассмотрим на примере схемы, приведенной на Рис. Рис.4.15.

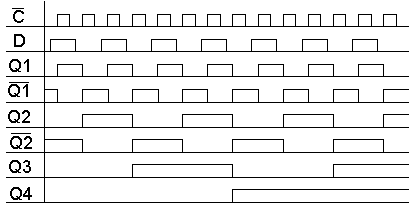

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы «С» триггеров не меняет их состояния.

Как следует из Рис.4.15, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 - уровни логического «0», т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического «0», а на вход «D» первого триггера, по условию примера, подается «0» из внешнего источника информации.

При подаче на вход «D» первого триггера «1», с приходом первого синхроимпульса, в этот триггер запишется «1», а в остальные триггеры - «0», т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 «ещё» присутствовал логический «0». Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе «D» в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая «1» , с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной «1» с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д.. Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

|

|

|

|