- •План лекции. Лекция 10.

- •Режиме прямого доступа к памяти (пдп).

- •Общая структура мпс.

- •Модель внешнего устройства (ву) мпс.

- •Программный режим обмена информацией в мпс.

- •Режим обмена информацией по прерываниям.

- •Режиме прямого доступа к памяти (пдп)

- •Архитектура мп.

- •Система команд

- •Cisc и risc архитектуры.

- •Структура программы

- •Локальные. @ Имя Помеченный оператор

- •Использование регистров.

План лекции. Лекция 10.

Общая структура МПС.

Модель внешнего устройства (ВУ) МПС.

Программный режим обмена информацией в МПС.

Режим обмена информацией по прерываниям.

Режиме прямого доступа к памяти (пдп).

Архитектура МП.

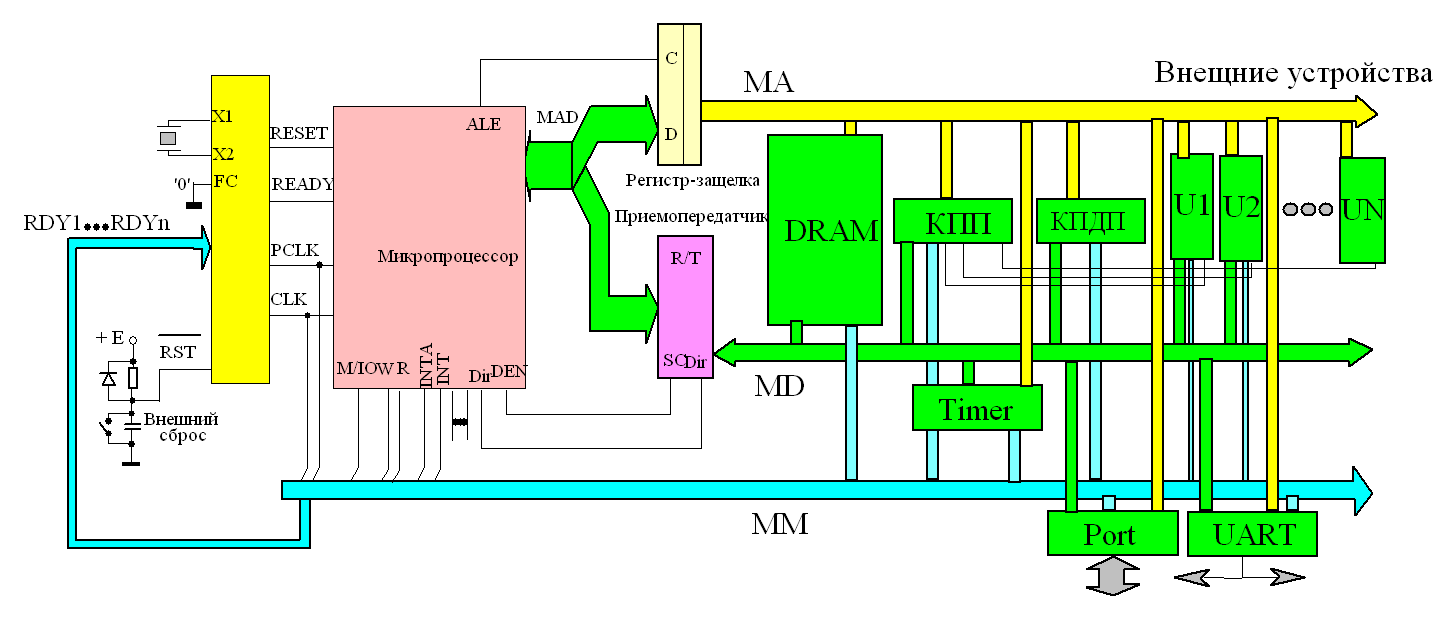

Общая структура мпс.

|

Рис. 91 |

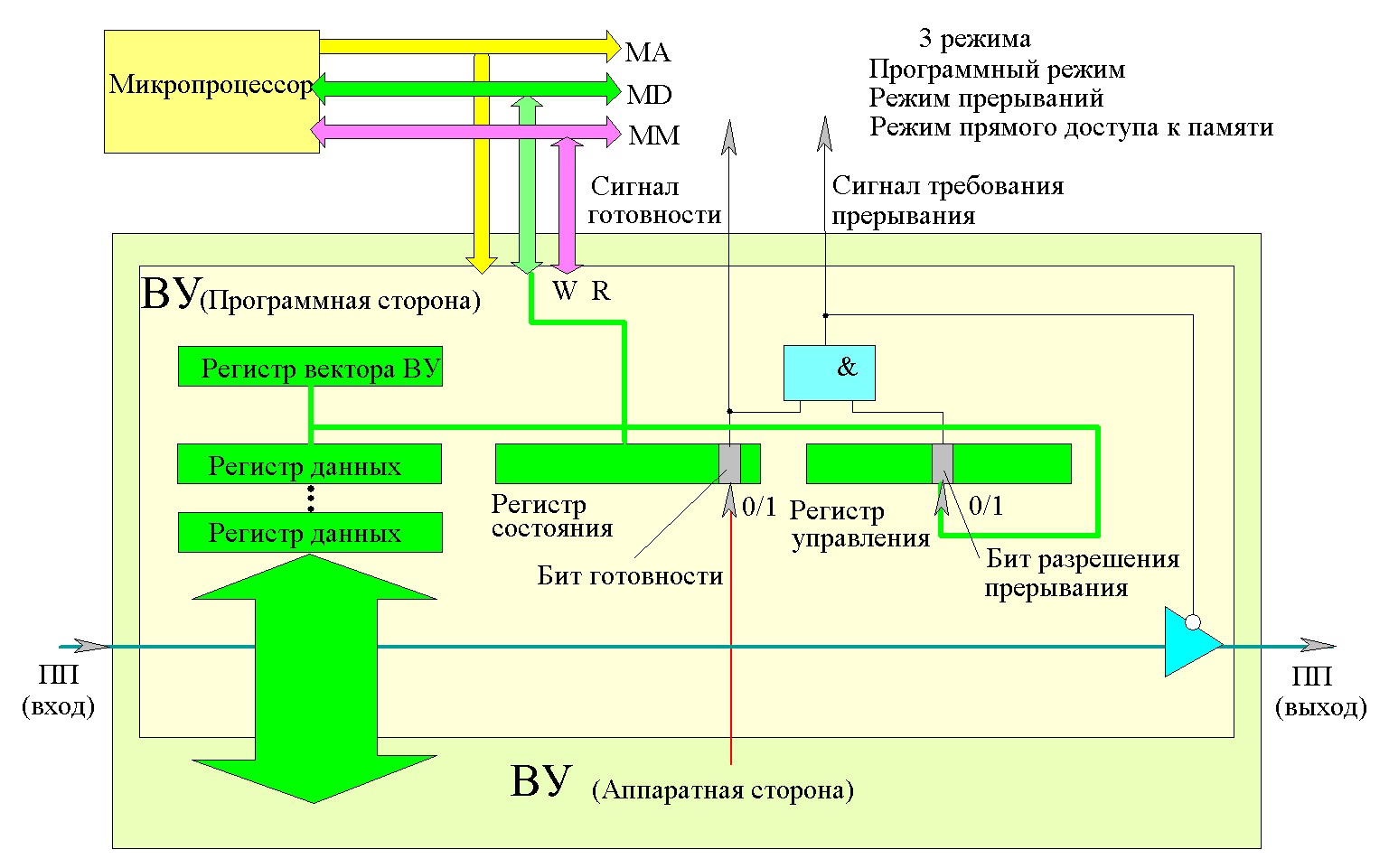

Модель внешнего устройства (ву) мпс.

|

Рис. 92 |

Программный режим обмена информацией в мпс.

Режим чтения или записи информации в МПС инициированный командами исполняемой программы называют программным обменом. |

Программный обмен с памятью (ОЗУ) осуществляется в синхронном режиме (время доступа к любой ячейке одинаково). Процессор выводит на МА адрес ячейки памяти, с которой происходит операция чтения∕записи. Осуществляется дешифрация адреса и выбор ячейки. Ячейка соединяется с МД. По команде R ∕W происходит операция чтния∕записи. В программе используют команды:

MOV ПриемникДанных, [AдресЯчейки] ! чтение из памяти (←);

MOV [AдресЯчейки], ИсточникДанных ! запись в память (←);

…

Программный обмен с внешним устройством (ВУ) осуществляется в асинхронном режиме (устройство может быть не готово к обмену данными по разным причинам). Процессор выводит на МА адрес регистра состояния ВУ, читает его содержимое (как и при работе с ОЗУ) и проверяет значение бита готовности ВУ (рис. 92). Если устройство готово, осуществляется обмен, иначе выполняется цикл повторной проверки готовности (ожидания готовности). В программе используют команды:

если общая магистраль –

MOV ПриемникДанных, [AдресРегистраВУ] ! чтение из ВУ (←);

MOV [AдресРегистраВУ], ИсточникДанных ! запись в ВУ (←);

…

если разделенная магистраль –

IN ПриемникДанных, [AдресРегистраВУ] ! чтение из ВУ (←);

OUT [AдресРегистраВУ], ИсточникДанных ! запись в ВУ (←);

Программный режим обмена обеспечивается циклическим опросом битов готовности всех ВУ. В исполняемой процессором программе (главной программе) должны быть встроены циклически повторяющиеся команды проверки битов готовности ВУ. Этот процесс занимает значительное процессорное время, которое может быть с пользой потрачено для решения текущей задачи обработки информации.

Режим обмена информацией по прерываниям.

Режим, при котором функционирование процессора инициировано внешним устройством называют режимом прерывания. |

Этот режим характерен только для работы с ВУ (для ОЗУ он не имеет смысла).

Готовность ВУ к обмену часто носит случайный характер. Это заставляет использовать альтернативный не программный режим взаимодействия процессора с ВУ. Такой режим носит название обмена информацией по прерыванию.

Инициируют прерывания ВУ. На специальной линии они устанавливают сигнал «требование прерывания». Этот сигнал (рис. 92) формируется в ВУ (на элементе &) на основании его внутренней готовности и программируемого разрешения работать в режиме прерывания (бит разрешения в регистре управления ВУ).

При поступлении сигнала «требование прерывания» процессор:

прекращает выполнение текущей программы;

запоминает (в стеке) своё внутреннее состояние и адрес возврата для возможного продолжения выполнения программы;

определяет номер источника прерывания (есть два способа рис.93,94);

используя этот номер как ссылку на ячейку оперативной памяти, процессор извлекает из нее адрес начала подпрограммы и переходит к её исполнению.

Эта подпрограмма носит название подпрограммы обслуживания прерывания ВУ. Поэтому в оперативной памяти МПС должно быть выделено место для хранения начальных адресов подпрограмм обслуживания ВУ.

после выполнения подпрограммы извлекает из стека информацию о возврате к прерванной программе и продолжает её выполнение.

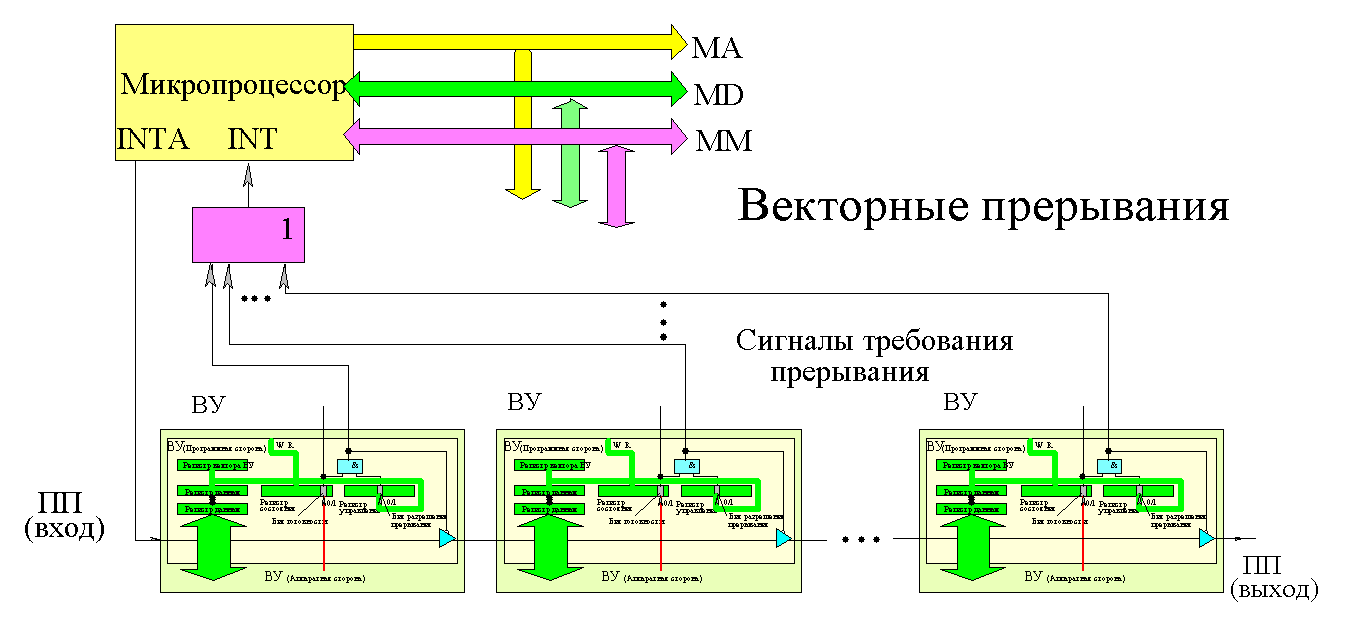

Существует два способа определения номера источника прерывания:

цепочечный (векторный);

радиальный.

При цепочечном способе процессор посылает сигнал предоставления прерывания (ПП) в линию, которая проходит через все устройства (рис.93). Устройство, запросившее прерывание, блокирует передачу этого сигнала дальше и, таким образом, обозначает себя. В регистре вектора этого ВУ (рис.92) процессор находит адрес подпрограммы обслуживания прерывания (или ссылку на адрес).

|

Рис. 93 |

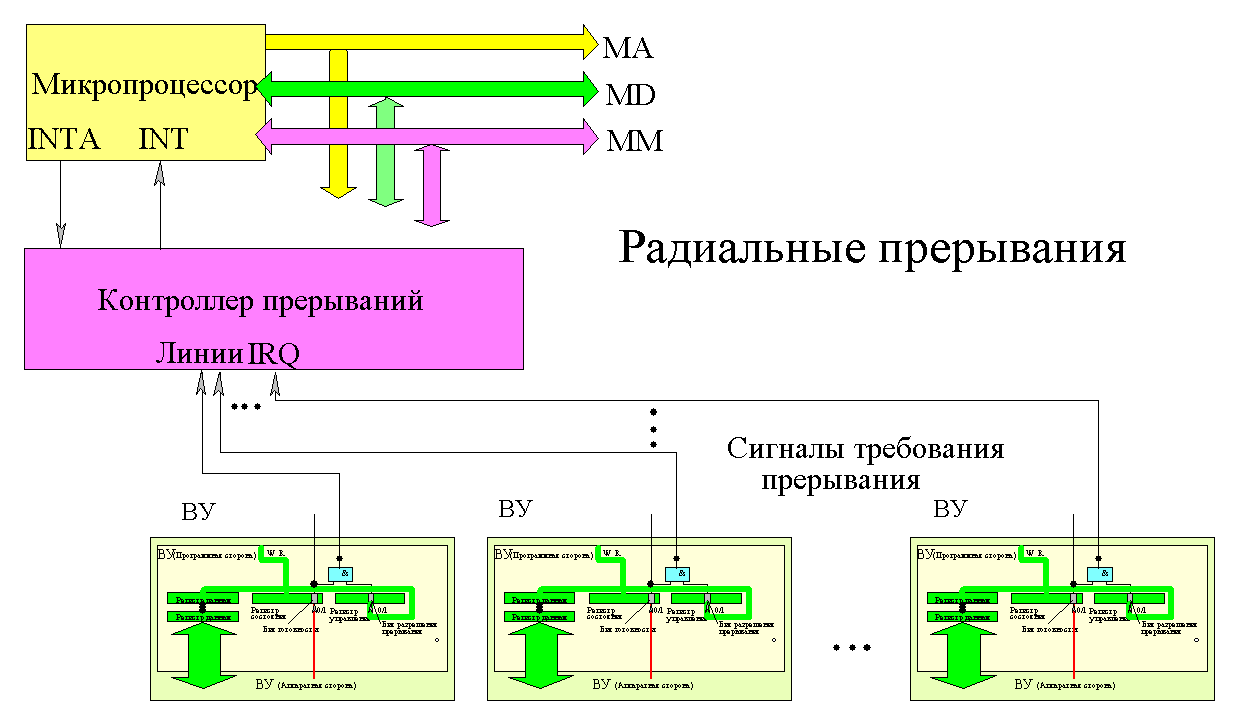

Радиальные прерывания используют специальное устройство – контроллер прерываний.

|

Рис. 94 |

Процессор посылает сигнал предоставления прерывания в контроллер, который возвращает ему номер ВУ (рис.94). Этот номер является адресом ячейки, где лежит ссылка (адрес) на подпрограмму обслуживания прерывания. Процессор переходит на её выполнение.

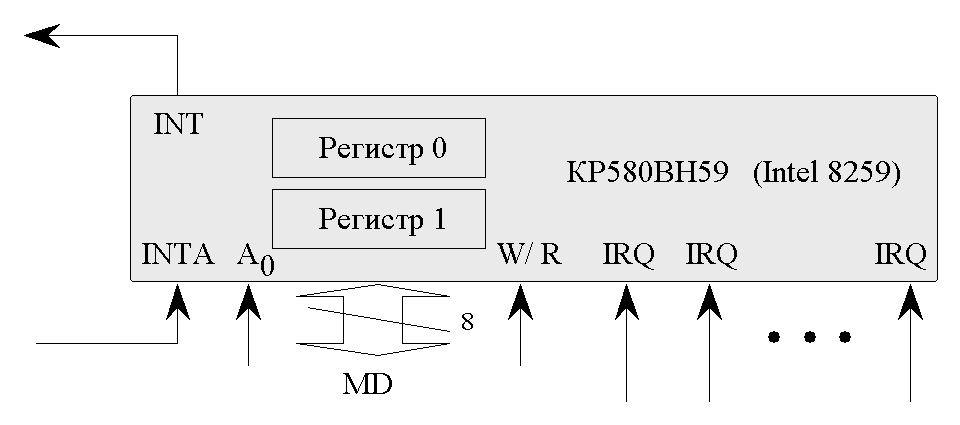

Реальная схема контроллера КР580ВН59 (рис. 95). Линии IRQ – входы сигналов требования прерывания от ВУ (рис. 92). Линия INT – общий сигнал требования прерывания на процессор. Линия INTA – сигнал разрешения прерывания из процессора. По МД происходит связь с внутренними регистрами. Регистры программируются для выполнения внутренних задач выбора приоритетов линий IRQ и управления контроллером.

|

Рис. 95 |