- •1. Архітектура мп к580 вм80

- •2. Структурна схема мп к580 вм 80

- •3. Призначення вхідних/вихідних сигналів мп к580 вм 80

- •4. Цикли роботи мп к580 мп вм 80.

- •Фаза вибору - це час, за який команда вибірається з пам’ті та записується в регістр команд (рк).

- •5. Способи адресації мп к580 вм80.

- •6. Загальна характеристика системи команд.

- •7 Команди пересилки

- •8 Арифметичні команди

- •9 Логічні команди.

- •10. Команди розгалуження, виклику підпрограм, повернення та рестарту.

- •11. Команди роботи зі стеком та керування вводу/виводу.

- •12. Генератор тактових імпульсів к580 гф 24.

- •Мал. 2.1 Функціональна схема гті

- •Мал. 2.2. Часова діаграма сигналів гті

- •13 Системний контролер к 580 вк 28

- •Мал.2.4. Функцюнальнасхема ск

- •14. Програмований паралельний інтерфейс (ппі) к 580 вв 55.

- •15. Програмований контролер приорітетних переривань к530 вн59.

- •Мал. 2.9. Структурна схема пкпп вн59

- •Мал. 2.10 Каскадне з‘єднання пкпп

- •16. Режими функціонування пкп к580 вн-59

- •17. Програмування пкп вн 59 та схеми пріоритетів.

- •Використавши циклічний зсув в, маємо такий новий розподіл пріоритетів

- •17 Програмований контролер прямого доступу до пам’яті к 580 вт 57.

- •2.5.1 Загальна характеристика.*

- •2.5.2 Структурна схема контролера к580 вт 57.

- •19. Режими роботи контролера к580 вт 57.

- •20. Загальна характеристика.

- •21.Структурна схема мп.

- •26. Загальна характеристика мікроконтролерів (мк)

- •27. Структурна схема мк 8051

- •1.3. Система переривань мп вм86.

- •1.3.1. Загальна характеристика.

- •1.3.2. Зовнішні переривання.

- •1.3.3. Внутрішні та програмні переривання.

- •1.3.4. Процедура обслуговування переривань.

- •1.4 Система і формат команд мп вм86.

- •1.4.1 Формат команд.

27. Структурна схема мк 8051

має наступний вигляд і є базовою для родини MCS-51:

До складу структурної схеми входять функціональні елементи:

Р0-Р3 – паралельні порти:

Р0.7-Р0.0 – маркеровка ліній;

ПП – послідовний порт

T/C – таймери-лічильники (2)

СП – система переривань

ПЗП / РПП – резидентна пам’ять програм;

PC – лічильник команд

DPTR – регістр покажчик даних

РА – регістр адрес

SP – покажчик стеку

РК – регістр команд

СКС – схема керування синхронізацією

БК – блок керування

ГТІ – генератор тактових імпульсів

АЛП – арифметико-логічний пристрій

PSW – регістр слова стану програми

ТР/ТА – тимчасовий регістр/акумулятор

А – акумулятор

БЦП – блок центрального процесора

ОЗП/РПД – резидентна пам’ять даних

БЦП містить 8-ми розрядний АЛП, акумулятор А, регістр В, регістр слова стану програми PSW та програмно недоступні буферні регістри ТА/ТР, які використовуються для формування вхідних даних для АЛП.

ЦП виконує операції додавання, віднімання, множення, ділення, логічні операції «І», «АБО», «Виключне АБО», інверсія, операції зсуву та скидання, оперуючи такими типами даних:

булевими – 1 біт

цифровими – 4 біти

байтові – 8 біт

адресними – 16 біт

Характерною особливість МК є набір операцій з бітами: окремі біти змінних можуть бути встановленні, скинуті, інвертовані, передані, що дозволяє реалізувати операції типу «FALSE/TRUE». Акумулятор А – 8-ми розрядний, використовується як джерело одного з операндів при логічних командах, а також місцем розміщення результату виконання команд. Ряд команд вводу/виводу інформації від ЗП, команд типу TEST, INC, DEC можуть виконуватись без участі акумулятору. Регістр B використовується як акумулятор лише в множенні/діленні, де розміщений інший операнд, а також як місце розміщення результату(залишок ділення); в інших випадках – РЗП.

Регістр PSW зберігає інформацію про стан АЛП в процесі виконання програми.

Таблиця 1

Номер біта |

Позначення |

Призначення |

Доступ до біта |

7 |

CY |

Флаг переносу(Carry) |

Апаратно/програмно |

6 |

AC |

Флаг додаткового переносу(Auxiliary Carry) |

Апаратно/програмно |

5 |

F0 |

Флаг користувача |

Програмно |

4 3 |

RS 1 RS 0 |

Покажчик банку робочих регістрів: 00 – банк 0; 10 – банк 2; 01 – банк 1; 11 – банк 3 |

Програмно |

2 |

OV |

Флаг переповнення(Overflow) |

Програмно |

1 |

– |

Резервний |

Програмно |

0 |

P |

Флаг парності(Parity) |

Апаратно/програмно |

Призначення флагів CY, AC аналогічне призначенню таких же самих флагів у МП i8080, а флаг OV встановлюється при операціях додавання і віднімання, множення і ділення. При додаванні і відніманні OV=1, якщо результат перевищує ємність 7 біт і старший біт не може бути інтерпретований як знаковий; у командах ділення зазвичай флаг OV скидається, а при діленні на нуль встановлюється. У командах множення флаг OV приймає значення логічної одиниці, якщо результат перевищує 0FFH.

Флаг Р є так званим доповненням вмісту акумулятора А до парності, тобто 9-розрядне слово, що складається з 8 бітів акумулятора А і самого біта Р, завжди повинно мати парну кількість одиниць.

Регістр команд призначений для прийому вводу команд КОП з наступним декодуванням:

СКС призначено для формування керуючих сигналів згідно з кодом команд і синхронізації роботи усіх блоків МК;

Постійний запам’ятовуючий пристрій(ПЗП) або резидентна пам'ять програм(РПП) має ємність 4 кб і 16-розрядну адресну шину, що дозволяє розширити пам'ять до 64 кб за рахунок приєднання зовнішніх ВІС ПЗП. Адреса доступу до пам’яті визначається вмістом лічильника команд PC(Program Counter) або вмістом регістра-покажчика DPTR(Data Pointer Register);

DPTR використовується при непрямих переходах у програмі або при адресації таблиць, або як один 16-розрядний регістр, який може бути поділений на старшу і молодшу половини – DPH і DPL.

Розподіл адресного простору РПП має наступний вигляд, коли молодші адреси ПЗП відводяться під обробку переривань і початку роботи МК після скидання(RESET).

С – скидання

ВП – вектори переривання

ВПП – внутрішня пам’ять програми

ЗПП – зовнішня пам'ять програми

ОЗП/РПД складається з двох областей, коли:

перша область – ОЗП даних ємністю 128 біт з адресами 00-7FH

друга – регістри спеціальних функцій(SFR) з адресами 80- FFH.

Резидентна пам'ять даних має структуру:

ПАБ – пряма адресація бітів

28

Таблиця 2. Регістри спеціальних функцій

Позначення |

Найменування, адреси бітів |

Адреса |

Значення після скидання |

ACC* |

Акумулятор А

|

0E0H |

00 |

B* |

Акумулятор В

|

0F0H |

00 |

PSW* |

Слово стану програми

|

0D0H |

00 |

SP |

Регістр-вказівник стека |

81H |

07 |

DPTR |

Регістр-вказівник даних: DPH – старший байт DPL – молодший байт |

83H 82H |

00 00 |

P0* |

|

80H |

0FFH |

P1* |

Порт 1

|

90H |

0FFH |

P2* |

Порт 2

|

0A0H |

0FFH |

P3* |

Порт 3

|

0B0H |

0FFH |

IP* |

Регістр пріоритетів

|

0B8H |

xx000000B |

IE* |

Регістр маски переривань

|

0A8H |

0x000000B |

TMOD |

Регістр режиму таймера/лічильника

|

89H |

00 |

TCON* |

Регістр керування/статусу таймерів

|

88H |

00 |

TH0 |

Таймер 0(старший байт) |

8CH |

00 |

TL0 |

Таймер 0(молодший байт) |

8AH |

00 |

TH1 |

Таймер 1(старший байт) |

8DH |

00 |

TL1 |

Таймер 1(молодший байт) |

8BH |

00 |

SCON* |

Регістр керування приймачем-передавачем

|

98H |

00 |

SBUF |

Буфер приймачів-передавачів |

99H |

xx |

PCON |

Регістр керування потужністю

|

87H |

0xxxxxxx |

*Позначені регістри припускають адресацію окремих бітів.

РПД адресується 8-розрядним регістром адрес РА або SP. РА – програмно недоступний регістр, куди завантажується адреса, звернення до чарунки ОЗП під час виконання команд. Регістр SP призначений для адресації стека, що є частиною РПД, а вміст SP інкрементується при запису даних до стеку командами типу PUSH і CALL, і декрементується за командами типу POP і RET. Такий спосіб адресації елементів стеку зветься передінкрементним і постдекрементним.

У процесі ініціалізації МК після надходження сигналу RESET до SP автоматично завантажується адреса(код) 07H і це означає, що у випадку, якщо стек не буде переініціалізованим, перший байт даних у стеку буде розташований у чарунці РПД за адресою 08H.

Резидентна пам'ять даних, так само як і РПП, може бути розширена до 64 кб підключенням зовнішніх ВІС типу RAM.

Машинний цикл (МЦ), що поданий на рис. 4, має фіксовану тривалість і містить шість станів – S1-S6, кожний з яких за тривалістю відповідає одному такту (Т) і складається з двох фаз – Р1 і Р2.

Рис. 4. Часова діаграма машинного циклу (МЦ)

Порти вводу/виводу P0-P3(див. Рис.1) призначені для здійснення байтового обміну даними між МК та зовнішніми пристроями (ЗП) по 32 лініях вводу/виводу. Будь-які лінії портів можна використовувати для вводу або виводу інформації незалежно від інших ліній.

Як фізичні адреси портів в МК використовуються:

P0 – 80H, при бітовій адресації – 80H-87H;

P1 – 90H, при бітовій адресації – 90H-97H;

P2 – А0H, при бітовій адресації – А0H-А7H;

P3 – В0H, при бітовій адресації – В0H-В7H.

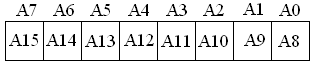

Порт Р0 є двонаправленим, реалізуючи функції вводу/виводу, а його вивід має три стани, а через порт Р0:

виводиться молодший байт адреси A7-A0 при роботі із зовнішнім ПЗП і зовнішнім ОЗП;

видається з МК та приймається в МК байт даних при роботі з зовнішньою пам’яттю;

задаються дані при програмуванні внутрішнього ПЗП типу EPROM.

Порти Р1-Р3 є квазідвонаправленими (тобто майже двонаправленими), бо оскільки у будь-який момент часу через порти можна тільки виводити інформацію, а для введення через них інформації необхідно записати до усіх розрядів їх регістрів-фіксаторів логічні одиниці.

Через порт Р1 задається молодший байт адреси при програмуванні внутрішнього ПЗП типу EPROM та при читанні внутрішнього ПЗП.

Через порт Р2:

виводиться старший байт адреси А15-А8 при роботі із зовнішнім ПЗП і зовнішнім ОЗП у тих випадках, коли адреса є 16-розрядною;

задається старший байт А15-А8 адреси при програмуванні внутрішнього ПЗП типу EPROM та при читанні внутрішнього ПЗП.

Порт Р3 може використовуватися як для вводу/виводу інформації, так і для реалізації альтернативних функцій обміну інформацією згідно з табл. 3.

Кожну з восьми ліній порту Р3 користувач може запрограмувати на виконання альтернативних функцій записом одиниці у відповідні біти регістра-замка (Р3.0-Р3.7) порту Р3.

Таблиця 3. Альтернативні функції порту Р3

Біт |

Позиція |

Альтернативна функція обміну інформацією |

RxD |

P3.0 |

Вхід приймача послідовного порту в режимах 1-3. Введення/виведення послідовних даних у режимі регістра зсуву. |

TxD |

P3.1 |

Вихід передавача послідовного порту в режимах 1-3. Вихід синхронізації при роботі послідовного порту в режимі 0. |

INT0 |

P3.2 |

Вхід запиту переривання 0. Сприймання сигналів низького рівня або зріз сигналу. |

INT1 |

P3.3 |

Вхід запиту переривання 1. Сприймання сигналів низького рівня або зріз сигналу. |

T0 |

P3.4 |

Вхід таймера/лічильника 0 або тестовий вхід 0. |

T1 |

P3.5 |

Вхід таймера/лічильника 1 або тестовий вхід 1. |

WR |

P3.6 |

Запис. Апаратне формування активного сигналу низького рівня у разі звернення до зовнішньої пам’яті даних. |

RD |

P3.7 |

Читання. Активний сигнал низького рівня формується апаратно у разі звернення до зовнішньої пам’яті даних. |

Послідовний порт (див. Рис. 1) призначений для забезпечення послідовного обміну даними між МК і зовнішнім пристроєм (ЗП), для реалізації циклічного зсуву даних, а також для використання як універсального асинхронно-синхронного прийомо-передавача із фіксованою або змінною швидкістю обміну і з можливістю двостороннього обміну даними (так званий дуплексний режим). Послідовний порт може працювати в одному з чотирьох режимів (0-3), програмуючись на один з них записом керуючого слова (КС) до регістру керування SCON(Serial Port Control).

Блок таймерів/лічильників призначений для підрахунку зовнішніх подій (функція лічильника), реалізації програмно-керованих затримок та виконання функцій завдання часу (функція таймера).

До складу блока таймерів/лічильників входять:

два 16-розрядні регістри T/C0 та T/C1;

8-розрядний регістр режимів TMOD;

8-розрядний регістр керування TCON;

схема інкременту;

схема фіксації сигналів INT0, INT1, T0 і T1;

схема керування флагами;

логіка керування Т/С.

Система переривань призначена для реагування на зовнішні та внутрішні події. При цьому до:

зовнішніх подій належать появи нульових активних рівнів сигналів на входах INT0 та INT1;

внутрішніх подій належать переповнення таймерів та завершення послідовного обміну. Зовнішні або внутрішні події викликають встановлення відповідних флагів: IE0, IE1, TF0, TF1, RI та TI, що й спричиняють переривання.

Усі ці флаги можуть бути програмно встановлені або скинуті, при цьому їх програмне встановлення викликає переривання так само, як і реагування на подію.

Отже, переривання можуть програмно викликатися або програмно усуватися. Крім того переривання на входах INT0, INT1 можуть викликатися програмним скиданням бітів Р3.2 і Р3.3 порту Р3. Керування системою переривання здійснюється записом керуючих слів (КС) до регістрів TCON блоку таймерів/лічильників, а також до регістрів ІЕ та ІР.

Регістр дозволу переривань ІЕ призначений для дозволу або заборони переривань від відповідних джерел.

Регістр пріоритетів переривань ІР призначений для встановлення рівня пріоритету переривання для кожного з п’яти джерел переривань.

29

Микроконтроллер типа i8051 работает с данными битового и байтового формата. При обработке данных можно обращаться не только к байтам во всех ЗУ, но и к отдельным битам функциональных регистров или части адресного пространства внутреннего ОЗУ. Есть несколько команд, работающих с данными двухбайтового формата. Часть команд обрабатывает каждый из битов байтовых операндов независимо от информации, содержащейся в других битах. Другая часть команд работает с байтами как с положительными целыми числами. Всего в МК 111 команд, разделённых на 5 групп: 1)команды передачи 2)команды арифметических операций 3)команды логических операций 4)команды передачи управления 5)команды операции с битами. При наличии отдельно адресуемых битов в пространстве ОЗУ, говорят, что в МК серии i8051 имеется встроенный булевский процессор.

В командах обработки информации могут указываться один или два операнда. При явном использовании двух операндов один из них называется источником (source), а второй приемником (destination). Следует обратить внимание на то, что в поле операндов первым записывается обозначение приемника, а вторым - источника. При работе с одним операндом производится чтение операнда, его проверка или изменение и (при необходимости) запись. При работе с двумя операндами производится чтение источника и (при необходимости) приемника, вычисление и (при необходимости) запись результата по адресу приемника. Слова "при необходимости" означают, что необходимость действия определяется типом команды. После выполнения команды обработки информации содержимое слова состояния процессора может измениться в зависимости от результата вычислений. В описаниях команд, которые не осуществляют непосредственную запись в этот регистр, приводятся сведения о влиянии результата выполнения на содержимое отдельных битов PSW.

Время выполнения каждой команды различное: в большинстве от 1 до 2 командных циклов, команды расширенной арифметики – за 4 командных цикла.

Режимы адресации:

1)Непосредственная. Данные содержатся непосредственно в команде: mov A,#12;

Для символического обозначения непосредственной адресации в источнике используются символ # и числовое выражение, по которому транслятор вычисляет и записывает в машинный код команды нужную константу. Допустимое десятичное значение константы от 0 до 255 для байтового формата и от 0 до 65535 для двухбайтового. В качестве непосредственного операнда можно записывать числа в десятичной, шестнадцатеричной, восьмеричной или двоичной системах счисления с суффиксами d, h, о(q) или b соответственно. По умолчанию транслятор считает число десятичным. Непосредственная адресация удобна тем, что не нужно тратить дополнительное время на чтение операнда, так как он хранится в команде. Увеличение размера машинной команды не столь важно, так как константу все равно нужно где-то хранить.

2)Регистровая. Данные содержаться в одном из регистре общего назначения: mov R0, A;

Для символического обозначения регистровой адресации используется имя любого из восьми регистров общего назначения. При регистровой адресации содержимое регистра обрабатывается как данные. Номер регистра общего назначения указывается в коде операции, вследствие чего для регистровой адресации не требуется увеличивать размер машинной команды. По этой причине регистровая адресация обоих операндов не допускается. Она чаще всего применяется для временного хранения промежуточных результатов вычислений и удобна тем, что на чтение из регистра и на запись в него не тратится дополнительное время.

3)Прямая: mov DPTR, #1234h;

Для символического обозначения прямой адресации используется имя операнда. В качестве такового можно записать имя какого-либо функционального регистра или имя данных, указанное в поле метки при резервировании адресного пространства ОЗУ. По этому имени транслятор вычисляет фактическое значение адреса и подставляет его в машинный код команды.

4)Косвенная: mov A,@R0;

Для обозначения косвенной адресации используется символ @, за которым следует выражение с именем регистра. При косвенной адресации содержимое регистра используется не в качестве данных, а в качестве адреса данных, то есть указателя на данные. Для косвенной адресации могут использоваться только R0 и R1 или регистр указателя данных DPTR.

5)Индексная: mov A, @R0+DPTR

Используется сумма содержимого накопителя с содержимым программного счетчика или регистра указателя. Индексная адресация используется только для чтения из ПЗУ. Записывается как @А+ с последующим именем используемого регистра PC или DPTR.

6)Стековая: push Acc;

Аналогична косвенной в том смысле, что адрес для обращения к ОЗУ берется из регистра SP. Отличие состоит в том, что перед записью в ОЗУ содержимое указателя стека увеличивается на 1, а после, а после чтения из ОЗУ – уменьшается на 1.

Команди пересилки

Несмотря на пересылку данных в неизменном виде, эти команды осуществляют один из способов обработки информации. В качестве примера такой обработки можно привести сортировку. В командах пересылки используется все разнообразие способов адресации данных. Пересылка данных может осуществляться в форматах байта, половины байта, двух байтов и бита.

Начнем с байтового формата. Команда MOV копирует содержимое источника (src) в приемник (dst) (при выполнении этой команды первоначальное содержимое приемника теряется).

MOV A,#src; MOV A,Rn; MOV A,@Ri; MOV A,src; MOV Rn,A; MOV Rn,#src; MOV Rn,src; MOV @Ri,A;

MOV @Ri,#src; MOV Ri,src; MOV dst,A; MOV dst,#src; MOV dst,Rn; MOV dst,@Ri; MOV dst,dst.

Для засылки нуля в накопитель проще использовать команду очистки: CLR А.

Чтение и запись данных байтового формата при обращении к внешнему ОЗУ осуществляется при помощи команд MOVX, где буква X, по-видимому, означает external (внешняя память):

MOVX A,@Ri; MOVX A,@DPTR; MOVX @Ri,А; MOVX @DPTR, А.

Перед выполнением этой команды в соответствующий регистр нужно записать адрес. Чтение данных из ПЗУ осуществляется при помощи команды MOVC;.

MOVC A,@A+DPTR; MOVC A,@A+PC.

Эти команды очень удобны для чтения из таблиц, записываемых в ПЗУ. Запись в ОЗУ и чтение из него при помощи стекового способа адресации производятся командами: push src; POP dst.

Мнемокоды стековых команд соответствуют английским глаголам «затолкнуть» и «вытолкнуть».

Существует еще одна команда копирования ХСН (eXCHange означает «обменять»), которая осуществляет обмен содержимого источника и приемника. В принципе обмен можно произвести при помощи трех команд пересылки. Следующие команды делают это за то же время, но занимают меньше места в ПЗУ и не требуют использования дополнительной ячейки ОЗУ: ХСН А,Rn; ХСН A,@Ri; ХСН A,src.

Есть также команда, обменивающая младшие половины байтов: XCHD A, Ri.

Здесь D означает Digit (четыре бита используются для двоичного представления десятичной цифры).

Одна из команд пересылки данных записывает два байта в регистр указателя данных: MOV DPTR,#src.

Других команд для явной пересылки двухбайтовых данных нет. Несколько команд пересылки информации работают в битовом формате. В команде MOV источником или приемником должен быть бит переноса С: MOV С,flag; MOV flag,С.

Все команды пересылки не влияют на содержимое слова состояния программы PSW, за исключением случаев пересылки информации в этот регистр или один из его битов.

Арифметичні команди

В арифметических операциях нужно придерживаться строго определенных правил записи данных в соответствии с порядковыми номерами разрядов двоичного кода. В связи с ограниченными ресурсами микроконтроллера в нём используются только четыре арифметических операции с целыми числами (+, -, *, /). Отступления от правил кодирования приводят к неправильному выполнению арифметических операций.

В одном байте может быть закодировано 256 значений целого числа. При работе с положительными числами это соответствует значениям от 0 до 255. Все команды арифметических операций предназначены для работы с положительными целыми числами байтового формата, хотя команды сложения и вычитания в случае отсутствия переполнения обеспечивают получение корректного результата при специальном способе кодирования отрицательных чисел. Кодирование чисел более подробно рассмотрено в главе о программировании арифметических операций. При необходимости работы с числами, которые не могут быть представлены в байтовом формате, необходимо разрабатывать соответствующие подпрограммы. Выполнение операций умножения и деления с числами, имеющими произвольный знак, возможно при их представлении через знак и модуль и использовании соответствующих подпрограмм. Это могут быть собственные разработки или заимствования из хорошо проверенных библиотек других разработчиков.

Команда сложения работает с данными байтового формата, притом в качестве приемника всегда используется только накопитель:

ADD A,#src; ADD A,Rn; ADD A,@Ri; ADD A,src.

Для работы с числами, которые не могут быть представлены одним байтом, используется команда сложения, учитывающая перенос, полученный при сложении предыдущей пары байтов:

ADDC A,#src; ADDC A,Rn; ADDC A,@Ri, ADDC A, src.

Добавление буквы С к обозначению команды указывает на использование бита переноса. Существует также команда сложения, при помощи которой производится увеличение заданного операнда на единицу:

INC А; INC Rn; INC @Ri; INC src

Такая же команда есть и для работы с двумя байтами содержимого регистра указателя данных:INC DPTR. При помощи этой команды можно изменять содержимое указателя для чтения последовательности байтов из ПЗУ. При сложении чисел, представленных двоично-десятичными кодами, после операции сложения нужно использовать команду десятичной коррекции суммы DA А. Двоично-десятичное кодирование имеет весьма ограниченное применение и потому далее не рассматривается.

Набор команд для вычитания гораздо уже. Команда вычисления разности существует только в варианте с вычитанием содержимого бита переноса:

SUBB A,#src; SUBB A,Rn; SUBB A,@Ri; SUBB A,src/

Перед вычислением разности младших байтов нужно обязательно очищать бит переноса, если нет уверенности в его содержимом. При вычислении разности старших байтов этого делать не нужно.

Существует также команда вычитания, при помощи которой производится уменьшение заданного операнда на единицу: DEC A; DEC Rn; DEC src; DEC @Ri.

Команды уменьшения для работы с двухбайтовым форматом данных нет.

Результаты выполнения команд сложения и вычитания влияют на содержимое битов переноса, дополнительного переноса и переполнения в слове состояния программы. Результаты выполнения команд увеличения и уменьшения не влияют на содержимое слова состояния программы.

Команда умножения и деления работают при записи операндов в накопитель (A) и регистр В. Для команды умножения порядок записи сомножителей в эти регистры не важен. MUL АВ

Произведение имеет двухбайтовый формат. Младший байт произведения записывается в накопитель, а старший - в регистр В.

Для команды деления делимое должно быть записано в накопитель, а делитель - в регистр В: DIV АВ

После выполнения команды в накопителе находится частное, а в регистре В - остаток. После выполнения команд умножения и деления в бит переноса заносится 0. Если старший байт произведения не равен нулю, то в байт переполнения заносится 1. При делении на 0 в байт переполнения также заносится 1.

**************************