- •1.Понятие двоичной функции и ее свойства

- •III. Инверсия(операция лог. Отрицания)[Не]

- •3.Понятие логических операций “не-и”, “не-или”, “исключающее или” и их таблицы истинности.

- •4.Основные законы булевой алгебры и их назначение.

- •5. Законы булевой алгебры, определяющие действия с константами 0 и 1 и их назначение

- •6.Понятие комбинационной схемы

- •7. Понятие сднф двоичной функции и принцип получения формы сднф

- •8.Понятие скнф двоичной функции и принцип получения формы скнф

- •9.Назначение карты Карно и ее вид для двух переменных

- •11.Принцип построения карты Карно

- •12.Понятие мднф и мкнф переключающей функции

- •25.Понятие триггеров. Классификация триггеров

- •26.Rs триггер

- •28.T триггер

- •29.D триггер

- •30.Jk триггер

- •31.Понятие шифратора ,его графическое представление в схеме

- •33.Понятие приоритетного шифратора и его графическое представление в схеме

- •34.Понятие дешифратора и его графическое представление в схеме

- •37.Понятие мультиплексора и его графическое представление в схеме

- •38.Понятие демультиплексора и его графическое представление в схеме

- •39.Компораторы кодов и их графическое представление в схеме

- •40.Понятие полусумматора и его графическое представление в схеме

- •41.Сумматор и его графическое представление в схеме

- •43.Понятие полувычитателя и его графическое представление в схеме

- •45.Многоразрядный параллельный вычитатель и его функциональная схема

- •46.Последовательный сумматор и его функциональная схема

- •47.Понятие счетчика, его назначение, типы счетчиков

- •50.Синхронный счетчик и его функциональная схема

- •51.Реверсивный счетчик, его графическое представление

- •52.Делитель частоты. Представление его функциональной схемы

- •54.Понятие регистров, назначение регистров, типы регистров

- •55.Параллельные регистры, назначение, их типы, схема

- •57.Регистры сдвига,назначение,их типы

- •58.Последовательные регистры сдвига, назначение, функциональная схема

- •59.Параллельный регистр сдвига, назначение, функциональная схема

- •Структурная схема 4-разрядного параллельного кольцевого регистра

40.Понятие полусумматора и его графическое представление в схеме

Полусумматор — логическая схема имеющая два входа и два выхода. Полусумматор используется для построения двоичных сумматоров. Полусумматор позволяет вычислять сумму A+B, где A и B — это разряды двоичного числа, при этом результатом будут два бита S,C, где S — это бит суммы, а C — бит переноса. Однако, как можно заметить, для построения схемы двоичного сумматора необходимо иметь элемент, который суммирует три бита A,B и C, где C — бит переноса из предыдущего разряда, таким элементом является полный двоичный сумматор, который как правило состоит из двух полусумматоров.

41.Сумматор и его графическое представление в схеме

Сумматор — логический операционный узел, выполняющий арифметическое сложение двоичных, троичных или n-ичных кодов двух (бинарный), трёх (тринарный) или n чисел (n-нарный). При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Сумматоры являются комбинационными схемами, выполняющими бинарную (двухоперандные), тринарную (трёхоперандные) или n-арную (n-операндную) логическую функцию сложения. Входят в состав узлов арифметическо-логических устройств (АЛУ).

43.Понятие полувычитателя и его графическое представление в схеме

Сумматоры и вычитатели очень похожи друг на друга, и, кроме того, полувычитатели и полные вычитатели используются аналогично полусумматорам и полным сумматорам.

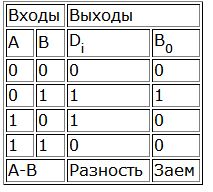

В вычитается из А (А и В - входные сигналы), результат (разность) появляется на выходе Di. Если В больше А (как в строке 2 таблицы), нужно занять 1 в соседнем старшем разряде. Сигнал заема указан в столбце В0. Условное графическое обозначение полувычитателя показано на рис. 15.1.

Рис. 15.1. Полувычитатель. а - условное графическое обозначение, б – схема

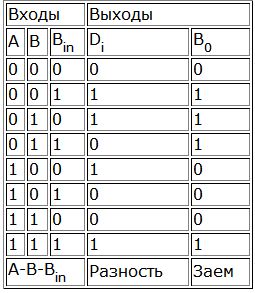

При вычитании многоразрядных двоичных чисел нужно принимать во внимание заем "единиц" в более старших разрядах. Таблица истинности, содержащая всевозможные комбинации, которые могут возникнуть при вычитании двоичных чисел, показана ниже.

Вычитанию в разряде двоек соответствует строка 3, в разряде четверок - строка 6, в разряде восьмерок - строка 3, в разряде с весом 16 - строка 2 и в разряде с весом 32 - строка 6 таблицы истинности. Условное графическое обозначение полного вычитателя показано на рис. 15.2.

Рис. 15.2. Полный вычитатель. а - условное графическое обозначение, б - принципиальная схема

45.Многоразрядный параллельный вычитатель и его функциональная схема

Соединяя друг с другом полувычитатели и полные вычитатели, получают устройства, называемые параллельными вычитателями.

На рис. 16.1 представлена структурная схема, полученная путем объединения одного полувычитателя и трех полных вычитателей. Это схема 4-разрядного параллельного вычитателя, который выполняет операцию вычитания двоичного числа В3В2В1В0 из двоичного числа А3А2А1А0. Обратите внимание, что верхний (на схеме) вычитатель (полувычитатель) осуществляет вычитание в разряде единиц (СМР). Выход В0 этого вычитателя связан с вычитателем разряда двоек. Вообще выход заема В0 каждого вычитателя связан со входом заема Вin вычитателя соседнего старшего разряда. Эти линии связи "следят" за заемами в процессе вычитания двоичных чисел.

Рис. 16.1. 4-разрядный параллельный вычитатель