- •1.Понятие двоичной функции и ее свойства

- •III. Инверсия(операция лог. Отрицания)[Не]

- •3.Понятие логических операций “не-и”, “не-или”, “исключающее или” и их таблицы истинности.

- •4.Основные законы булевой алгебры и их назначение.

- •5. Законы булевой алгебры, определяющие действия с константами 0 и 1 и их назначение

- •6.Понятие комбинационной схемы

- •7. Понятие сднф двоичной функции и принцип получения формы сднф

- •8.Понятие скнф двоичной функции и принцип получения формы скнф

- •9.Назначение карты Карно и ее вид для двух переменных

- •11.Принцип построения карты Карно

- •12.Понятие мднф и мкнф переключающей функции

- •25.Понятие триггеров. Классификация триггеров

- •26.Rs триггер

- •28.T триггер

- •29.D триггер

- •30.Jk триггер

- •31.Понятие шифратора ,его графическое представление в схеме

- •33.Понятие приоритетного шифратора и его графическое представление в схеме

- •34.Понятие дешифратора и его графическое представление в схеме

- •37.Понятие мультиплексора и его графическое представление в схеме

- •38.Понятие демультиплексора и его графическое представление в схеме

- •39.Компораторы кодов и их графическое представление в схеме

- •40.Понятие полусумматора и его графическое представление в схеме

- •41.Сумматор и его графическое представление в схеме

- •43.Понятие полувычитателя и его графическое представление в схеме

- •45.Многоразрядный параллельный вычитатель и его функциональная схема

- •46.Последовательный сумматор и его функциональная схема

- •47.Понятие счетчика, его назначение, типы счетчиков

- •50.Синхронный счетчик и его функциональная схема

- •51.Реверсивный счетчик, его графическое представление

- •52.Делитель частоты. Представление его функциональной схемы

- •54.Понятие регистров, назначение регистров, типы регистров

- •55.Параллельные регистры, назначение, их типы, схема

- •57.Регистры сдвига,назначение,их типы

- •58.Последовательные регистры сдвига, назначение, функциональная схема

- •59.Параллельный регистр сдвига, назначение, функциональная схема

- •Структурная схема 4-разрядного параллельного кольцевого регистра

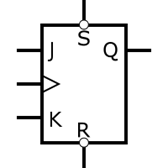

30.Jk триггер

JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы Jи K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К.

J |

K |

Q(t) |

Q(t+1) |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

31.Понятие шифратора ,его графическое представление в схеме

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) - преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

n=2m, где n- число входов,m- число выходов двоичных разрядов.

Троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного (одноединичного или однонулевого) кода в троичный. При подаче сигнала ("1" в одноединичном коде или "0" в однонулевом коде) на один из n входов на выходе появляется троичный код номера активного входа.

Число входов и выходов в полном троичном шифраторе связано соотношением:

n=3m, где n- число входов,m- число выходов троичных разрядов.

33.Понятие приоритетного шифратора и его графическое представление в схеме

Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

приоритетный шифратор (рис. 99). Она имеет восемь информационных входов 0-7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1,2,4; G -признака подачи входного сигнала и Р - переноса.

Если на всех информационных входах микросхемы лог. 1, на выходах 1,2,4, G - лог. 1, на выходе Р - лог. 0. При подаче лог. 0 на любой из информационных входов 0-7 на выходах 1,2, 4 появится инверсный код, соответствующий номеру входа, на который подан лог. 0, на выходе G'- лог. 0, что

является признаком подачи входного сигнала, на выходе Р - лог. 1, которая запрещает работу других микросхем ИВ1 при их каскадном соединении. Если лог. 0 будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером.

Так работает микросхема при подаче на вход Е лог. 0. Если же на входе Е лог. 1 (запрет работы), на всех шести выходах микросхемы лог. 1.